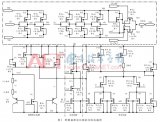

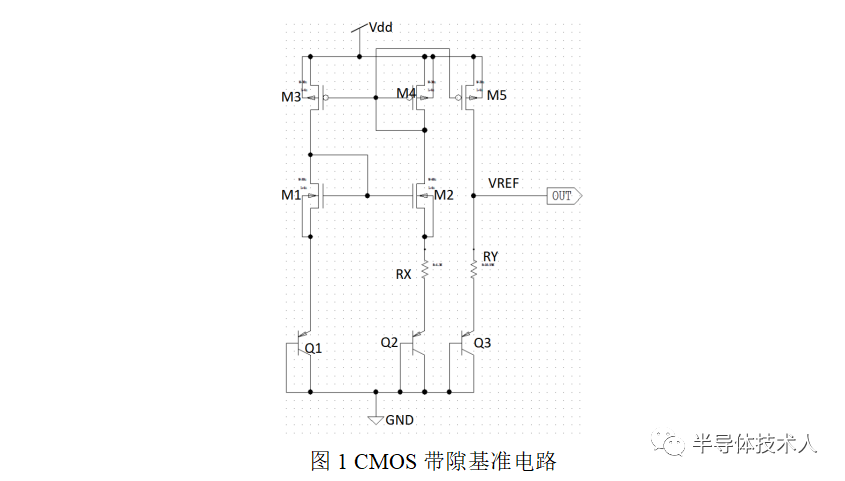

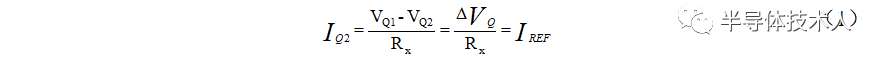

帶隙基準電壓源核心電路

- 電源電路(64055)

- 基準電壓源(20477)

相關推薦

如何減小cmos帶隙基準溫度系數工藝角的影響?

、速度快等優點,在眾多電子設備中應用廣泛。其中,基準電壓就是一個比較重要的參數,而基準電壓的溫度系數是指在不同溫度下電路帶來的基準電壓變化情況。 通常來說,CMOS電路中使用的帶隙基準技術,具有多晶硅、硅谷能帶、亞穩態等技術,但是這些技術都存在著一定的溫度漂移問題。而在實際

2023-10-23 10:29:11 24

24

24

24為什么要用基準電壓源?如何選擇基準電壓源?基準電壓源怎么選型號?

電壓源,而是使用何種基準電壓源。 基準電壓源只是一個電路或電路元件,只要電路需要,它就能提供已知電位。基準電壓源主要有兩類:分流和串聯。基準電壓源只是一個電路或電路元件,只要電路需要,它就能提供已知電位。這可能是幾分鐘、幾小時或幾年。

2023-07-17 11:40:00 699

699

699

699

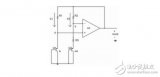

用于基準電壓產生的啟動電路設計

下拉晶體管源極輸出端即為啟動電路的啟動節點,該啟動節點連接帶隙基準電路的PMOS電流鏡柵極,啟動電路工作時將帶隙基準電路中的PMOS電流鏡柵極電平拉低,為三極管充電。用于啟動帶隙基準電路,使帶隙基準電路脫離錯誤工作狀態。

2023-07-06 16:05:43 944

944

944

944

帶你認識帶隙基準電路

與溫度關系很小的電壓或者電流基準,在實際電路設計中具有重要的應用,比如在電流鏡結構中,需要對一“理想的”基準電流進行精確復制,這一“理想的”基準電流,一般由帶隙基準電路產生。

2023-07-06 11:32:14 799

799

799

799

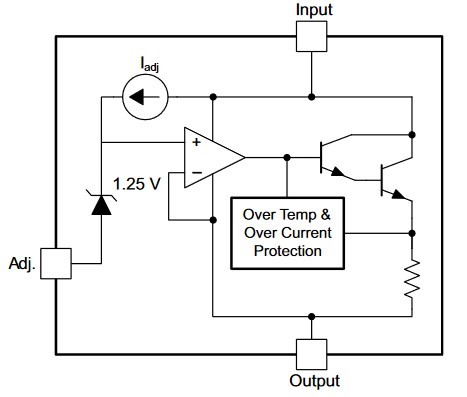

基于LDO穩壓器的帶隙基準電壓源設計

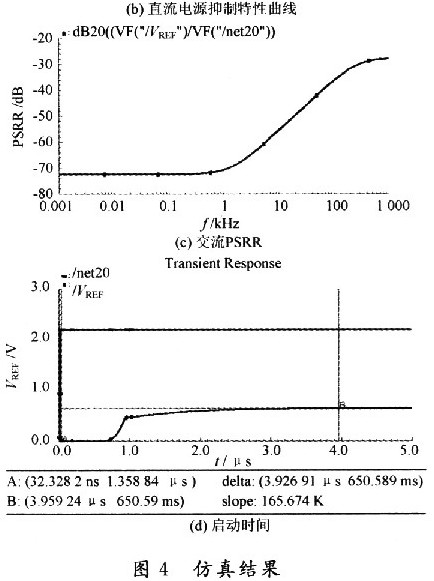

一種結構簡單的基于LDO穩壓器的帶隙基準電壓源,以BrokaW帶隙基準電壓源結構為基礎來進行設計。采用Cadence的Spectre仿真工具對電路進行了完整模擬仿真,-20~125℃溫度范圍內,基準

2018-10-09 14:42:54

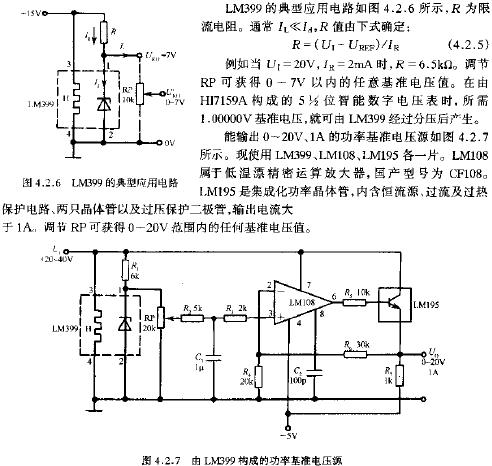

高精度基準電壓源工作原理介紹

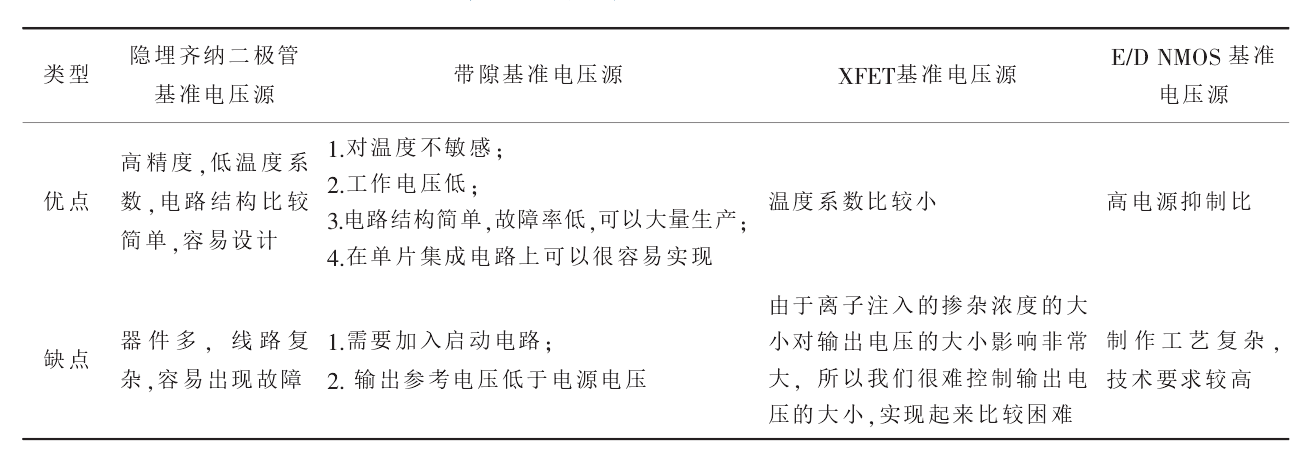

壞就是整個電路性能的好壞。主要有以下4種:隱埋齊納二極管基準電壓源、帶隙基準電壓源、XFET基準電壓源和E/DNMOS基準電壓源。

2022-02-24 14:15:06 2739

2739

2739

2739

高精度基準電壓源的工作原理介紹

壞就是整個電路性能的好壞。主要有以下4種:隱埋齊納二極管基準電壓源、帶隙基準電壓源、XFET基準電壓源和E/DNMOS基準電壓源。 高精度基準電壓源是從實際電源抽象出來的一種模型,在其兩端總能保持一定的電壓而不論流過的電流為

2022-01-20 16:52:17 1089

1089

1089

1089

如何設計一個LDO帶隙基準的電壓源

本論文設計的帶隙基準電壓源電路是LDO電源管理芯片的一個核心電路之一,蒂隙基準電路在DC-DC,A/D(模/數),D/A(數/模)等集成電路中都有廣泛的應用。LDO穩壓器因其超低壓差,以及成熟

2019-12-04 16:36:41 13

13

13

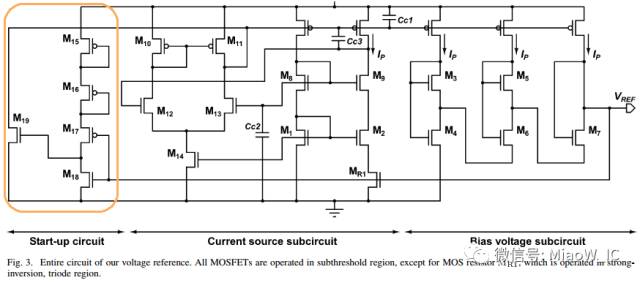

13關于一種低溫漂高電源抑制比帶隙基準源的設計

通過一階、二階、高階以及分段等方式進行補償,來提高基準源的精度[1]。本文基于一階補償后的基準電壓輸出特性,設計一個高低溫分段補償電路,帶隙基準源在寬的溫度范圍具有較低的溫度系數。同時,該補償方式還可以用于其他類似輸出特性的電路中,用以提高基準精度。

2018-06-26 08:06:00 6017

6017

6017

6017

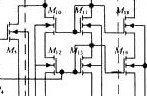

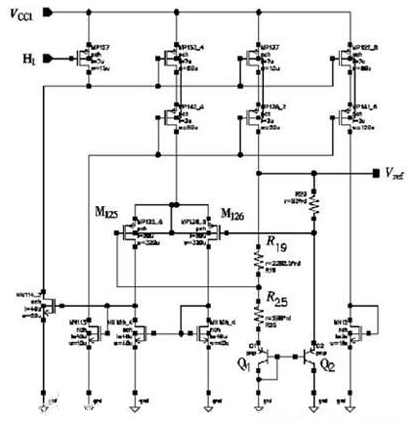

一種用于高精度DAC的實用型CMOS帶隙基準源

本文根據基準源的精度必須好于DAC設計精度指標。利用負反饋和基本電流鏡等原理,合理設計電路的情況下得到了穩定的PTAT電流,并根據帶隙基準電壓源的設計原理得到一個高精度和快速啟動的CMOS帶隙基準

2018-03-05 10:45:23 7915

7915

7915

7915

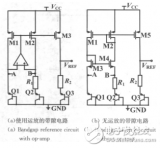

帶隙基準源電路的基本原理及仿真分析

模擬電路中廣泛地包含電壓基準(reference voltage)和電流基準(current reference)。在數/模轉換器、模/數轉換器等電路中,基準電壓的精度直接決定著這些電路的性能。這種

2017-12-07 09:26:01 25210

25210

25210

25210

帶隙基準電路的基本原理電路核心以及誤差源和抑制比的分析

近年來,由于集成電路的飛速發展,基準電壓源在模擬集成電路、數模混合電路以及系統集成芯片(SOC)中都有著非常廣泛的應用,對高新模擬電子技術的應用和發展也起著至關重要的作用,其精度和穩定性會直接影響整個系統的性能。因此,設計一個好的基準源具有十分現實的意義。

2017-12-04 05:41:01 17949

17949

17949

17949

cmos帶隙基準電壓源設計

帶隙是導帶的最低點和價帶的最高點的能量之差。也稱能隙。帶隙越大,電子由價帶被激發到導帶越難,本征載流子濃度就越低,電導率也就越低帶隙主要作為帶隙基準的簡稱,帶隙基準是所有基準電壓中最受歡迎的一種

2017-11-24 15:45:20 21469

21469

21469

21469

一種用于D/A轉換電路的帶隙基準電壓源的設計

基準電壓源在DAC電路中占有舉足輕重的地位,其設計的好壞直接影響著DAC輸出的精度和穩定性。而溫度的變化、電源電壓的波動和制造工藝的偏差都會影響基準電壓的特性。本文針對如何設計一個低溫度系數和高電源電壓抑制比的基準電壓源作了詳細分析。

2017-11-24 11:53:32 2583

2583

2583

2583

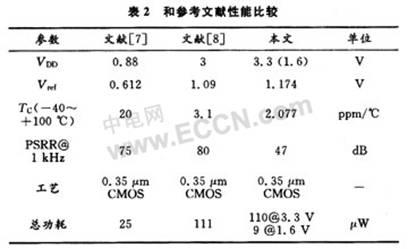

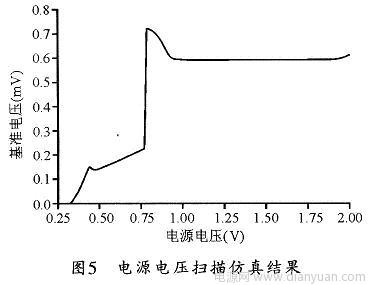

基于CMOS工藝設計低溫漂高PSRR帶隙基準源

基準源廣泛應用于模擬和混合集成電路設計中,例如數據轉換器、PWM 控制器、振蕩器、運放和PLL 等。隨著電路越來越復雜、性能要求越來越高,高精度基準源已經成為很多模塊的關鍵部分。傳統的帶隙基準由具有

2017-10-31 10:31:24 11

11

11

11帶隙基準電壓源及過溫保護電路

介紹了一種低溫漂的BiCMOS帶隙基準電壓源及過溫保護電路。采用Brokaw帶隙基準核結構,通過二階曲率補償技術,設計的熱滯回差很好地防止了熱振蕩現象。

2017-09-07 20:15:25 23

23

23

23一種發動機高溫差環境下的基準電壓源電路

根據汽車發動機控制芯片的工作環境,針對常見的溫度失效問題,提出了一種應用在發動機控制芯片中的帶隙基準電壓源電路。該電路采用0.18 m CMOS工藝,采用電流型帶隙基準電壓源結構

2013-09-26 17:06:12 33

33

33

33一種高電源抑制比的CMOS帶隙基準電壓源設計

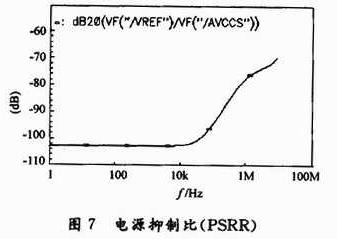

介紹一種基于CSMC0.5 m工藝的低溫漂高電源抑制比帶隙基準電路。本文在原有Banba帶隙基準電路的基礎上,通過采用共源共柵電流鏡結構和引入負反饋環路的方法,大大提高了整體電路的

2013-05-27 16:29:08 71

71

71

71用于音頻AD轉換器的CMOS帶隙電壓基準源

在傳統帶隙基準電壓源電路結構的基礎上,通過在運放中引入增益提高級,實現了一種用于音頻-A/D轉換器的CMOS帶隙電壓基準源。在一階溫度補償下實現了較高的電源抑制比(PSRR)和較

2012-10-10 14:49:50 43

43

43

43帶隙電壓基準源的設計與分析

本文介紹了基準源的發展和基本工作原理以及目前較為常用的帶隙基準源電路結構。設計了一種基于Banba結構的基準源電路,重點對自啟動電路及放大電路部分進行了分析...

2012-05-24 15:18:29 79

79

79

79一種高精度帶隙基準源

在傳統正溫度系數電流基礎上,增加兩種不同材料的電阻以實現帶隙基準的二階溫度補償,采用具有反饋偏置的折疊共源共柵運算放大器,使得所設計的帶隙基準電路,具有較高的精度和溫度

2012-02-13 15:31:13 54

54

54

54低溫漂CMOS帶隙基準電壓源分析

帶隙基準電壓源的目的是產生一個對溫度變化保持恒定的量,由于雙極型晶體管的基極電壓VBE,其溫度系數在室溫(300 K)時大約為-2.2 mV/K

2011-11-23 09:19:32 2963

2963

2963

2963

低功耗CMOS電壓基準源的設計

傳統的帶隙電壓基準源面積大、功耗大、不適應低功耗小面積的要求。本文立足于低功耗、小面積、利用工作于弱反型區晶體管的特點,對傳統的帶隙電壓基準源做出改進,設計了一款

2011-10-09 11:22:04 1613

1613

1613

1613

CMOS帶隙基準電壓源中的曲率校正方法

基準電壓源是集成電路系統中一個非常重要的構成單元。結合近年來的設計經驗,首先給出了帶隙基準源曲率產生的主要原因,而后介紹了在高性能CMOS 帶隙基準電壓源中所廣泛采用的幾種

2011-09-27 14:30:52 58

58

58

58一種高PSR帶隙基準源的實現

文針對傳統基準電壓的低PSR以及低輸出電壓的問題,通過采用LDO與帶隙基準的混合設計,并且采用BCD工藝,得到了一種可以輸出較高參考電壓的高PSR(電源抑制)帶隙基準。

2011-08-23 10:28:08 2388

2388

2388

2388

一種帶隙基準電壓源的設計與仿真

設計了一款帶隙基準電壓源,在LTspice下畫出原理圖,產生網表后,在Hspice下仿真,結果表明,溫度系數為9.14×10-16℃,電源電壓在3~5 V之間變化時,基準電壓在43 mV以內變化,滿足設計

2011-08-19 11:12:08 2455

2455

2455

2455基于N型工藝的基準電壓源設計

設計了一種可以集成于只有N型有源器件和無源元件工藝中的 基準電壓源 產生電路。為只存在N型MOS或者NPN型晶體管、沒有P型器件、難以用傳統的帶隙電壓源結構來產生精確參考電壓的

2011-08-15 11:02:42 30

30

30

30帶隙基準計算器(BGRC)功能

帶隙基準計算器(BGRC)是一個帶隙基準電路的設計和分析。所有的電路參數和輸出電壓的計算結溫的功能。惠普? 50G計算器或免費的PC模擬器,可以使用計算器

2011-08-10 10:13:33 1918

1918

1918

1918

CMOS帶隙基準電壓源曲率校正方法

基準電壓源是集成電路系統中一個非常重要的構成單元。結合近年來的設計經驗,首先給出了帶隙基準源曲率產生的主要原因,而后介紹了在高性能CMOS 帶隙基準電壓源中所廣泛采用的幾種

2011-05-25 14:52:44 34

34

34

34新型電流模式曲率補償帶隙基準源設計

本文提出了一種新穎的曲率補償帶隙基準結構。通過3個具有不同溫度依賴性質的電流的適當疊加,從而產生一個具有極低溫度系數的參考電壓。

2011-05-09 09:20:47 1476

1476

1476

1476

基于汽車環境的帶隙基準電壓源的設計

比較了傳統帶運算放大器的帶隙基準電壓源電路與采用曲率補償技術的改進電路,設計了一種適合汽車電子使用的帶隙基準電壓源,該設計電路基于上海貝嶺2 μm 40 V bipolar工藝,采

2010-12-22 17:22:15 22

22

22

22新型BiCMOS帶隙基準電路的設計

在模擬及數/模混合集成電路設計中,電壓基準是非常重要的電路模塊之一,而通過巧妙設計的帶隙電壓基準更是以其與電源電壓、工藝、溫度變化幾乎無關的特點,廣泛應用

2010-11-02 09:40:44 1619

1619

1619

1619

一種高電源抑制比帶隙基準電壓源的設計

摘要:采用共源共柵運算放大器作為驅動,設計了一種高電源抑制比和低溫度系數的帶隙基準電壓源電路,并在TSMC0.18Um CMOS工藝下,采用HSPICE進行了仿真.仿真結果表明:在-25耀115益

2010-10-18 01:17:25 56

56

56

56高精度CMOS帶隙基準源的設計

引言

模擬電路中廣泛地包含電壓基準(reference voltage)和電流基準(current reference)。在數/模轉換器、模/數轉換器等電路中,基準電壓的精度直接決定著這些電路的

2010-09-30 10:11:55 3517

3517

3517

3517

一種高精度BiCMOS帶隙電壓基準源的設計

在對傳統典型CMOS帶隙電壓基準源電路分析基礎上提出了一種高精度,高電源抑制帶隙電壓基準源。電路運用帶隙溫度補償技術,采用共源共柵電流鏡,兩級運放輸出用于自身偏置電路

2010-08-03 10:51:34 35

35

35

35帶隙基準源的現狀及其發展趨勢

在模擬電路和混合模擬電路中,帶隙基準電路作為一個很重要的單元,隨著集成電路的發展和SOC系統的復雜化,已經越來越受到國內外學者的重視。本文簡單介紹了傳統的帶隙基準源的

2010-07-29 15:48:34 20

20

20

20一種結構簡單的CMOS帶隙基準電壓源設計

本文提出了一種結構簡單高電源抑制比的CMOS帶隙基準電壓源,供電電源3.3V。采用CSMC 0.5um CMOS工藝。Spectre仿真結果表明,基準輸出電壓在溫度為-40~+80℃時,溫度系數為45.53×10-6/℃

2010-07-14 16:14:36 41

41

41

41低壓CM0S帶隙基準電壓源設計

低壓CM0S帶隙基準電壓源設計

近年來,隨著微電子技術的迅速發展,低壓低功耗已成為當今電路設計的重要標準之一。比如,在一些使用電池的系統

2010-05-12 17:36:54 2281

2281

2281

2281

低溫漂低功耗的帶隙基準源技術設計

低溫漂低功耗的帶隙基準源技術設計

摘 要:設計一種低溫漂低功耗的帶隙基準結構,在傳統帶隙基準核心電路結構上增加一對PNP管,兩個雙極型晶

2010-04-28 08:59:11 1197

1197

1197

1197

一種3ppmoC帶隙基準電壓源的設計

采用二級溫度補償對傳統電流模式結構的帶隙基準電壓電路進行改進,基于chartered 0.35um cmos工藝,使用cadence spectre進行仿真,結果表明工作電壓為2v時,電路可以輸出100mv—1.8v的寬范

2010-02-23 11:39:54 28

28

28

28一種結構簡單的CMOS帶隙基準電壓源設計

本文提出了一種結構簡單高電源抑制比的CMOS 帶隙基準電壓源,供電電源3.3V。采用CSMC 0.5um CMOS 工藝。Spectre 仿真結果表明,基準輸出電壓在溫度為-40~+80℃時,溫度系數為45.53×10-6/

2010-01-11 14:20:43 27

27

27

27基于BiCMOS工藝的帶隙基準電壓源設計

電壓基準是模擬集成電路的重要單元模塊,本文在0.35um BiCMOS 工藝下設計了一個帶隙基準電壓源。仿真結果表明,該基準源電路在典型情況下輸出電壓為1.16302V,在-45℃~105℃范圍

2010-01-11 11:42:05 31

31

31

31如何選擇最佳的電壓基準源

選擇最佳的電壓基準源供稿:美信摘要:電壓基準源簡單、穩定的基準電壓,作為電路設計的一個關鍵因素,電壓基準源的選擇需要考慮多方面的問題并作出折衷。本文討

2010-01-08 23:02:30 77

77

77

77選擇最佳的電壓基準源

選擇最佳的電壓基準源摘要:電壓基準源簡單、穩定的基準電壓,作為電路設計的一個關鍵因素,電壓基準源的選擇需要考慮多方面的問題并作出折衷。本文討論了

2009-12-07 14:32:23 44

44

44

44一種低功耗差動CMOS帶隙基準源

設計了一種采用0.6μmCMOS工藝的低功耗差動帶隙基準電壓源電路。在設計中采用兩個pn結串聯結構來減小運放失調電壓的影響,并采用自偏置共源共

2009-09-04 08:57:34 30

30

30

30一種采用曲率補償技術的高精度帶隙基準電壓源的設計

本文設計了采用曲率補償,具有較高的溫度穩定性的高精度帶隙基準電壓源。設計中沒有使用運算放大器,電路結構簡單,且避免運算放大器所帶來的高失調和必須補償的缺陷。此

2009-08-31 11:29:44 26

26

26

26一種低壓低功耗共源共柵帶隙基準電壓源的實現

提出了一種低壓低功耗的帶隙基準電壓源電路,設計基于0.5μm 2P3M BiCMOS Process,并使用了低壓共源共柵電流鏡結構減少了對電源電壓的依賴,消除了精度與余度之間的矛盾,并用HL50S-

2009-08-22 09:27:53 26

26

26

26一種BiCMOS能隙基準電壓電路

設計了一種采用BiCMOS工藝的高精度能隙基準電壓電路,該基準電壓源主要用于線性穩壓器。在CSMC 0.6um工藝條件下,使用CADAENCE SPECTRE仿真工具進行仿真可得溫度在20C~80C變化時,其輸

2009-08-17 10:10:02 17

17

17

17選擇最佳的電壓基準源

摘要:電壓基準源簡單、穩定的基準電壓,作為電路設計的一個關鍵因素,電壓基準源的選擇需要考慮多方面的問題并作出折衷。本文討論了不同類型的電壓基準源以及它們的關鍵

2009-05-06 09:29:30 499

499

499

499

選擇最佳的電壓基準源

摘要:電壓基準源簡單、穩定的基準電壓,作為電路設計的一個關鍵因素,電壓基準源的選擇需要考慮多方面的問題并作出折衷。本文討論了不同類型的電壓基準源以及它們的關鍵

2009-05-03 14:42:34 447

447

447

447

選擇最佳的電壓基準源

摘要:電壓基準源簡單、穩定的基準電壓,作為電路設計的一個關鍵因素,電壓基準源的選擇需要考慮多方面的問題并作出折衷。本文討論了不同類型的電壓基準源以及它們的關鍵

2009-04-27 11:12:06 42

42

42

42帶隙基準電路的研究

本文闡述了Banba 和Leung 兩種基本帶隙基準電壓源電路的工作原理,分析了Leung結構對于Banba 結構改進的方法,分別對兩個電路的參數進行了設計,并仿真其性能,由此來比較了

2009-03-11 17:28:36 70

70

70

70 電子發燒友App

電子發燒友App

評論