LDO------LDO的原理以及構(gòu)成

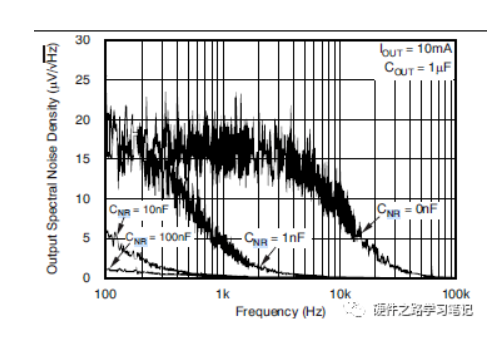

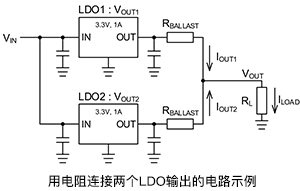

引言:LDO作為使用最為廣泛的模擬電源器件之一,因?yàn)槠洳捎镁€性工作,特別適合用來濾除開關(guān)電源產(chǎn)生的電壓紋波,在處理許多非常小的信號(hào)應(yīng)用中,這種紋波可能會(huì)造成干擾,本文從不一樣的角度來進(jìn)一步了解其基本工作原理。

1.什么是線性穩(wěn)壓器

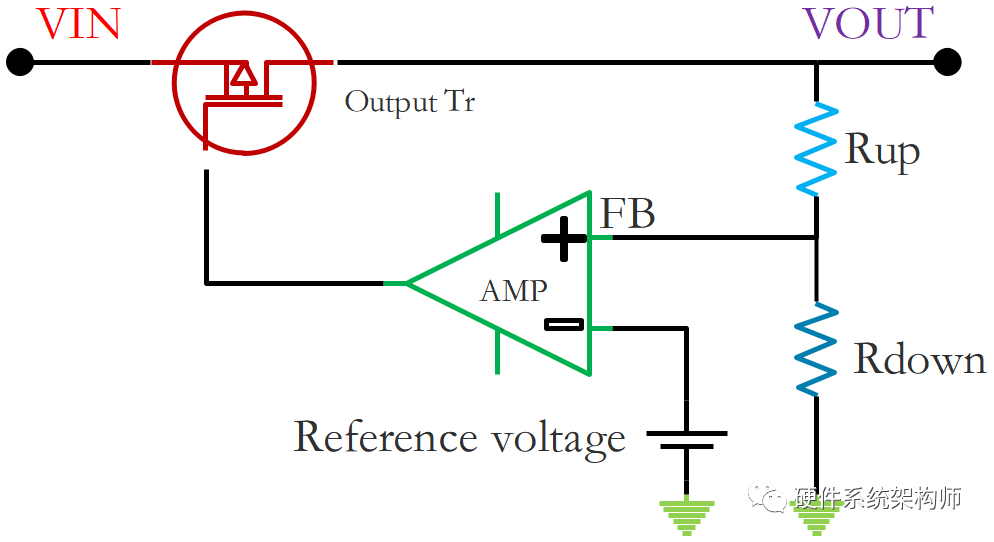

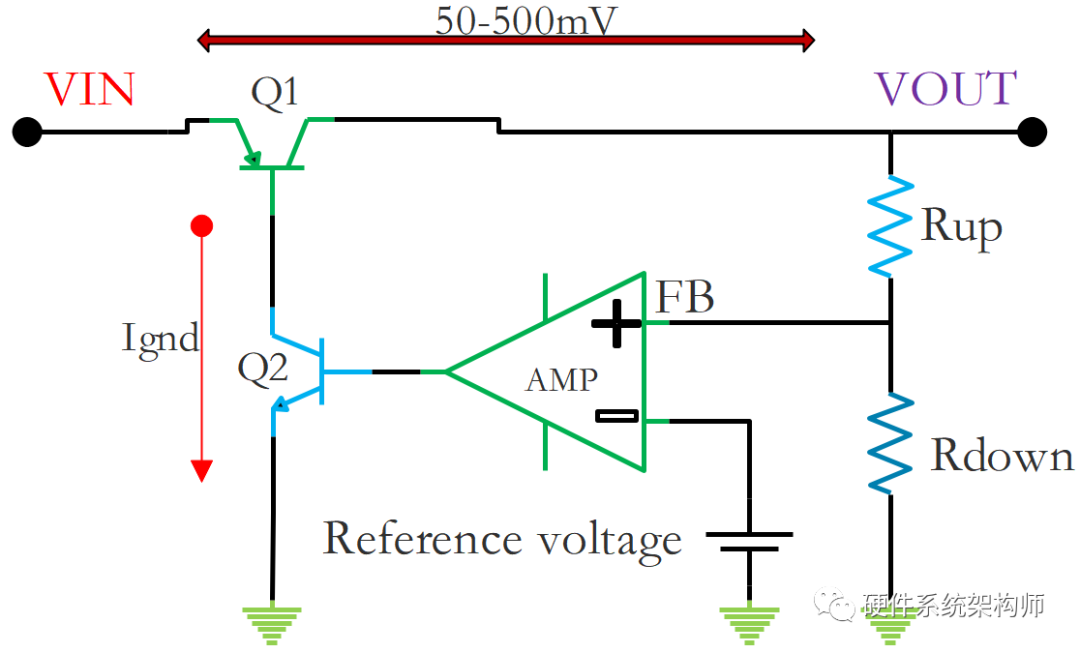

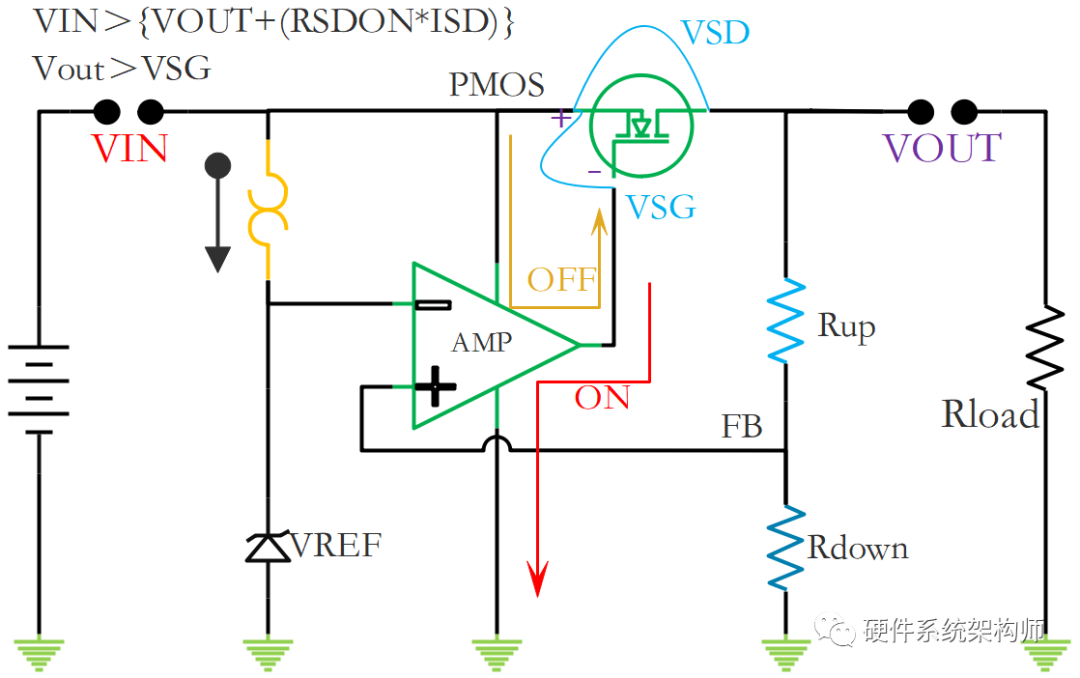

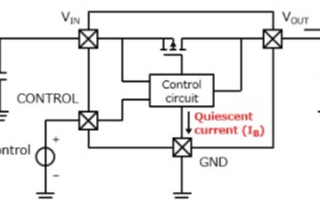

圖1-1:LDO的內(nèi)部結(jié)構(gòu)

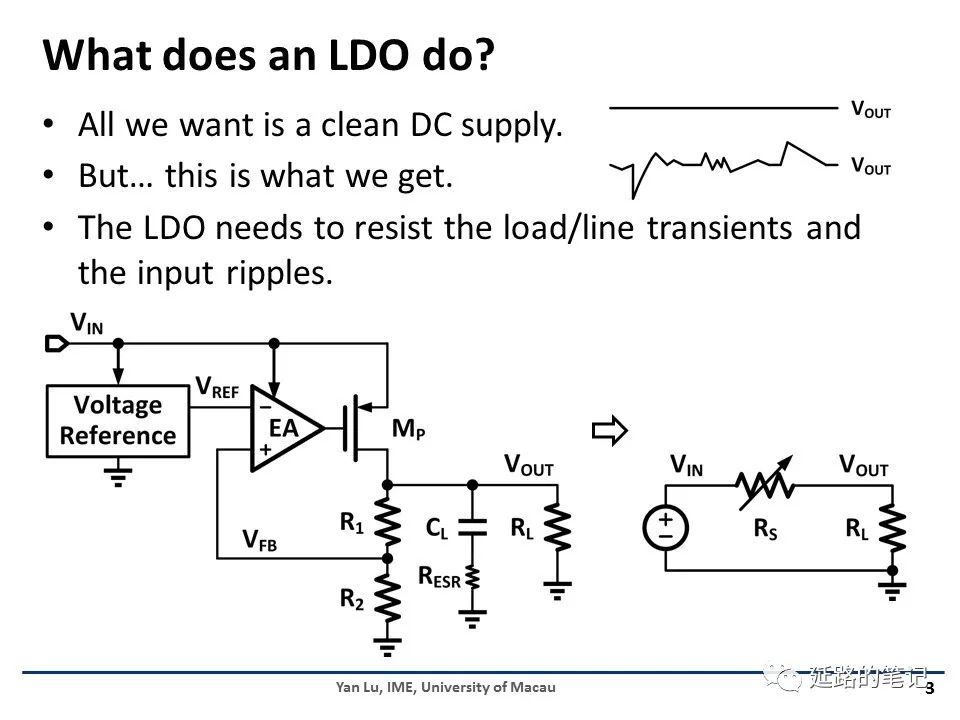

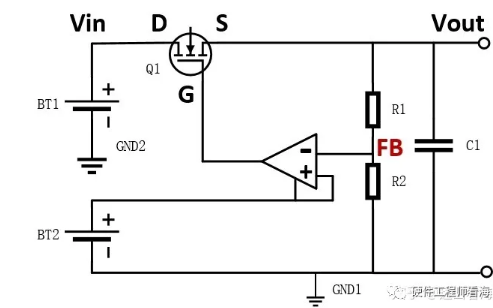

如圖1-1,LDO由誤差放大器(誤差檢測用放大器)、基準(zhǔn)電壓源、輸出晶體管三部分組成,與DCDC電路不同的是,輸出晶體管的工作狀態(tài)不是開關(guān)模式,而是線性工作模式,這一點(diǎn)許多人會(huì)進(jìn)入認(rèn)知誤區(qū),我們后面會(huì)再著重講到。作為一個(gè)標(biāo)準(zhǔn)的負(fù)反饋回路,當(dāng)輸入或負(fù)載發(fā)生變動(dòng)而輸出電壓開始波動(dòng)時(shí),誤差放大器會(huì)連續(xù)比較來自輸出電壓的反饋電壓和基準(zhǔn)電壓,并控制輸出功率晶體管使它們的差為零,從而保持輸出電壓Vout恒定。這就是通過反饋環(huán)路控制實(shí)現(xiàn)電壓穩(wěn)定(穩(wěn)壓)。在反饋環(huán)路中,誤差放大器的同相引腳電壓始終試圖與VREF 相同,故流經(jīng)Rdown的電流是恒定的。流經(jīng)Rup和Rdown的電流可以通過 VREF/Rdown求得,因此Vout是該電流乘以(Rup+Rdown)所得的值。這是遵循了歐姆定律,公式如下:

回到輸出晶體管這部分,工作在線性區(qū)域的晶體管可以視為是一個(gè)壓控電流源(MOS類型),控制電路連續(xù)監(jiān)視(檢測)輸出電壓,并調(diào)節(jié)電流源(根據(jù)負(fù)載的需求)以把輸出電壓保持在期望的數(shù)值。所以電流源的設(shè)計(jì)極限限定了穩(wěn)壓器在仍然保持電壓調(diào)節(jié)作用的情況下所能供應(yīng)的最大負(fù)載電流。輸出電壓采用一個(gè)反饋環(huán)路進(jìn)行控制,其需要某種類型的補(bǔ)償以確保環(huán)路穩(wěn)定性。大多數(shù)線性穩(wěn)壓器都具有內(nèi)置補(bǔ)償功能電路,無需外部組件就能保持完全穩(wěn)定。某些穩(wěn)壓器(比如低壓降型)則確實(shí)需要在輸出引腳和地之間連接一些外部電容以確保穩(wěn)壓器的穩(wěn)定性。

2.LDO的模型與拓?fù)?/p>

1.NPN型的LDO

NPN型的LDO分兩大類:一種是用達(dá)林頓管做的LDO,因?yàn)楫?dāng)時(shí)的單個(gè)晶體管的放大倍數(shù)不是很大,所以要用達(dá)林頓管來構(gòu)成更大的放大倍數(shù)。在這里不討論達(dá)林頓管構(gòu)成的LDO;另一種就是單個(gè)NPN 型晶體管構(gòu)成的LDO。

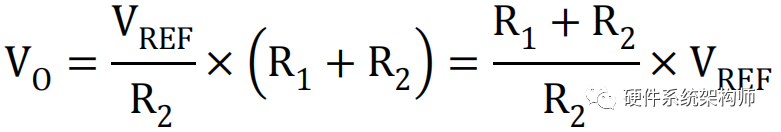

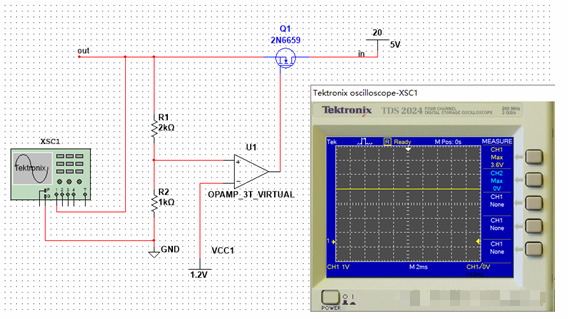

圖1-2:NPN型LDO

圖1-2是NPN型的LDO架構(gòu)圖,從圖可知經(jīng)過輸出采樣之后,通過一個(gè)小信號(hào)NPN三極管來控制一個(gè)PNP型的前級(jí)晶體管,這個(gè)前級(jí)的晶體管再通過集電極的電流來控制NPN晶體管。在上圖中Q2集電極和發(fā)射極之間的電壓VCE(Q2)一定會(huì)疊加在功率三極管Q1的集電極和基極之間的電壓VCB(Q1)上面。這兩個(gè)電壓的疊加是我們能在控制一個(gè)穩(wěn)定電壓的情況下,決定輸入電壓最低是多少的兩個(gè)成分。

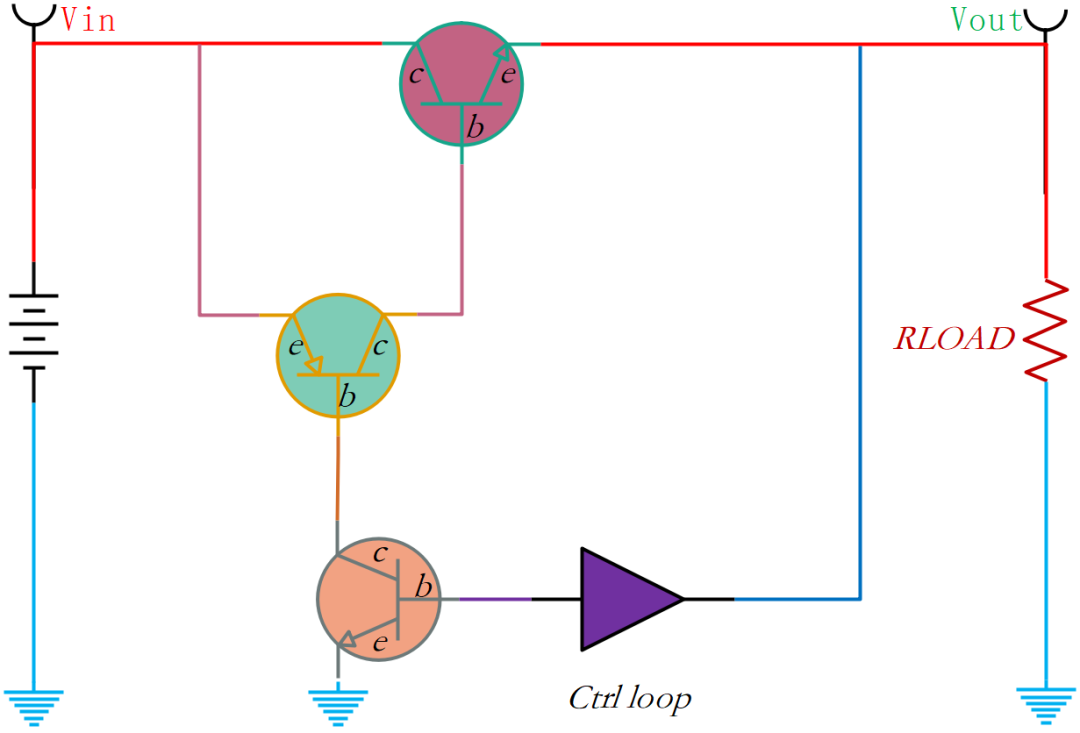

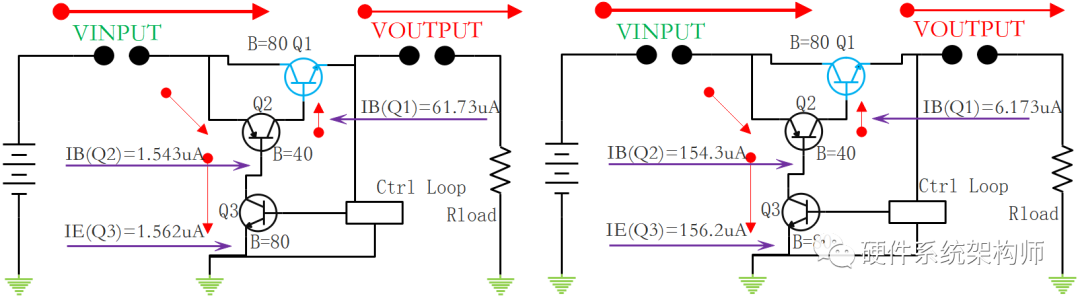

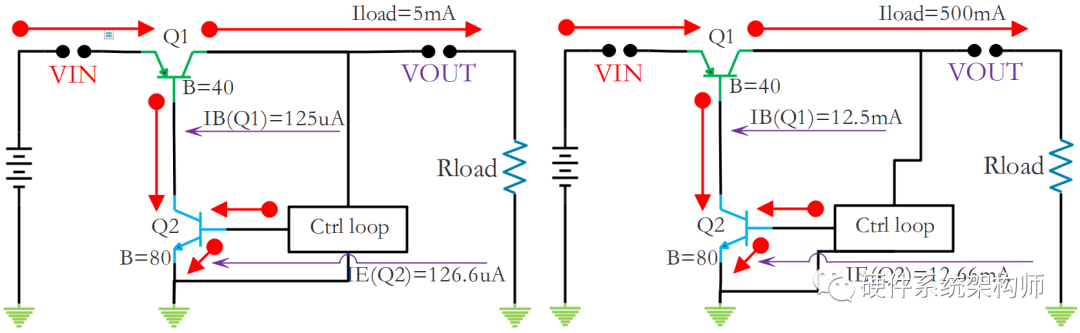

圖1-3是描述的是 NPN“準(zhǔn)LDO”在一個(gè)5mA和500mA的負(fù)載電流下需求的驅(qū)動(dòng)電流。從下圖可以看到,在不同的條件下,我們需要芯片本身的靜態(tài)電流產(chǎn)生怎樣的變化才能對(duì)這樣負(fù)載的變化有一個(gè)比較好的調(diào)整。可見在NPN型的LDO中,芯片的靜態(tài)電流是會(huì)隨負(fù)載電流的增加而增加的,而且是成比例增加的。當(dāng)然在NPN型的三極管當(dāng)中這種電流的總體的絕對(duì)值也是比較小的,就像這里例子里面的就算它的負(fù)載電流達(dá)到500mA,它的靜態(tài)電流也小于1mA 。

圖1-3:左邊為5mA負(fù)載,右邊為500mA負(fù)載

小結(jié)1.0:NPN準(zhǔn)LDO具有如下特性

要求輸入電壓至少比輸出電壓高0.9V至1.5V

接地引腳電流大于NPN-達(dá)林頓管,但小于PNP-LDO穩(wěn)壓器

需要一個(gè)輸出電容器,但一般不像PNP-LDO那樣具有特殊的ESR要求

2.NPN型的LDO

圖1-4:PNP型LDO

一個(gè)PNP型的LDO它的壓控恒流源是由一個(gè)功率型的PNP管(Q1)來構(gòu)成(圖1-4),同時(shí)在它的基極也會(huì)連接一個(gè)對(duì)地的NPN型的晶體管(Q2),這就是一個(gè)典型的PNP型LDO的架構(gòu)。在上圖右邊它一樣是由兩電阻來檢測電壓,然后把它放進(jìn)誤差放大器里面和一個(gè)基準(zhǔn)作比較,放大之后對(duì)Q2進(jìn)行控制。Q2集電極上的電流會(huì)控制Q1上基極的電流。由于功率晶體管(Q1)是PNP型的晶體管,它的集電集輸出,因此由于它的這種結(jié)構(gòu)它的輸出阻抗是比較大的。在這種輸出阻抗比較大的情況下,我們必須給輸出增加輸出電容器,也要控制這個(gè)電容器的ESR控制在一定范圍之內(nèi),才能保證這種LDO的工作穩(wěn)定。

圖1-5是描述的是PNP型LDO在一個(gè)5mA和500mA的負(fù)載電流下需求的靜態(tài)電流。由于PNP型的靜態(tài)電流,也就是它的功率晶體管(Q1)基極對(duì)地流出的電流,直接決定了它的集電極能夠給負(fù)載提供的電流,而這個(gè)輸出電流也決定于基極和發(fā)射極電流之間的β比。因此我們也可以看到NPN型LDO的靜態(tài)電流是遠(yuǎn)遠(yuǎn)大于NPN型的LDO的。由下圖我們可以看到當(dāng)在5mA負(fù)載電流情況下它的靜態(tài)電流已經(jīng)遠(yuǎn)遠(yuǎn)大于1mA了。由下圖我們也可以看到PNP型的LDO中和在NPN型的LDO中一樣,芯片的靜態(tài)電流也是會(huì)隨負(fù)載電流的增加而增加的,而且是成比例的增加。

圖1-5:左邊為5mA負(fù)載,右邊為500mA負(fù)載

小結(jié)2.0:NPN準(zhǔn)LDO具有如下特性

要求輸入電壓至少比輸出電壓高100mV至700mV

具有高于NPN型LDO的接地引腳電流

需要謹(jǐn)慎地選擇電容器數(shù)值和ESR額定值

3.NMOS型的LDO

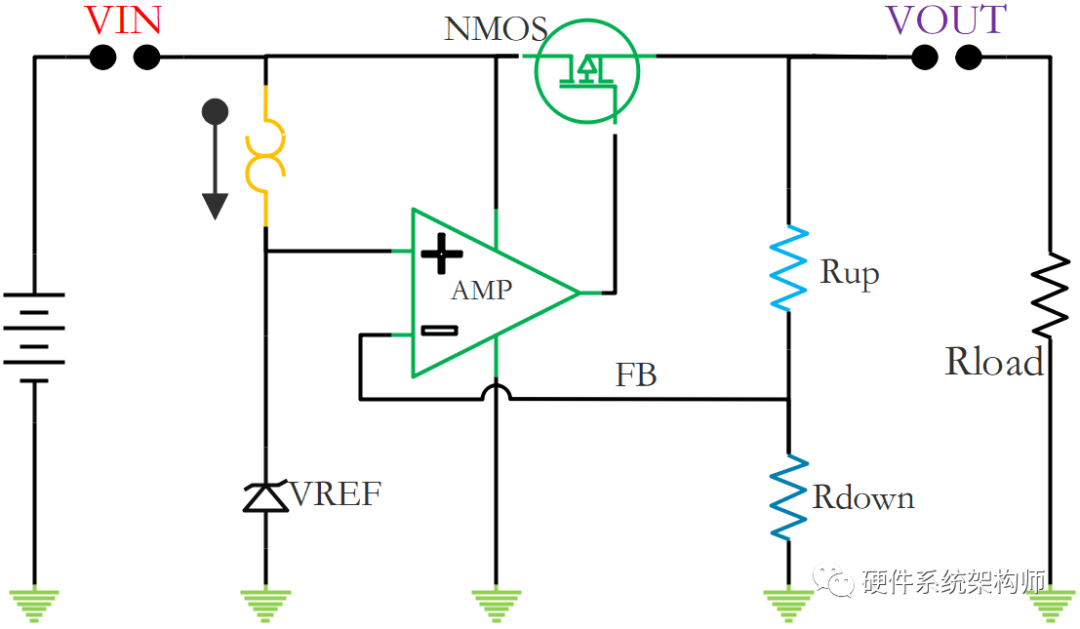

圖1-6:NMOS型LDO

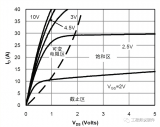

圖1-6從功率型晶體管變成了NMOS,結(jié)構(gòu)沒有變化,在整個(gè)線路里面對(duì)輸入于輸出的壓差構(gòu)成限制的不再是晶體管的基極與發(fā)射極之間的結(jié)壓降,而是MOS管里面門級(jí)到漏極之間的最小壓差。圖1-7簡單表示了經(jīng)由NMOS傳輸元件流至負(fù)載的電流。這里所使用的柵極至源極電壓(VGS)用于說明原理。NMOS LDO它同樣是采用一對(duì)電阻來采樣輸出電壓,把它送入誤差放大器的輸入端,接著和一個(gè)基準(zhǔn)做比較,然后在誤差放大器里面進(jìn)行放大,最后產(chǎn)生一個(gè)電壓信號(hào)來控制NMOS的門級(jí)。實(shí)際的柵極至源極電壓將取決于所運(yùn)用的制造工藝以及設(shè)計(jì)考慮因素。一個(gè)標(biāo)準(zhǔn)的NMOS傳輸晶體管實(shí)際上將由幾千個(gè)并聯(lián)的單獨(dú)晶體管組成。

圖1-7:NMOS傳輸元件流至負(fù)載的電流流向

與晶體管對(duì)于高負(fù)載和低負(fù)載所需要的驅(qū)動(dòng)電流變化大不同,NMOS LDO在一個(gè)50mA和3A的負(fù)載電流下需求的靜態(tài)電流差不多,雖然這種負(fù)載的變化是比較大的,但是在靜態(tài)電流上幾乎是沒什么變化的,因?yàn)镹型MOS我們只需要用電壓信號(hào)來控制,這個(gè)電壓信號(hào)不需要消耗誤差放大器里面本身的電流。因此我們可以看出由NMOS構(gòu)成的LDO相對(duì)于晶體管而言它的靜態(tài)電流是它一個(gè)最大的優(yōu)勢。

小結(jié)3.0:NMOS型LDO的特點(diǎn)

要要偏置電壓用來上拉NFET

NFET的導(dǎo)通電阻低于PFET;允許非常低的VIN和VOUT;較低的輸出阻抗可減輕負(fù)載極點(diǎn)的影響

可以在使用小容值外部電容時(shí)保持穩(wěn)定;接地引腳電流可以保持很低;高DC增益和不錯(cuò)的帶寬

要求輸入電壓高于輸出電壓(高出的值取決于傳輸MOS的VGS要求)

接地引腳電流不隨輸出負(fù)載電流變化;不需要任何的輸出電容器(為了動(dòng)態(tài)響應(yīng)更優(yōu)良建議還是使用)

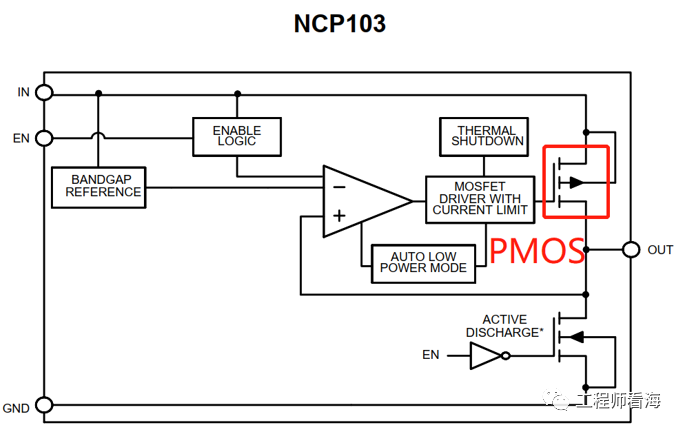

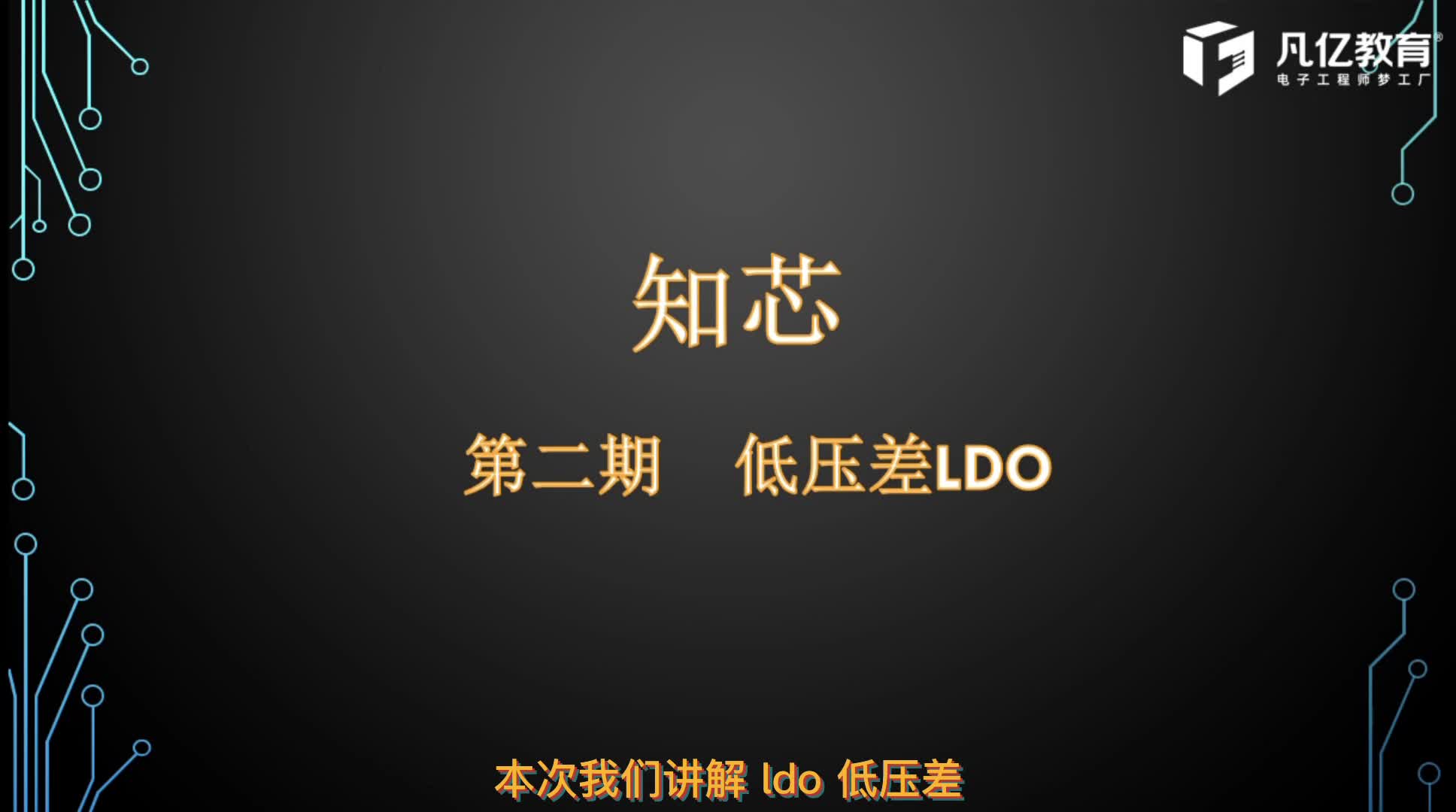

4.PMOS型的LDO

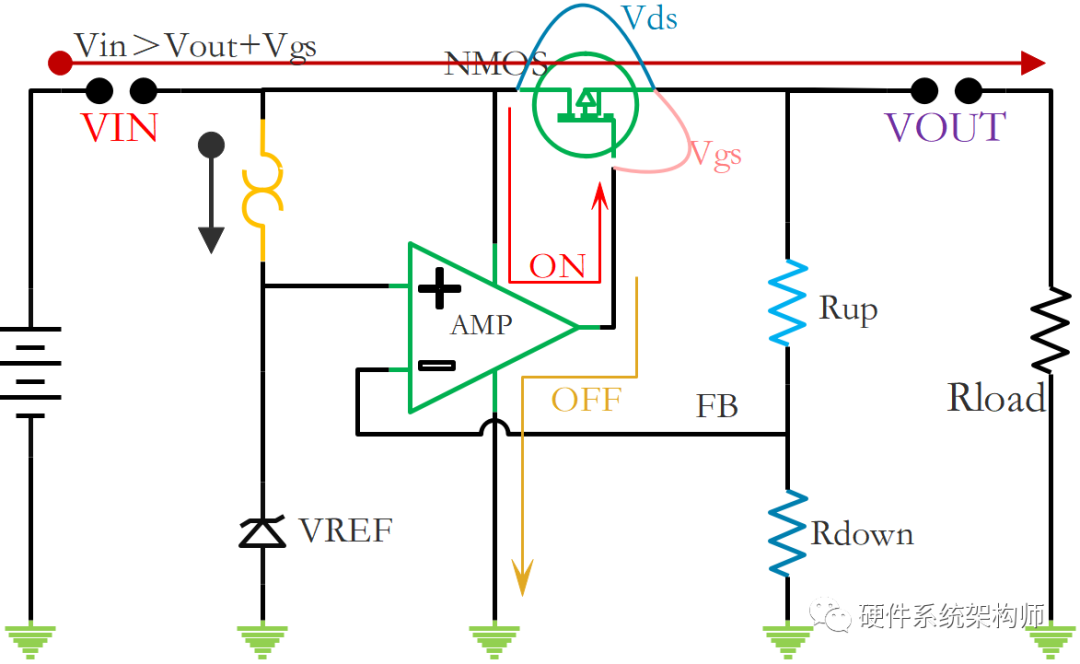

在上面的NMOS LDO中,NMOS由于它的源極和門級(jí)之間的導(dǎo)通門限,使簡單構(gòu)成的NMOS LDO它輸入和輸出之間的壓差不可能很小,必須大于這個(gè)導(dǎo)通門限,如果我們引入一個(gè)單個(gè)的偏置電壓對(duì)某些應(yīng)用來說又是一個(gè)負(fù)擔(dān)。因此我們可以引用另外一種方式,也就是PMOS構(gòu)成的LDO來減少這一部分使能。由于PMOS它的輸入端是接在它的源極上(如下圖1-8),而門級(jí)是需要低于源極才能使它導(dǎo)通,所以這個(gè)就是PMOS的LDO在驅(qū)動(dòng)上天生的要比NMOS的LDO簡單。同樣的,驅(qū)動(dòng)門限是不會(huì)隨負(fù)載電流電流的變化而改變。

圖1-8:PMOS型LDO

小結(jié)4.0:NMOS型LDO的特點(diǎn)

要求輸入高于輸出電壓(基于負(fù)載電流和傳輸元件的導(dǎo)通電阻:VIN>RDS(ON)*IOUT)

要求輸出電壓高于傳輸元件的VGS需求

要求慎重的選擇輸出電容數(shù)值和ESR額定值

為了實(shí)現(xiàn)相似的RDS(on)性能,PMOS晶體管所需的晶片面積將大于NMOS晶體

許多業(yè)界標(biāo)準(zhǔn)的線性穩(wěn)壓器采用單電壓供電執(zhí)行低壓差工作,但大多數(shù)無法同時(shí)實(shí)現(xiàn)低輸出噪聲、極低電壓轉(zhuǎn)換、寬范圍輸入/輸出以及廣泛的保護(hù)功能。PMOSLDO可實(shí)現(xiàn)壓降并在單電源下運(yùn)行,但在低輸入電壓下受到傳輸晶體管VGS特性的限制,并且它們不具備高性能LDO所提供的許多保護(hù)功能。基于NMOS的器件可提供快速瞬態(tài)響應(yīng),但它們需要兩個(gè)偏置電源為器件供電。NPNLDO可提供寬輸入和輸出電壓范圍,但它們需要兩個(gè)電源電壓或具有更高的壓差。相比之下,通過適當(dāng)?shù)脑O(shè)計(jì)架構(gòu),PNPLDO可實(shí)現(xiàn)低壓差、高輸入電壓、高PSRR以及極低的電壓轉(zhuǎn)換,具有多重保護(hù)功能,并且只需要單電源。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論