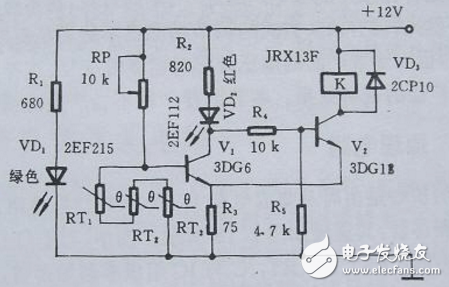

過流保護電路工作原理

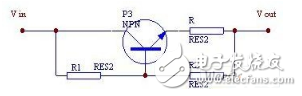

當電路處于正常狀態時,通過過流保護用PTC熱敏電阻的電流小于額定電流,過流保護用PTC熱敏電阻處于常態,阻值很小,不會影響被保護電路的正常工作。當電路出現故障,電流大大超過額定電流時,過流保護用PTC熱敏電阻陡然發熱,呈高阻態,使電路處于相對“斷開”狀態,從而保護電路不受破壞。當故障排除后,過流保護用PTC熱敏電阻亦自動回復至低阻態,電路恢復正常工作。

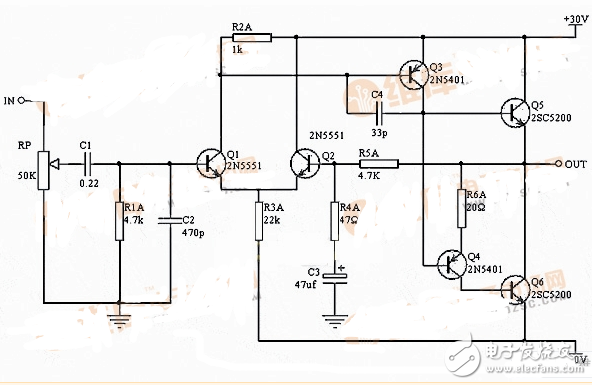

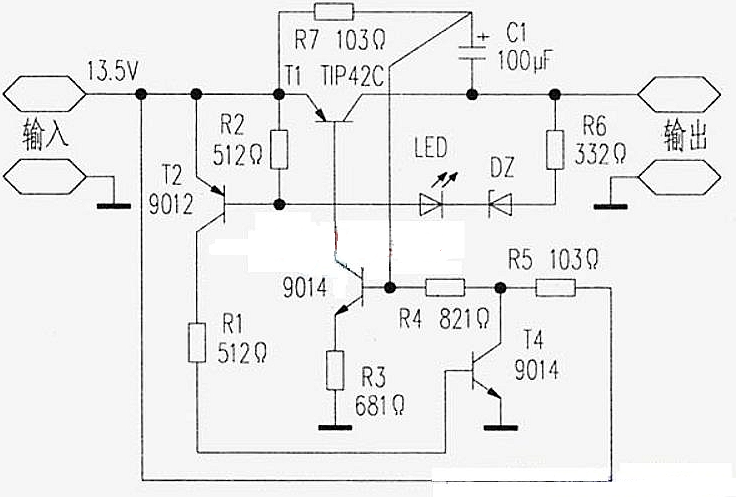

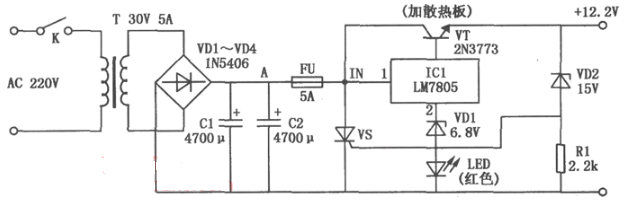

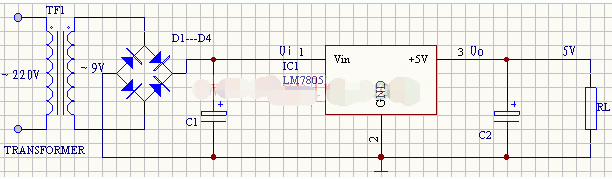

簡單過流保護電路設計方案(一)

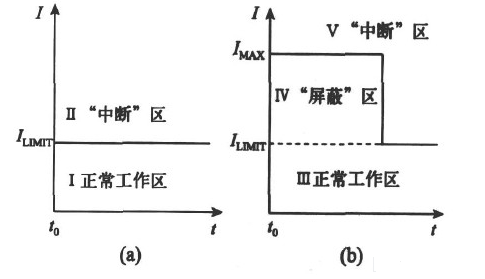

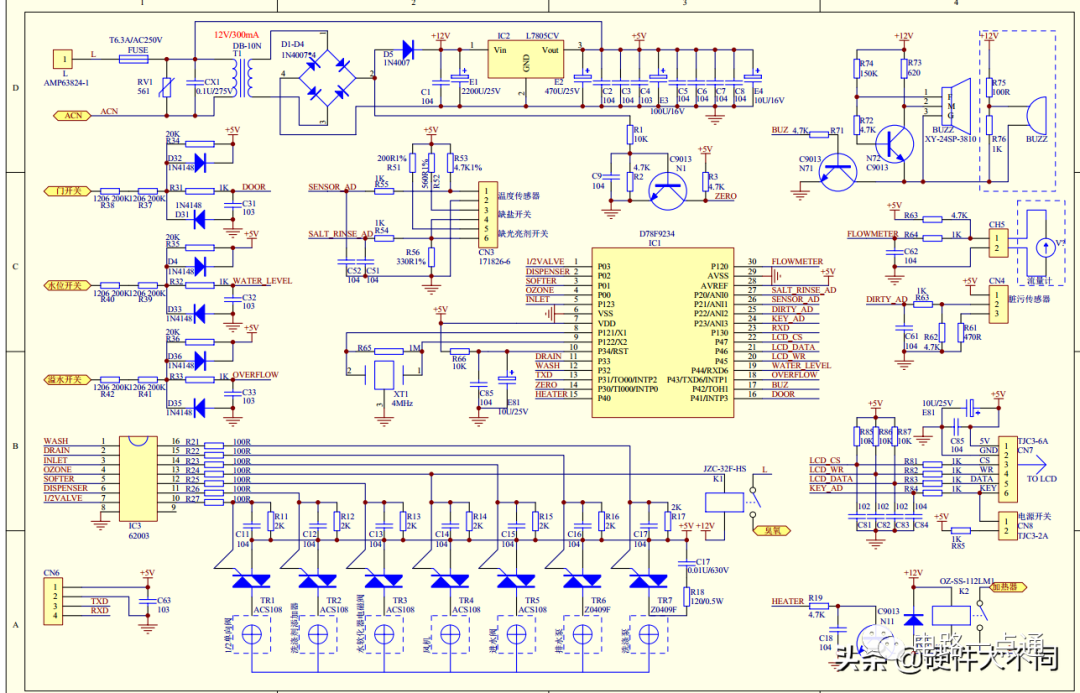

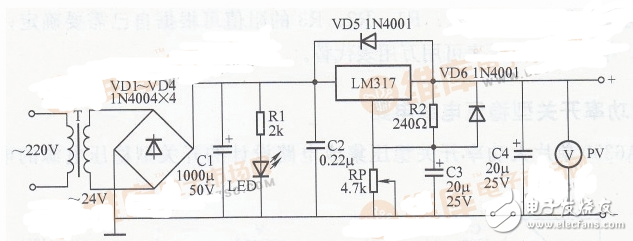

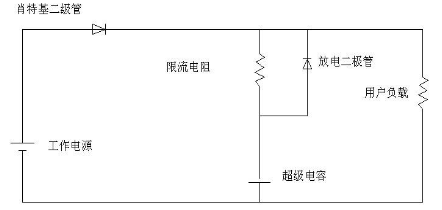

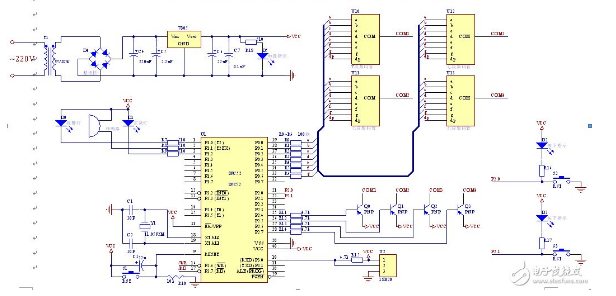

傳統的過流保護電路由電流感應電路、比較電路以及輸出級組成,分為恒流式過流保護和折返式過流保護。傳統的過流保護電路采用的是“中斷”模式,對于任何過流情況,只要負載電流大于限制電流,都將使LDO中斷運行。

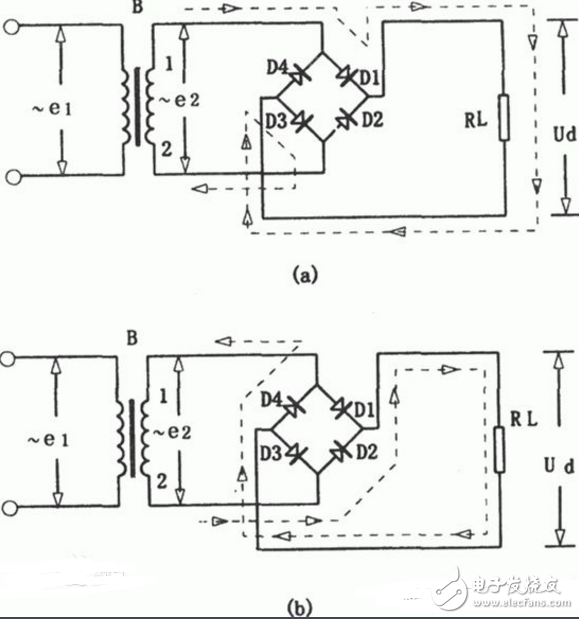

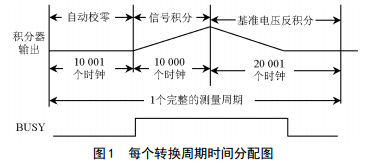

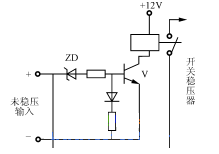

當負載電流超過限制電流ILIMIT不太多且持續作用時間不太長時,我們希望過流保護電路能保持LDO不中斷工作,因此需要采用“屏蔽”模式屏蔽掉部分可以讓LDO不中斷運行的過流信號,對于過流幅值和持續作用時間超過范圍的過流信號,過流保護電路又能采取中斷LDO工作的模式。傳統的“中斷”模式電流保護電路工作狀態如圖1(a)所示,分為正常工作區Ⅰ和“中斷”區Ⅱ,當負載電流不超過ILIMIT時,LDO工作在正常工作區,當負載電流超過ILIMIT時LDO進入“中斷”區。加入“屏蔽”模式后的過流保護電路工作狀態如圖1(b),分為正常工作區Ⅲ、屏蔽區Ⅳ以及中斷區Ⅴ,當負載電流小于ILIMIT時,LDO處于正常工作區,當過流信號的幅值在ILIMIT和最大幅值電流IMAX之間,持續作用時間在t=tMAX之內即同時滿足ILIMIT≤ILOAD≤IMAX,t≤tMAX時,LDO進入屏蔽區,這個范圍之外的過流信號將進入中斷區。對比圖1(a)和(b)可以看出,改進過流保護電路后的LDO的正常工作區包括圖1(b)的正常工作區Ⅲ和“屏蔽”區Ⅳ,增大了工作區的范圍,提高了LDO的工作效率。

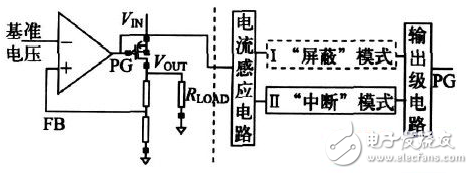

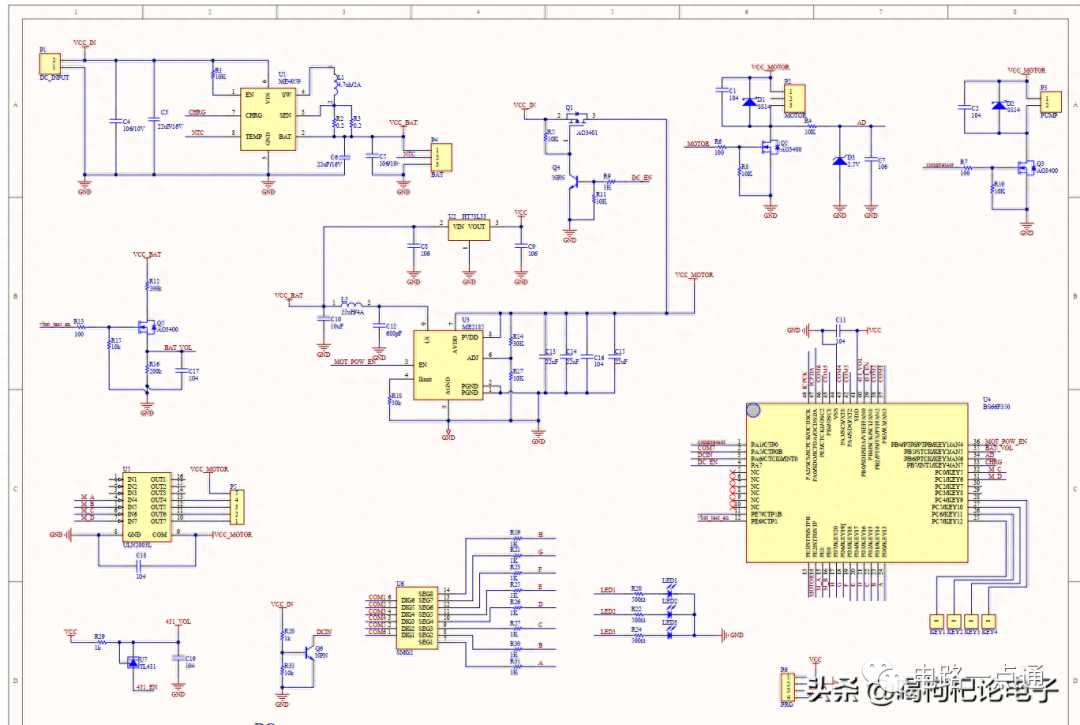

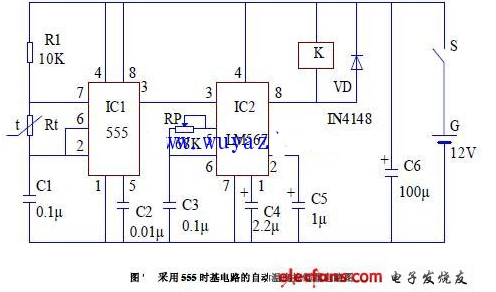

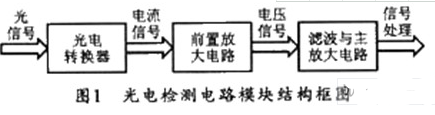

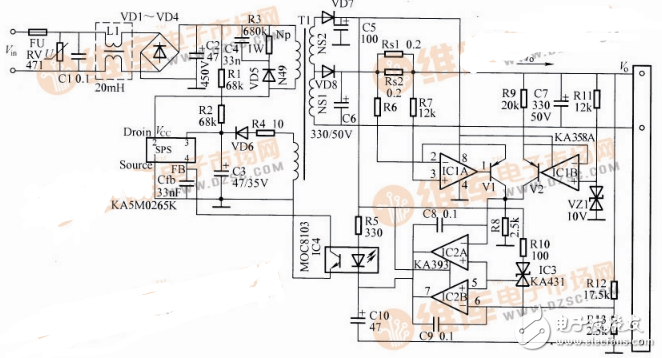

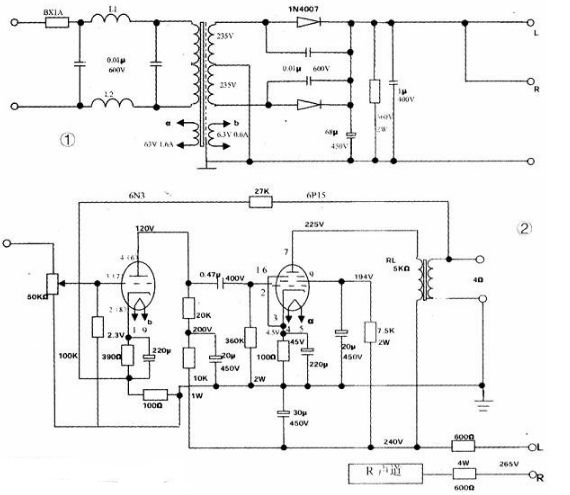

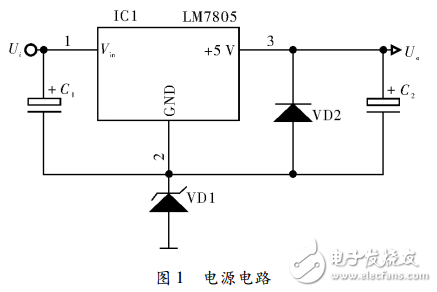

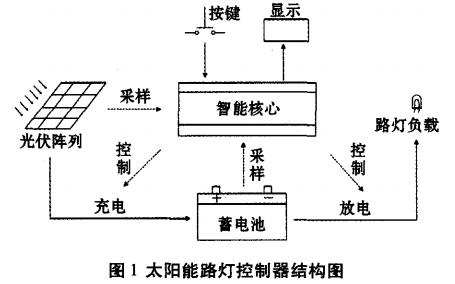

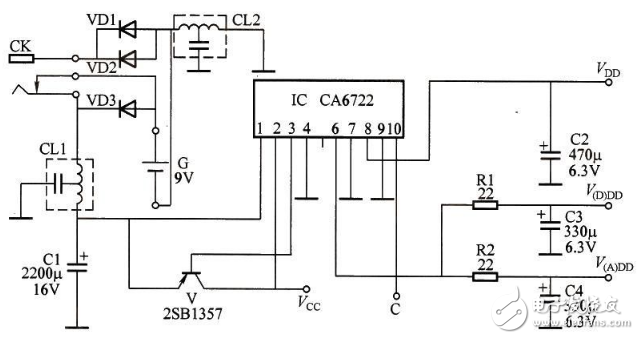

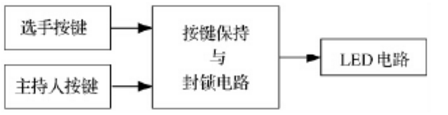

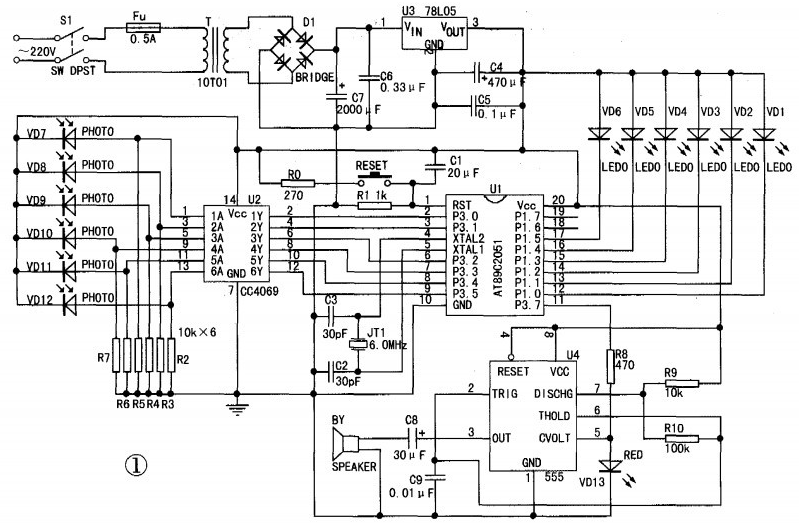

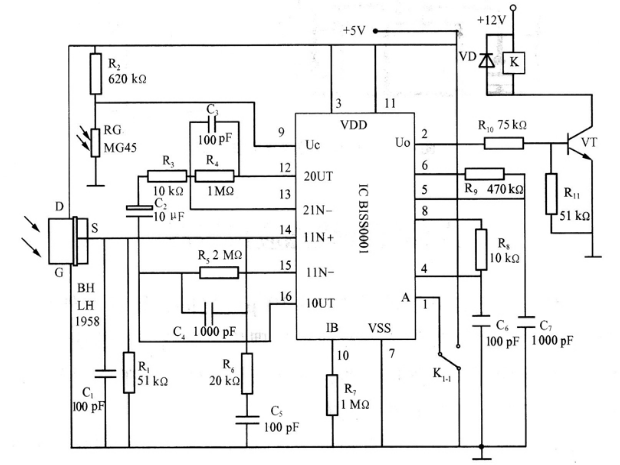

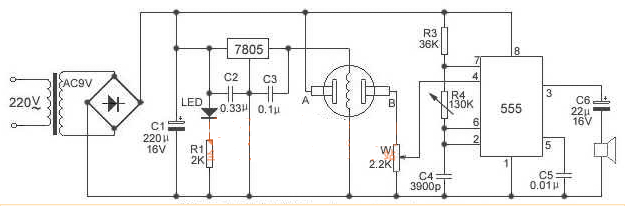

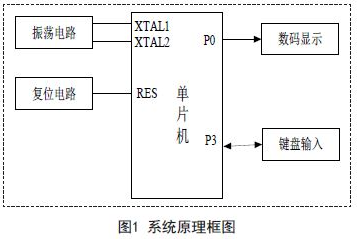

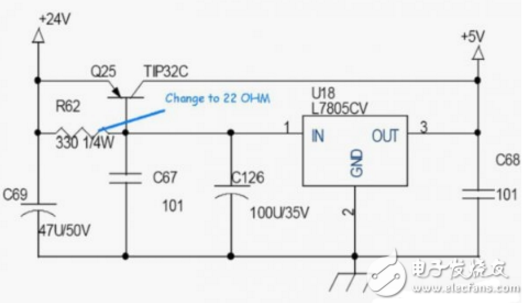

包含過流保護電路的LDO整體框圖如圖2所示,虛線左邊是LDO主體電路,包括誤差放大器、功率管、負載電阻以及分壓電阻。虛線右邊部分為電流保護電路,主要作用是感應并檢測負載電流是否超過限制電流,然后通過控制功率管來決定是否使LDO中斷運行,包括電流感應電路和控制電路。傳統的過流保護電路只采用圖2中實框Ⅱ所示的“中斷”模式(不包括虛框),對于任何負載過流情況,不論持續作用時間如何,都使LDO中斷工作;本文在傳統的“中斷”模式基礎上,增加了“屏蔽”模式(如圖2中虛框Ⅰ),能有效屏蔽希望LDO不中斷工作的過流信號,使LDO更高效運行,同時保留“中斷”模式,保證LDO安全工作。

圖2 ?帶過流保護電路的LDO框圖

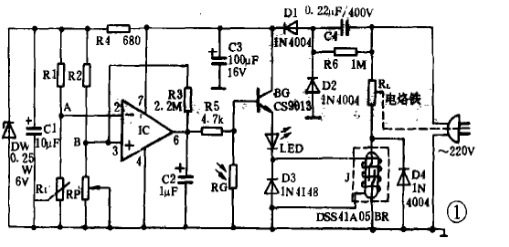

“屏蔽”模式電路實現

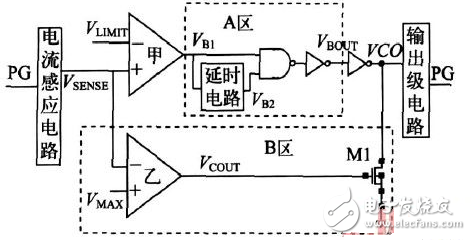

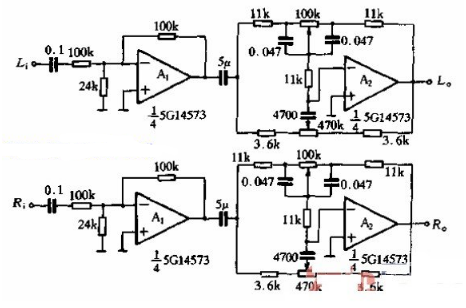

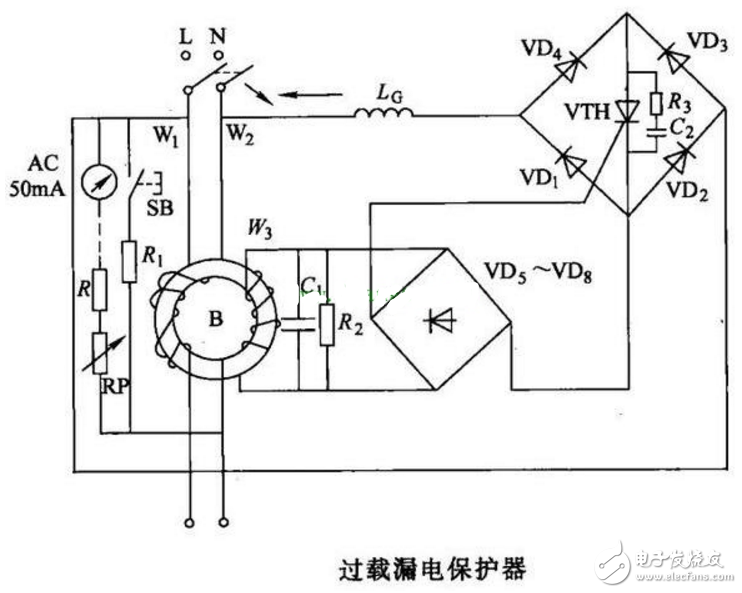

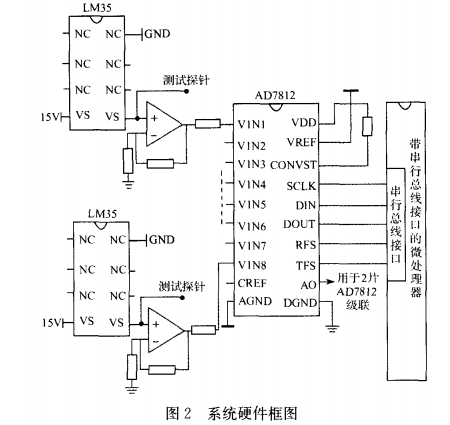

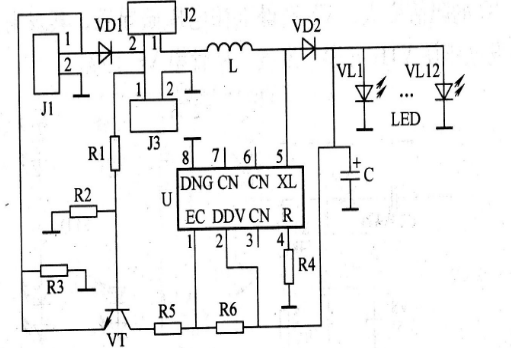

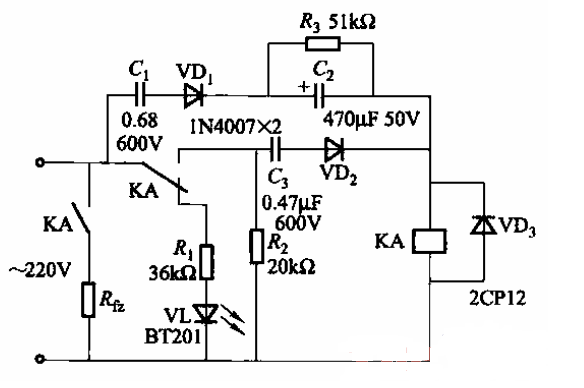

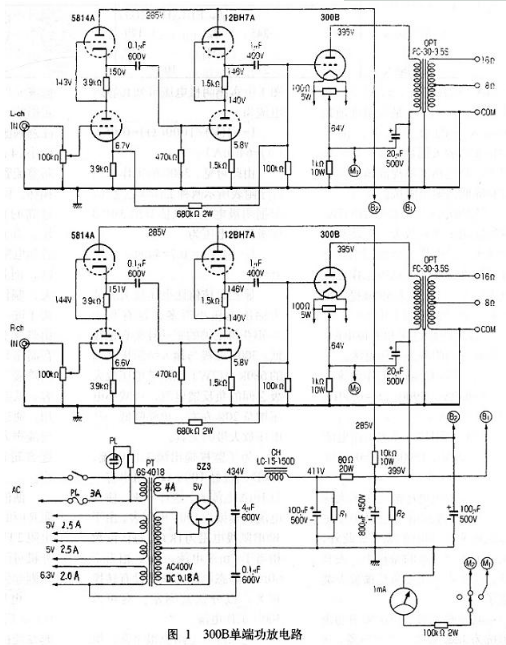

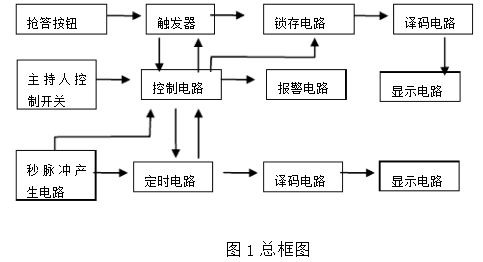

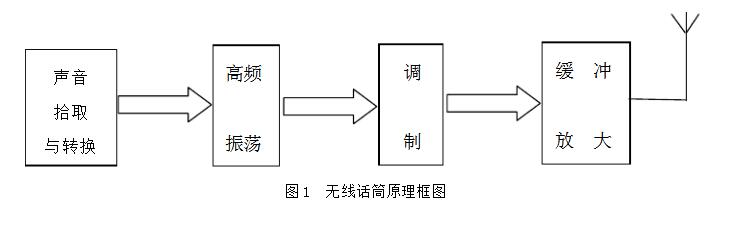

圖3是改進前后的過流保護電路圖。不加虛框部分是傳統的“中斷”模式過流保護電路,由電流感應電路、比較電路以及輸出級電路組成。電流感應電路采樣功率管電流。采樣得到的電流和限制電流ILIMIT分別轉化為比較器的兩輸入端電壓VSENSE和VLIMIT并進行比較,得到VCO。VCO作用于輸出級電路以控制功率管柵極電壓。如果負載過流,過流保護電路使得功率管柵極電壓PG為高電平,強行使LDO中斷。

圖3 ?改進后的電流保護電路圖

如果我們在電路中加入圖3虛框A區所示的電路結構,電路將變為“屏蔽”模式電流保護。屏蔽電路由延時電路、或非門構成。比較器甲輸出的信號VB1經過延時后得到VB2,VB1和VB2進行或非運算再經過一次反向后得到屏蔽電路的輸出信號VBOUT。

由于邏輯或運算只能使同時為1的兩個信號保持不變,因此,可以通過或非門和反相器消除掉延遲時間內的脈沖信號。在過流保護電路中增加屏蔽電路,則可屏蔽掉延遲時間內的過流信號,但如果負載電流太大,可能瞬間燒毀功率管,因此需要相應的關斷電路。當負載電流超過最大限制電流IMAX時,過流保護電路能不經過延遲直接關斷LDO。

圖3虛框B區電路能解決屏蔽時間內大電流可能導致功率管瞬間燒毀的問題,當延遲時間內出現很大過流信號時,能及時關斷功率管,保證系統安全。關斷電路由比較器乙和NMOS開關管M1組成。

當過流信號超過最大限制電流IMAX(此時VSENSE》VMAX)時,比較器乙輸出VCOUT為高電平導致開關管M1導通,使得VCO強行為低電平而不受屏蔽電路影響并同步關斷LDO,保證功率管安全。當過流電流不是太大時,比較器輸出電壓VCOUT為低,開關管M1不導通,不影響屏蔽電路工作。

圖3所示的改進電流保護電路能夠實現圖1(b)所期望的“屏蔽”區工作模式。負載電流過流最大持續作用時間tMAX和最大過流幅值IMAX即為“屏蔽”區的時間和幅值邊界。實際應用中,功率管能承受的熱功耗和擊穿電流是有限的。最大持續作用時間tMAX由功率管能承受的熱功耗和散熱性能決定,而功率管的最大擊穿電流確定了過流的最大幅值IMAX。

對于特定的應用需要,通過設定合理的屏蔽時間與最大過流幅值,能使LDO更高效地運行。

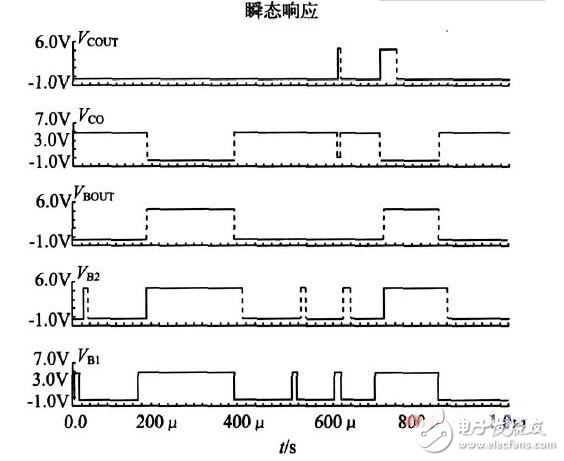

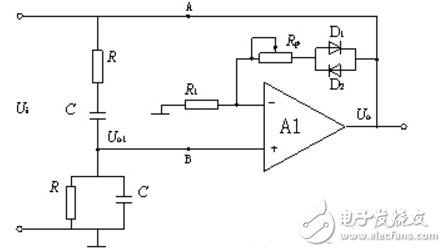

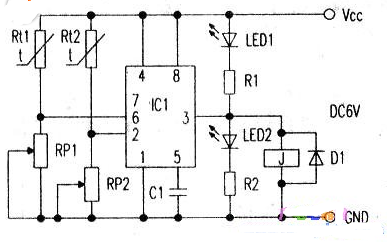

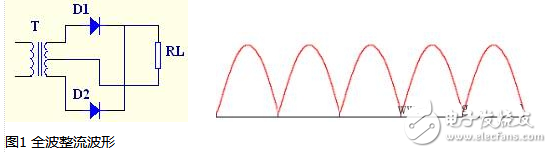

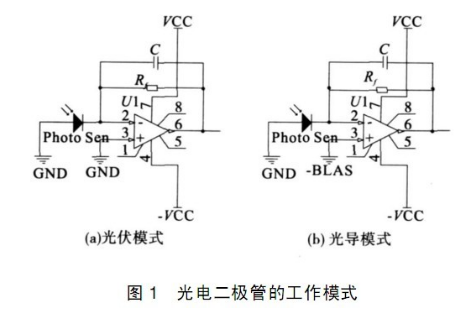

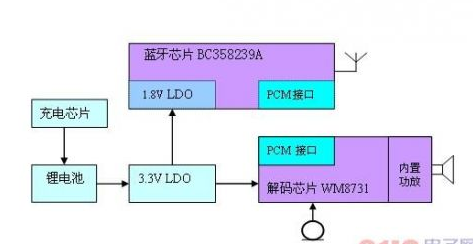

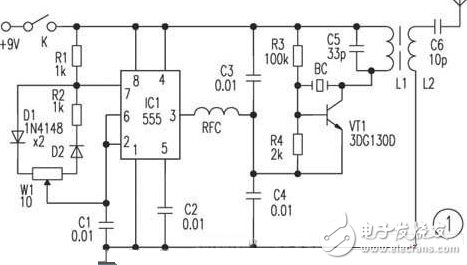

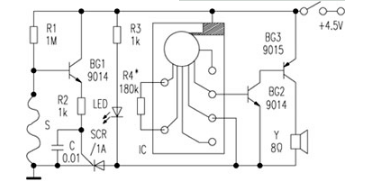

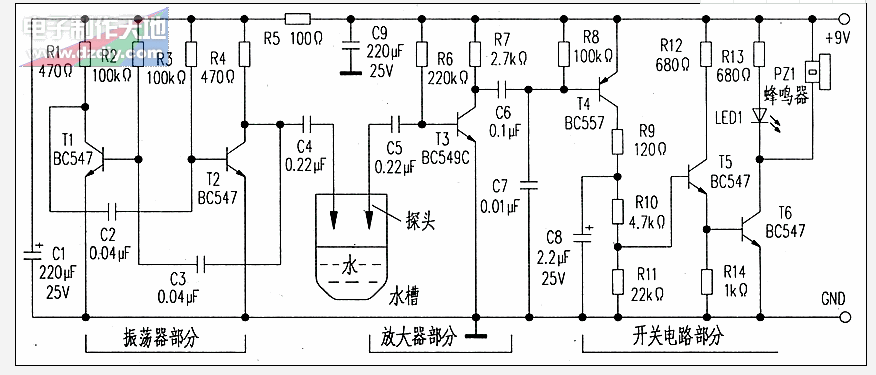

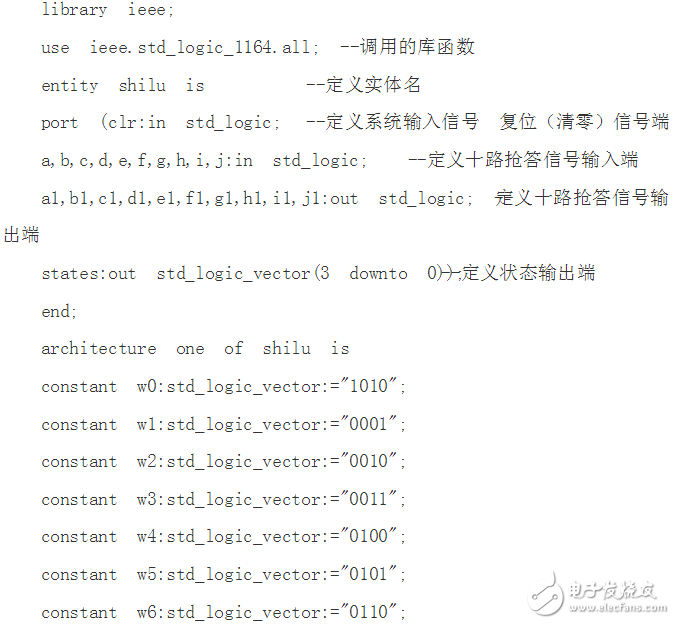

“屏蔽”模式的邏輯關系如圖4所示,其中VB1和VCOUT分別為比較器甲和乙的輸出信號,VB1經過一個延遲時間后輸出信號為VB2,屏蔽電路輸出電壓為VBOUT,VCO為屏蔽電路的輸出端。VB1、VB2和VBOUT的波形反應了屏蔽電路的邏輯關系,只有當VB1和VB2同時為高電平,VBOUT才為低電平,否則VBOUT一直為高電平,因此屏蔽電路屏蔽了延遲時間內的脈沖信號,保持寬脈沖信號;VCOUT為使能端,只要VCOUT為高電平,VCO立即變為低電平。

圖4“屏蔽”電路邏輯關系圖

電子發燒友App

電子發燒友App

評論