概述:REF191是一款精密帶隙基準電壓源芯片,它采用專利的溫度漂移曲率校正電路,激光微調高度穩定的薄膜電阻,以實現非常低的溫度系數和較高的初始精度。REF191采用SOIC、TSSOP及DIP8腳封裝工藝;...

2021-04-13 06:00:16

概述:REF198是一款精密帶隙基準電壓源芯片,它采用專利的溫度漂移曲率校正電路,激光微調高度穩定的薄膜電阻,以實現非常低的溫度系數和較高的初始精度。REF198采用SOIC、TSSOP及DIP8腳封裝工藝;...

2021-04-14 07:34:35

采用1830工藝設計預設值電流I=10uA,由公式過驅動電壓0.2V,得到PMOS寬長比12.5/1由公式過驅動電壓0.2V,得到NM8寬長比2.8/1設置K=4,NM7寬長比4×2.8/1由公式帶入計算得到R大小為9.96KΩ進行DC仿真,發現電流有偏差,調節R=15K歐姆,得到電流大小為10.07u對其進行VDD從3.5-5V和溫度從-40-120℃的直流掃描,仿真圖如圖隨溫度變化浮動巨大,同時隨電壓改變電流不能很好的穩定。

2021-12-30 08:15:23

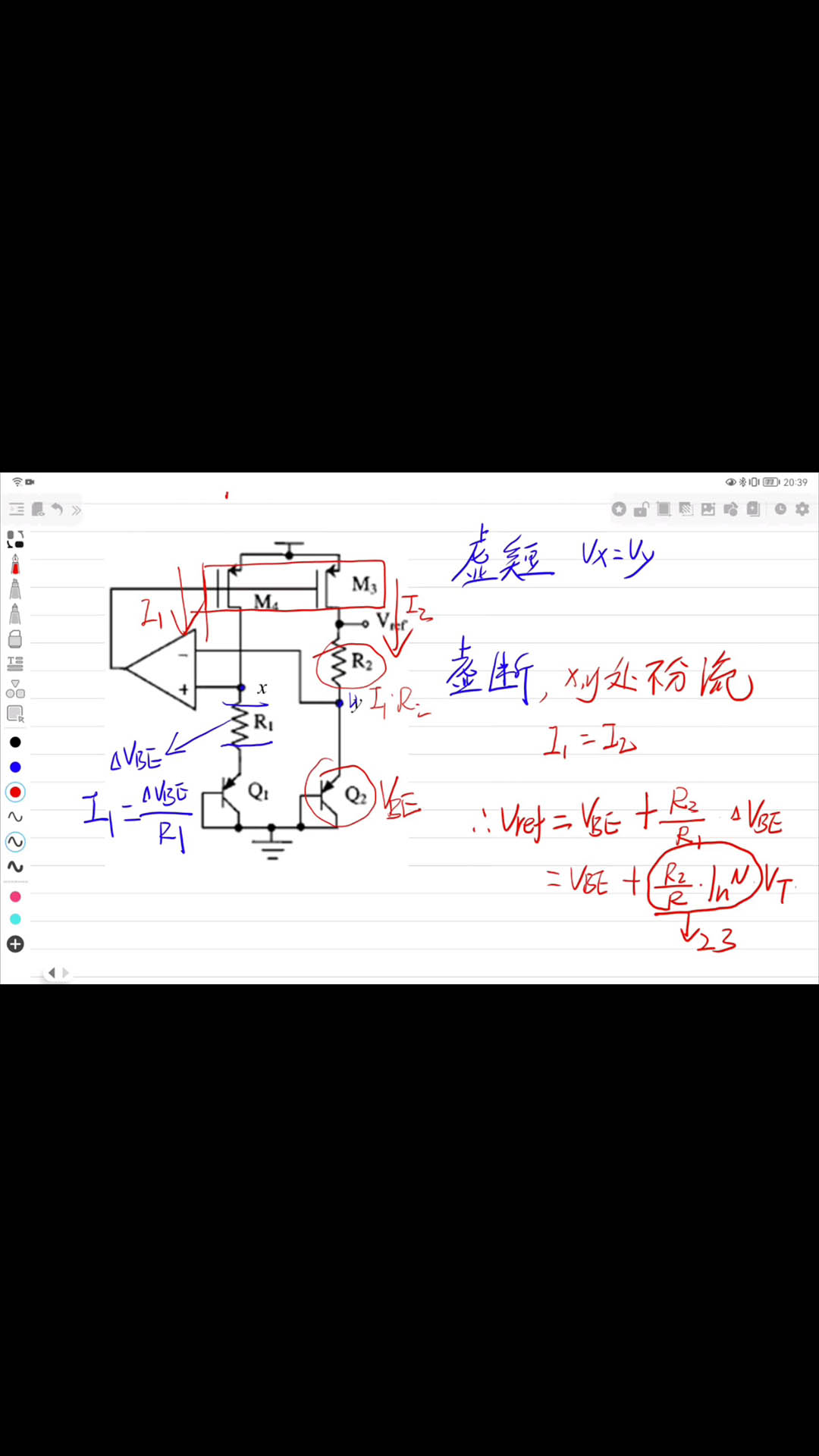

帶隙基準是什么?帶隙基準的功能工作原理是什么?帶隙基準的結構是由哪些部分組成的?

2021-06-22 08:14:04

最近在做一個項目,就是帶隙中運放的前后仿真不一致 。后仿真(NO RC)的時候出現的SA SB參數和前端仿真中的SA SB 參數不同。如果將后端網表的SA SB 參數改成前仿真默認參數,與前仿真

2021-06-25 08:07:33

這是帶隙基準仿真波形。這款帶隙基準用于RFID芯片中,當整流出來為周期性波動電壓時,供給帶隙后,帶隙輸出也會發生周期性抖動。在單仿帶隙時,DC仿真和瞬態仿真都沒有問題,可以穩定輸出。但是如果瞬態加

2021-06-25 07:27:47

標準的帶隙基準,輸出電壓約為1.2V,10ppm左右。設計好,接入電路中,瞬態仿真,輸出電壓波形為以1.2V為直流,類似100MHz頻率的20mv峰值正弦波做周期等幅振蕩,可能的原因是什么。

2011-12-07 14:43:44

工作站;適用于各種視頻ramdac;智能工業發射機;PCMCIA卡;汽車;3 V/5 V,8位至12位數據轉換器。 一般說明 AD1580是一個低成本,2端(分路),精密帶隙基準。它為50μA到10

2020-07-15 10:06:46

AD7674芯片使用外部基準電壓,在ADC工作的時候基準電壓對地值會被拉低,ADC不工作的時候恢復正常。ADC摘掉基準電壓也恢復正常。

基準電壓芯片位REF02,推測它的帶載能力不夠,在后面加了電壓跟隨電路。加入電壓跟隨電路后,基準電壓正常工作,跟隨電路輸出電壓會被拉低。

請問如何解決?

2023-12-08 07:46:26

AN1078的電流基準是多少?為什么使用偏置減ADC采集值,而不是ADC采樣值減偏置?

2021-10-14 08:54:07

the first conversion, a delay of 5 ms is required.跟據手冊所說,若是利用外部基準,則對ADCREFSEL寄存器進行配置進行配置,但是必須在帶隙上電之前配置

2015-08-19 16:21:45

1.請問各位大神GTM模塊中的TBU時間基準單元中,這個時間基準是什么意思呢?是指GTM從CMU得到系統時鐘之后通過TBU進行處理得到GTM本身需要的時鐘嗎?2、TBU模塊通過獲取DPLL模塊產生

2024-02-21 08:25:49

請教大家, N76E616 內部帶隙電壓的存儲參數如何讀取?

2023-06-25 11:04:36

1. 看了V1.04的芯片手冊,但是沒看到 芯片內部帶隙電壓的出廠校準值 的存儲地址, 請問如何讀出帶隙電壓值?

2. 我將芯片內存存儲器都用作APROM區,請問我將最后1K區域當做EEPROM來存儲參數,要如何操作? 這個內部APROM區域大概可以重復寫入多少次內?

2023-06-27 06:20:00

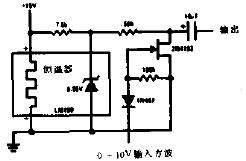

REF191精密微功耗,低壓差電壓基準的典型應用。 REF19x系列精密帶隙電壓基準采用獲得專利的溫度漂移曲率校正電路和高穩定性薄膜電阻的激光微調,可實現極低的溫度系數和高初始精度

2019-06-20 14:26:01

嗨,正在查看最新版本的STM8S003F3P6數據表,似乎沒有關于AIN7帶隙的評論。之前的數據表中提到過它(我有一個來自2014年)。帶隙是否正式出現在這個uC上?我的代碼顯示它在物理上存在

2019-02-28 16:22:05

如 VL53L1CX 的應用說明 AN5231 中所述,如果同時存在覆蓋窗和大氣隙,則可能需要墊圈來限制負面串擾效應。 是否有針對 VL53L5CX 型號的類似應用說明?例如,可以考慮以下規范

2022-12-13 08:09:43

最近diy制作一個USB電源電流表,使用的N76E003單片機,液晶屏顯示部分程序,也弄好了,就差adc采樣了,想利用內部帶隙電壓計算外部電壓值,不知道怎么計算,讀取UID最后兩個字,值為1663

2023-06-16 07:32:22

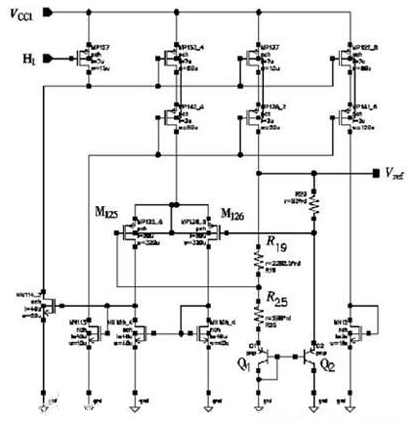

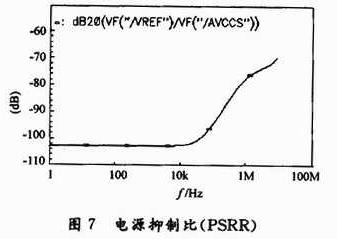

李沛林 楊建紅 在模擬及數/模混合集成電路設計中,電壓基準是非常重要的電路模塊之一,而通過巧妙設計的帶隙電壓基準更是以其與電源電壓、工藝、溫度變化幾乎無關的特點,廣泛應用在LDO及DC-DC集成

2019-07-12 07:36:42

傳統帶隙基準源有哪些基本原理?什么樣的基準源電壓才能滿足普通應用要求?

2021-04-07 06:52:08

溫度系數,而受控晶體管發射結具有負溫度系數,,晶體管的負溫度系數是什么意思?而且要求電阻和發射結的總電壓達到硅管的能帶隙電壓此時整個電路不具有溫度系數?能帶隙電壓是什么?

第二張圖,虛線框以內是基準源

2024-01-27 11:56:26

使用具有1.2外部帶隙基準的TC7116模數轉換器的典型應用(VIN- 與通用相連)

2019-07-26 08:35:49

M0518 ADC的內部帶隙電壓是指什么?

2018-10-16 09:53:21

。兩個獨立的緩沖器從帶隙電壓中生成VREF和VBIAS。內部電阻器依尺寸定制而使VBIAS = VREF/2。表3列出了REF2030的主要技術規格。圖4:解決方案3(雙輸出基準電壓- REF2030

2018-09-12 11:39:51

大家好,我有一個問題,配置PIC18F85 J94ADC。在第22.3.2頁中,從PIC18F97 J95家庭數據表中得知,內部帶隙基準電壓可用于ADC正基準電壓。然而,在寄存器描述中沒有提到這樣

2019-01-29 06:04:01

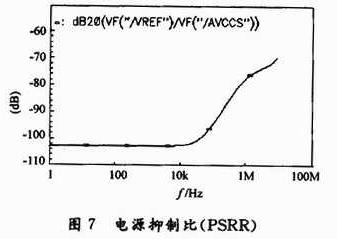

基準;LDO穩壓器;溫度系數;電源抑制比;運算放大器 CMOS帶隙基準電壓源不但能夠提供系統要求的基準電壓或電流,而且具有功耗很小、高集成度和設計簡便等優點,廣泛應用于模擬集成電路和混合集成電路中。帶隙

2018-10-09 14:42:54

一個可行的方法實現與溫度無關的電壓基準可調帶隙基準電壓電路分析及仿真

2021-04-08 06:59:00

帶曲率補償的帶隙基準源的原理是什么?它與傳統帶隙基準源相比有何不同?

2021-04-09 06:35:43

如果我們可以確定帶隙電壓和對應的ADC原始數據那么我們就可以通過比例運算知道VCC,因為滿量程對應的就是VCC,也就是0x0FFF對應VCC

即VCC:0xFFF=帶隙電壓:帶隙電壓ADC

2023-06-25 08:18:31

最近在做帶隙基準源,用到AMP鉗位電壓,使倆點電壓一致,拉雜為沒講用到的AMP要有什么要求?但看到資料的電路基本都是單級AMP,想問下大大們,這個AMP鉗位電壓原理就是虛短虛斷么?(如果是要求增益應該很大啊),還有那些要求?第一次發帖,小弟先謝了。

2022-06-15 10:26:32

氣隙/氣隙磁通量在電機中有什么作用?如何合理設計?

2021-02-04 08:01:17

氣隙的影響電機的氣隙

2021-01-22 06:15:07

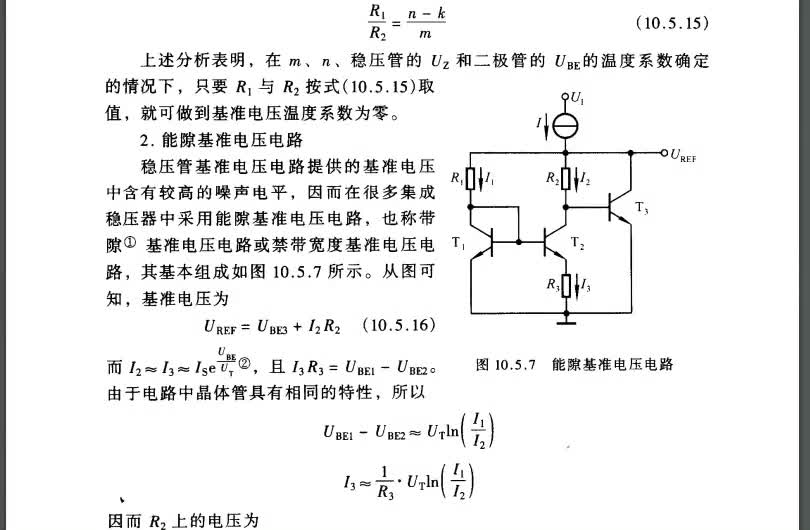

帶隙基準源原理是什么?雙極帶隙基準電路的實際電路結構是怎樣構成的?怎樣對雙極帶隙基準電路進行仿真測試?

2021-04-21 06:20:19

帶隙基準電壓源工作原理是什么?一種低溫漂輸出可調帶隙基準電壓源的設計

2021-05-08 06:38:57

1,通過MS51FB9AE帶隙電壓(Band-gap)能反推出電源電壓,2,MS51FB9AE帶隙電壓(Band-gap)比較低,1.17V ~ 1.27內3,如果我要偵測比較低的電壓(如50mV

2022-05-11 14:31:55

基準電壓源是工藝、電源電壓、溫度變化時能夠提供穩定輸出電壓的電路。基準電壓源廣泛應用于數據轉換器、智能傳感器、電源轉換器等電路。

基準電壓源設計的要點是精度高,溫度漂移小,帶隙基準電壓源利用硅的帶隙

2023-09-08 17:56:48

本帖最后由 萆嶶锝承鍩じ☆ve 于 2018-4-8 18:13 編輯

電壓基準芯片的分類 根據內部基準電壓產生結構不同,電壓基準分為:帶隙電壓基準和穩壓管電壓基準兩類。穩壓管電壓基準的基準

2018-04-08 17:19:22

你知道么,LT1461 和 LT1790 微功率低壓降帶隙電壓基準的過人之處不僅在于溫度系數 (TC) 和準確度,還在于長期漂移和遲滯(因為溫度的周期性變化而引起的輸出電壓漂移)。有時被其他制造商所

2019-08-02 06:36:09

電源電壓變化時,帶隙基準的輸出發生跳變,怎么減小帶隙基準的過沖?謝謝

2021-06-24 06:46:07

AD7674芯片使用外部基準電壓,在ADC工作的時候基準電壓對地值會被拉低,ADC不工作的時候恢復正常。ADC摘掉基準電壓也恢復正常。基準電壓芯片位REF02,推測它的帶載能力不夠,在后面加了電壓跟隨電路。加入電壓跟隨電路后,基準電壓正常工作,跟隨電路輸出電壓會被拉低。請問如何解決?

2018-07-24 10:40:58

請問NUC029LAN帶隙電壓BandGap是多少?怎么獲取?看資料N76E003可以讀UID的最后兩個字節,但是讀029LAN的UID好像沒有包含這個信息,ADC通道7可以讀取一個BandGap

2018-11-01 09:57:36

最近diy制作一個USB電源電流表,使用的N76E003單片機,液晶屏顯示部分程序,也弄好了,就差adc采樣了,想利用內部帶隙電壓計算外部電壓值,不知道怎么計算,讀取UID最后兩個字,值為1663

2023-08-30 06:43:07

什么是帶隙電壓?

2020-12-23 07:27:58

請問仿真一個運放的輸入失調電壓是不是要做MC分析啊用在帶隙基準中的運放,對于帶隙基準的性能要求:-40~130溫度掃描,輸出電壓偏離小于3mv,電壓精度小于1mv,這樣的性能要求輸入失調電壓為多少?幾mv嗎,還是小于1mv?

2021-06-24 06:28:08

如何實現低電壓帶隙基準電壓源的設計?傳統帶隙基準電壓源的工作原理是什么?低電源帶隙基準電壓源的工作原理是什么?

2021-04-20 06:12:32

如何讀取實際N76E003帶隙電壓?

2020-12-22 06:30:34

我們可以知道帶隙通道是 27 ,但是使用了 ADC0 或 ADC1?我都試過了,模擬總是零。

2023-04-25 09:30:23

帶隙放大器電路作為運放使用,請問該運放的輸出阻抗與跨導怎么分析,有沒有相關的資料?

2021-06-23 07:51:30

各位大神,請問有沒有做過cadence的CMOS帶隙基準電路設計,或者CMOS四運算放大器設計(LM324),求各位幫幫忙,我快山窮水盡了

2020-05-17 23:32:07

電子鎮流器芯片。本設計還優化了啟動部分,使新的帶隙基準可以在短時間內順利啟動。 1 電路結構 1.1 基準核心 目前的基準核心可以有多種實現方案:混合電阻,Buck voltage

2018-10-10 16:52:05

),沒有加電容,就參照上面的電路設計了。讓我們再進一步的看一下REF50XX系列bandgap基準源的內部,如下圖,芯片內部有一個1.2V的帶隙基準,和一個用于設置精確輸出電壓的放大器。這兩個就是基準

2019-06-11 06:59:08

采用 6 引腳 SOT-23 封裝的 1.25V、4ppm/°C、100μA 串聯(帶隙)電壓基準

2022-12-22 15:08:50

2.048V、4ppm/°C、100μA、6 引腳 SOT-23 串聯(帶隙)電壓基準

2022-12-22 15:08:50

采用 3 引腳 SOT-23 封裝的 1.25V、50ppm/°C、50μA 輸入串聯(帶隙)電壓基準

2022-12-22 15:09:05

采用 3 引腳 SOT-23 封裝的 2.048V、50ppm/°C、50μA 輸入串聯(帶隙)電壓基準

2022-12-22 15:09:05

采用 3 引腳 SOT-23 封裝的 2.5V、50ppm/°C、50μA 輸入串聯(帶隙)電壓基準

2022-12-22 15:09:06

采用 3 引腳 SOT-23 封裝的 4.096V、50ppm/°C、50μA 輸入串聯(帶隙)電壓基準

2022-12-22 15:09:07

電壓基準是模擬集成電路的重要單元模塊,本文在0.35um BiCMOS 工藝下設計了一個帶隙基準電壓源。仿真結果表明,該基準源電路在典型情況下輸出電壓為1.16302V,在-45℃~105℃范圍

2010-01-11 11:42:05 31

31 ADR291和ADR292均為低噪聲、微功耗、精密基準電壓源,采用XFET?基準電壓源電路。與傳統的帶隙和嵌入式齊納二極管基準電壓源相比,全新的XFET架構在性能方面有明顯改進。具體包括:工作電流

2023-06-26 15:29:55

ADR291和ADR292均為低噪聲、微功耗、精密基準電壓源,采用XFET?基準電壓源電路。與傳統的帶隙和嵌入式齊納二極管基準電壓源相比,全新的XFET架構在性能方面有明顯改進。具體包括

2023-06-26 15:33:05

精密基準方波基準電壓源電路圖

2009-04-15 09:00:27 1216

1216

在模擬及數/模混合集成電路設計中,電壓基準是非常重要的電路模塊之一,而通過巧妙設計的帶隙電壓基準更是以其與電源電壓、工藝、溫度變化幾乎無關的特點,廣泛應用

2010-11-02 09:40:44 1729

1729

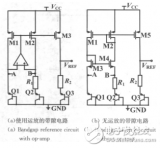

在數/模混合集成電路設計中電壓基準是重要的模塊之一。針對傳統電路產生的基準電壓易受電源電壓和溫度影響的缺點,提出一種新的設計方案,電路中不使用雙極晶體管,利用PMOS和

2012-10-10 16:38:05 4693

4693

本文為大家介紹一個cmos無運放帶隙基準源電路。

2018-01-11 16:52:50 14756

14756

電子發燒友App

電子發燒友App

評論