在移動(dòng)計(jì)算時(shí)代,片上系統(tǒng)(SoC)的設(shè)計(jì)已經(jīng)變得更為復(fù)雜,因?yàn)樵谠O(shè)計(jì)過程中面臨著諸多挑戰(zhàn),如需遵循針對(duì)高級(jí)流程節(jié)點(diǎn)的復(fù)雜設(shè)計(jì)規(guī)則,需采用低功率電路設(shè)計(jì)技術(shù),并放大電路的尺寸。電源完整性是設(shè)計(jì)方案能被成功簽核的關(guān)鍵因素之一。本文介紹了一種新的工具,與其他現(xiàn)有技術(shù)相比較,它不僅能將電源完整性分析與簽核的速度提高10倍,同時(shí)還能達(dá)到類似于集成電路通用模擬程序(SPICE)的準(zhǔn)確度。該工具將一套完整的設(shè)計(jì)實(shí)現(xiàn)和簽核工具整合到一起,以便更好地克服在簽核過程中遇到的挑戰(zhàn),從而實(shí)現(xiàn)業(yè)內(nèi)最快的設(shè)計(jì)收斂流程。

簡(jiǎn)介

為了滿足移動(dòng)計(jì)算的各種要求,片上系統(tǒng)的設(shè)計(jì)變得越來越復(fù)雜。隨著消費(fèi)者開始青睞更小巧、性能更好、電池續(xù)航時(shí)間更長的設(shè)備,設(shè)備中所使用的芯片必須能提供更豐富的功能,更低的能耗以及更小的尺寸。對(duì)設(shè)計(jì)工程師來說,這些變化意味著他們?cè)谠O(shè)計(jì)過程中必須運(yùn)用先進(jìn)的電源技術(shù)(例如電源控制開關(guān))、增加知識(shí)產(chǎn)權(quán)的內(nèi)容和功能(例如模擬/混合信號(hào)宏指令)以及減少設(shè)計(jì)裕度(例如電源電壓小于1V)。另一方面,產(chǎn)品上市周期變得越來越短,因此在設(shè)計(jì)周期的最后階段,電源簽核對(duì)成功將設(shè)計(jì)方案送交制造來說至關(guān)重要。

至今,可用的電源簽核技術(shù)仍未能跟上創(chuàng)新的步伐。例如,一直以來額外的運(yùn)行時(shí)間都是妨礙設(shè)計(jì)者們完整而全面地進(jìn)行電源完整性分析和優(yōu)化的一個(gè)瓶頸。然而,現(xiàn)在有一種新工具可以解決這個(gè)問題,它利用先進(jìn)的大規(guī)模并行算法和分層結(jié)構(gòu)將電源完整性分析和簽核的速度提高到原來的10倍,同時(shí)還能達(dá)到類似于SPICE 的準(zhǔn)確度。另外,作為從芯片到系統(tǒng)的整套流程中的一部分,該工具通過提高整個(gè)設(shè)計(jì)周期的生產(chǎn)力而加速設(shè)計(jì)收斂流程。

日益復(fù)雜的產(chǎn)品設(shè)計(jì)亟需電源完整性分析新工具

產(chǎn)品設(shè)計(jì)的復(fù)雜度越來越高,產(chǎn)品尺寸越來越小,而且對(duì)產(chǎn)品分析的要求也越來越復(fù)雜,這增加了完成電源完整性分析和簽核所需的時(shí)間。如果使用“平面”設(shè)計(jì)方法把設(shè)計(jì)拉平成為高級(jí)別的一層,則不足以分析擁有數(shù)億實(shí)例的超大規(guī)模設(shè)計(jì)。當(dāng)前的解決方案趨向于將設(shè)計(jì)分析劃分成與“單點(diǎn)工具”對(duì)應(yīng)的多個(gè)部分,這些工具在準(zhǔn)確性或易用性方面并不能達(dá)到高級(jí)片上系統(tǒng)的要求。

另外,由于當(dāng)前的解決方案是使用單點(diǎn)工具,因此無法有效地評(píng)估電源對(duì)時(shí)序收斂的影響,而時(shí)序?qū)﹄娫矗╒DD)卻是最為敏感的。此外,高級(jí)節(jié)點(diǎn)設(shè)計(jì)技術(shù)及技巧(如FinFET工藝和三維芯片(3D-IC)封裝)也帶來了新的挑戰(zhàn)。例如,隨著FinFET器件的部署,會(huì)因?yàn)榇怪?a href="http://www.xsypw.cn/tags/電流/" target="_blank">電流方向、功率密度增加等因素而產(chǎn)生新的電遷移規(guī)則。而隨著三維堆疊式芯片的部署,會(huì)有電熱協(xié)同仿真的新需求。為了讓設(shè)計(jì)工程師們滿足上市周期和產(chǎn)品質(zhì)量的相關(guān)要求,需要一個(gè)涵蓋芯片、封裝以及系統(tǒng)的完整電源完整性分析方案。

完美的電源完整性分析工具需具備哪些功能?

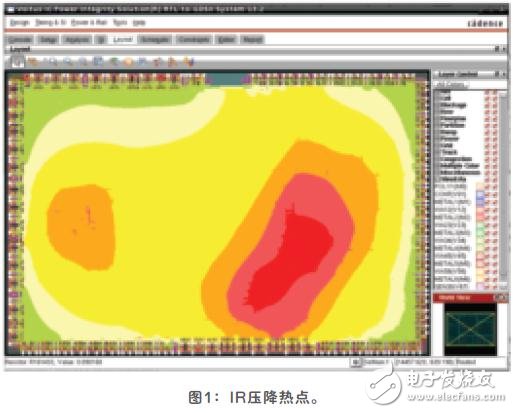

當(dāng)出現(xiàn)漏泄增加、溫度變化,或者由于靜態(tài)和動(dòng)態(tài)IR壓降造成工作電壓下降等場(chǎng)景時(shí),一項(xiàng)設(shè)計(jì)可能失敗。無論是對(duì)于數(shù)百萬門級(jí)設(shè)計(jì)還是對(duì)于多顆裸晶而言,能在設(shè)計(jì)早期階段就對(duì)電源和IR壓降約束進(jìn)行調(diào)試并證實(shí)其符合要求,是節(jié)約寶貴的開發(fā)成本和時(shí)間的關(guān)鍵。換句話說,盡早找到芯片上的“熱點(diǎn)”有助于防止芯片性能下降(圖1)。

為了能更好地支持高級(jí)片上系統(tǒng)設(shè)計(jì),完美的電源完整性分析工具應(yīng)具備以下功能:

● 能計(jì)算芯片上的漏泄以及開關(guān)和內(nèi)部耗能;

● 能對(duì)電源網(wǎng)絡(luò)的電源完整性進(jìn)行分析(IR壓降檢測(cè)及電遷移檢測(cè));

● 能就電路中去耦電容單元和電源控制開關(guān)的最佳尺寸和布置方式提供建議,從而對(duì)設(shè)計(jì)方案中的物理實(shí)現(xiàn)電流進(jìn)行優(yōu)化;

● 能評(píng)估IR壓降對(duì)包括靜態(tài)時(shí)序分析在內(nèi)的設(shè)計(jì)收斂的影響。

利用在生產(chǎn)過程中已得到驗(yàn)證的和具備簽核質(zhì)量的算法和引擎,Cadence公司開發(fā)出了一種既能覆蓋整個(gè)芯片又能顧及芯片上所有單元的新型電源完整性分析工具(即Voltus集成電路電源完整性分析解決方案),該工具能提供上述所有功能。它的分析速度比其他同類解決方案快10倍,同時(shí)還提供了類似于 SPICE的準(zhǔn)確度。此外,***積體電路制造股份有限公司(TSMC)已經(jīng)通過16nm級(jí)FinFET工藝對(duì)這種工具的性能進(jìn)行了驗(yàn)證。因此,工程師們可以相信該工具能夠跨越不同的設(shè)計(jì)規(guī)則而給出準(zhǔn)確的分析結(jié)果。

大規(guī)模并行處理可加快分析速度

與現(xiàn)有的其他技術(shù)相比較,Voltus集成電路電源完整性分析解決方案在性能、準(zhǔn)確度和設(shè)計(jì)收斂方面均有所提高。在性能方面,該工具使用先進(jìn)的大規(guī)模并行算法,從而使分析速度比同類解決方案快10倍。

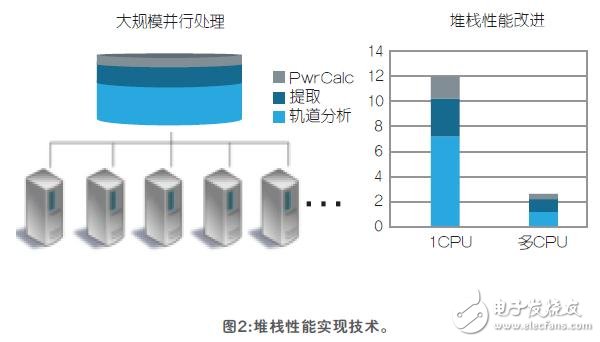

為了進(jìn)一步體現(xiàn)這種工具的快速分析性能,下面將以早期測(cè)試版客戶提供的位于高級(jí)流程節(jié)點(diǎn)的擁有數(shù)億實(shí)例的超大規(guī)模設(shè)計(jì)場(chǎng)景為例。在對(duì)這樣的超大規(guī)模設(shè)計(jì)進(jìn)行分析時(shí),如果運(yùn)用現(xiàn)有的生產(chǎn)流程,分層的靜態(tài)和動(dòng)態(tài)電源簽核需要10天左右才能完成;如果采用Voltus集成電路電源完整性分析解決方案,則可以在32 個(gè)CPU上同時(shí)進(jìn)行分析操作,僅耗時(shí)26個(gè)小時(shí)就可以完成分析工作—速度比原來提高了10倍左右,因此可以提前將設(shè)計(jì)方案送交制造(圖2)。

來看一個(gè)靜態(tài)功率分析的案例,在該案例中采用了一個(gè)在40nm級(jí)節(jié)點(diǎn)擁有2700萬個(gè)實(shí)例的模擬/混合信號(hào)芯片。如果利用現(xiàn)有的生產(chǎn)流程,要完成分析將需要 58個(gè)小時(shí)。而如果利用Voltus集成電路電源完整性分析解決方案,則可在8個(gè)CPU上同時(shí)進(jìn)行分析操作,僅耗時(shí)6個(gè)小時(shí)就可以完成分析工作,速度提高了10倍左右,并且不會(huì)降低準(zhǔn)確度。

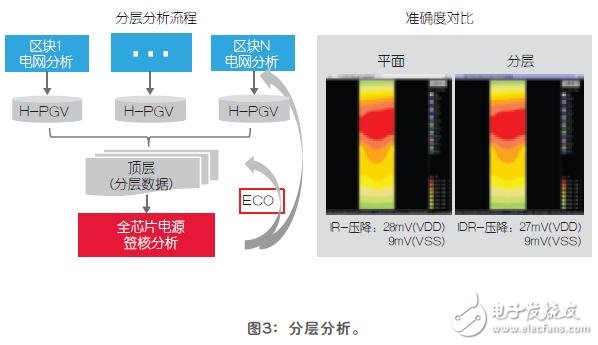

該工具采用了分層結(jié)構(gòu),而且分析性能卓越,可以通過計(jì)算機(jī)網(wǎng)絡(luò)進(jìn)行計(jì)算而且容量非常大 (最多可以支持10億個(gè)實(shí)例)。例如,如果一臺(tái)單機(jī)配有16個(gè)CPU,Voltus集成電路電源完整性分析解決方案可在這些CPU上同時(shí)進(jìn)行分析操作。如果單機(jī)的數(shù)量不止一臺(tái),每臺(tái)單機(jī)都有多個(gè)CPU,而且這些單機(jī)連接形成了一個(gè)網(wǎng)絡(luò),該工具仍然可以使用其多線程分布式處理技術(shù)支持快速電源分析計(jì)算。通過分層方法,工程師可以建立電源網(wǎng)絡(luò)模型,這是設(shè)計(jì)層次中較低層的部分,目的是獲取所關(guān)注的電源網(wǎng)絡(luò)信息。這一模型減小了從頂層所看到的節(jié)點(diǎn)總數(shù),鑒于此,與同類解決方案相比,工程師在分析過程中可以運(yùn)行更多的設(shè)計(jì)實(shí)例(圖3)。

在設(shè)計(jì)收斂方面,Voltus工具在早期底層規(guī)劃和電源規(guī)劃階段對(duì)電源軌進(jìn)行分析,以便通過布線布局、工程變更指令(ECO)和芯片與系統(tǒng)的協(xié)同設(shè)計(jì)分析在物理上對(duì)電源網(wǎng)絡(luò)進(jìn)行優(yōu)化。在準(zhǔn)確度方面,Voltus集成電路電源完整性分析解決方案采用SPICE級(jí)的軌矩陣解算法以及精確的電源網(wǎng)絡(luò)電阻電容萃取和實(shí)例功率計(jì)算/分布。軌矩陣解算法較為復(fù)雜,可以在分布在多臺(tái)設(shè)備上的幾十個(gè)CPU上同時(shí)進(jìn)行,提供大型電源網(wǎng)絡(luò)的高準(zhǔn)確度模擬。

整個(gè)簽核流程的一部分

Voltus集成電路電源完整性分析解決方案是Cadence公司提供整個(gè)簽核和設(shè)計(jì)收斂流程的一部分。該工具的作用與獨(dú)立的電源簽核工具類似。但它集成了很多其他組件,給設(shè)計(jì)工程師們提供了一個(gè)從芯片到系統(tǒng)的多產(chǎn)快速的設(shè)計(jì)收斂流程。

早期電源軌分析

在傳統(tǒng)的設(shè)計(jì)流程中,工程師布完線之后,會(huì)進(jìn)行電源簽核分析,以評(píng)估電源網(wǎng)絡(luò)設(shè)計(jì)方案的可行性。但是,如果在布完線之后才對(duì)設(shè)計(jì)方案的電源完整性進(jìn)行分析,而且在分析之后發(fā)現(xiàn)了問題,則需要耗費(fèi)更長的時(shí)間來解決問題,甚至可能無法解決。Voltus集成電路電源完整性分析解決方案可以避免上述問題,因?yàn)樗瑫r(shí)還集成了Cadence Encounter數(shù)字實(shí)現(xiàn)系統(tǒng),使設(shè)計(jì)工程師們可以將電源網(wǎng)絡(luò)設(shè)計(jì)挪到物理實(shí)現(xiàn)的早期階段。早期電源軌分析考慮了底層規(guī)劃信息,以及電源網(wǎng)絡(luò)金屬元件的大小和位置。如果工程師必須將兩個(gè)功能區(qū)塊放到一起(而且兩個(gè)區(qū)塊均十分活躍),則該集成解決方案可以提供關(guān)于如何實(shí)現(xiàn)最佳布線的指導(dǎo)建議。良好的早期軌分析結(jié)果將會(huì)推進(jìn)電源簽核,更快地匯聚,從而加快設(shè)計(jì)收斂。

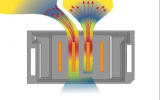

現(xiàn)實(shí)環(huán)境中的峰值功率分析

如果像IR壓降和電遷移這樣的電源完整性問題沒有得到解決,可能會(huì)導(dǎo)致硅故障。通過在現(xiàn)實(shí)環(huán)境中進(jìn)行電刺激分析可以提高分析結(jié)果的準(zhǔn)確性,特別是在長時(shí)間內(nèi)考量芯片的行為,以及在活躍度增加的情況下觀察峰值功率消耗發(fā)生的位置時(shí)更是如此。

Cadence公司Palladium平臺(tái)提供的“深循環(huán)”動(dòng)態(tài)功率分析(DPA)功能支持在現(xiàn)實(shí)環(huán)境中進(jìn)行電刺激分析,得益于此,Cadence Palladium仿真技術(shù)與Voltus解決方案的結(jié)合能夠?qū)崿F(xiàn)高準(zhǔn)確度的集成電路電源完整性分析(圖4)。

統(tǒng)一的電子簽核

時(shí)序?qū)﹄娫醋顬槊舾小R虼耍绻娫淳W(wǎng)絡(luò)實(shí)例中缺乏準(zhǔn)確有效的電源值則會(huì)引發(fā)設(shè)計(jì)防護(hù)頻帶,也就增加了靜態(tài)時(shí)序中的負(fù)面因素。由于Voltus集成電路電源完整性分析解決方案集成了CadenceTempus時(shí)序簽核解決方案,設(shè)計(jì)工程師們就可以使用統(tǒng)一的功率和時(shí)序分析收斂系統(tǒng)。集成解決方案將靜態(tài)時(shí)序分析的準(zhǔn)確率提高了3個(gè)百分點(diǎn),減少了時(shí)序中的負(fù)面因素,并且在芯片上生成了更符合現(xiàn)實(shí)使用環(huán)境的壓降。

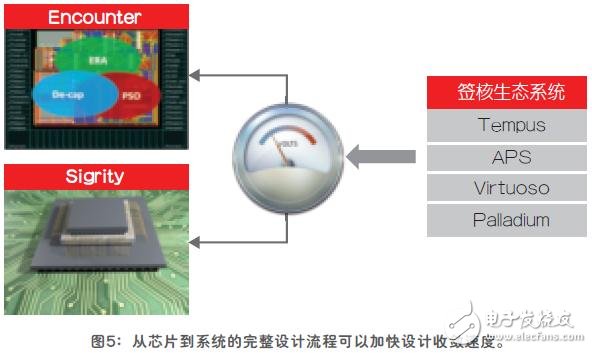

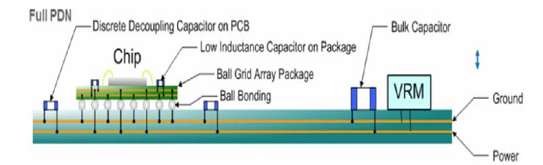

芯片-封裝-印刷電路板協(xié)同仿真與分析

為了防止封裝過程中的熱崩潰以及在芯片上和在印刷電路板階段出現(xiàn)的其他電源完整性問題,該工具集成了Cadence Allegro Sigrity技術(shù),提供芯片-封裝-印刷電路板協(xié)同仿真與分析功能。該集成解決方案提供了針對(duì)電源網(wǎng)絡(luò)中芯片和電路板的準(zhǔn)確分析,同時(shí)還支持像三維芯片那樣的先進(jìn)封裝技術(shù)。通過同時(shí)使用這些工具,工程師們就能夠加快系統(tǒng)級(jí)電源完整性分析和簽核的速度(圖5)。

總結(jié)

復(fù)雜度更高、耗時(shí)更長的電源完整性分析需要采用更高效的分析工具。人們對(duì)移動(dòng)應(yīng)用及物聯(lián)網(wǎng)應(yīng)用的需求對(duì)產(chǎn)品的上市周期和性能提出了更高的要求。通過使用先進(jìn)的大規(guī)模并行算法、大容量分析(最多能支持10億個(gè)實(shí)例)和分層結(jié)構(gòu),Voltus集成電路電源完整性分析解決方案的電源簽核速度比同類解決方案快10 倍。該解決方案集成了其他關(guān)鍵的時(shí)序分析、物理實(shí)現(xiàn)、仿真和封裝工具,形成了一個(gè)簽核生態(tài)系統(tǒng),為業(yè)界提供了最快的設(shè)計(jì)收斂流程。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論