用VHDL語言實現3分頻電路

標簽/分類:

眾所周知,分頻器是FPGA設計中使用頻率非常高的基本設計之一,盡管在目前大部分設計中,廣泛使用芯片廠家集成的鎖相環資源,如altera 的PLL,Xilinx的DLL.來進行時鐘的分頻,倍頻以及相移。但是對于時鐘要求不高的基本設計,通過語言進行時鐘的分頻相移仍然非常流行,首先這種方法可以節省芯片內部的鎖相環資源,再者,消耗不多的邏輯單元就可以達到對時鐘操作的目的。另一方面,通過語言設計進行時鐘分頻,可以看出設計者對設計語言的理解程度。因此很多招聘單位在招聘時往往要求應聘者寫一個分頻器(比如奇數分頻)以考核應聘人員的設計水平和理解程度。下面講講對各種分頻系數進行分頻的方法:

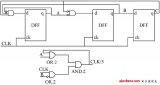

第一,偶數倍分頻:偶數倍分頻應該是大家都比較熟悉的分頻,通過計數器計數是完全可以實現的。如進行N倍偶數分頻,那么可以通過由待分頻的時鐘觸發計數器計數,當計數器從0計數到N/2-1時,輸出時鐘進行翻轉,并給計數器一個復位信號,使得下一個時鐘從零開始計數。以此循環下去。這種方法可以實現任意的偶數分頻。

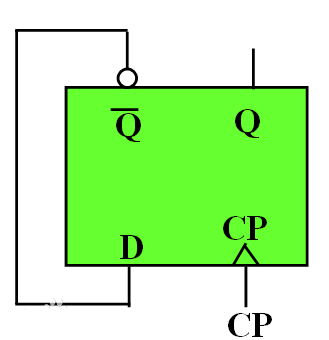

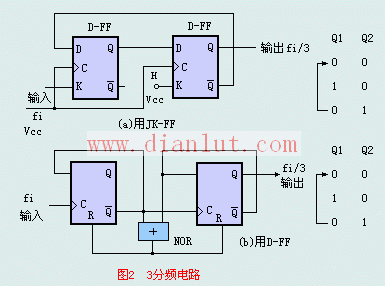

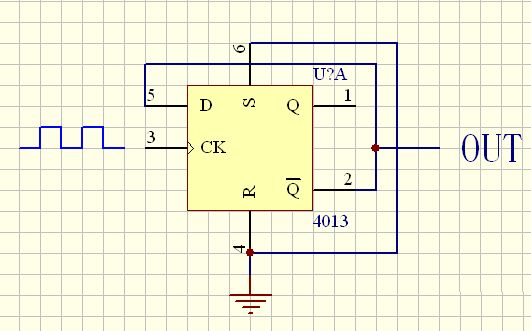

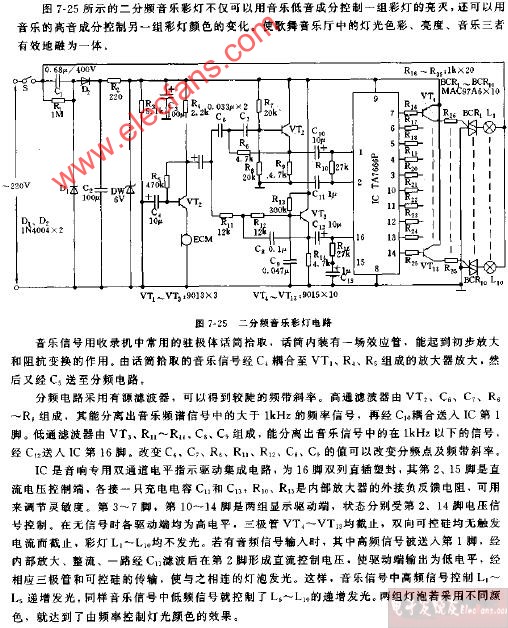

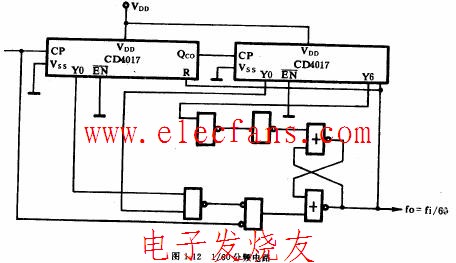

第二:奇數倍分頻:奇數倍分頻常常在論壇上有人問起,實際上,奇數倍分頻有兩種實現方法:首先,完全可以通過計數器來實現,如進行三分頻,通過待分頻時鐘上升沿觸發計數器進行模三計數,當計數器計數到鄰近值進行兩次翻轉,比如可以在計數器計數到1時,輸出時鐘進行翻轉,計數到2時再次進行翻轉。即是在計數值在鄰近的1和2進行了兩次翻轉。這樣實現的三分頻占空比為1/3或者2/3。如果要實現占空比為50%的三分頻時鐘,可以通過待分頻時鐘下降沿觸發計數,和上升沿同樣的方法計數進行三分頻,然后下降沿產生的三分頻時鐘和上升沿產生的時鐘進行相或運算,即可得到占空比為50%的三分頻時鐘。這種方法可以實現任意的奇數分頻。歸類為一般的方法為:對于實現占空比為50%的N倍奇數分頻,首先進行上升沿觸發進行模N計數,計數選定到某一個值進行輸出時鐘翻轉,然后經過(N-1)/2再次進行翻轉得到一個占空比非50%奇數n分頻時鐘。再者同時進行下降沿觸發的模N計數,到和上升沿觸發輸出時鐘翻轉選定值相同值時,進行輸出時鐘時鐘翻轉,同樣經過(N-1)/2時,輸出時鐘再次翻轉生成占空比非50%的奇數n分頻時鐘。兩個占空比非50%的n分頻時鐘相或運算,得到占空比為50%的奇數n分頻時鐘。另外一種方法:對進行奇數倍n分頻時鐘,首先進行n/2分頻(帶小數,即等于(n-1)/2+0.5),然后再進行二分頻得到。得到占空比為50%的奇數倍分頻。下面講講進行小數分頻的設計方法

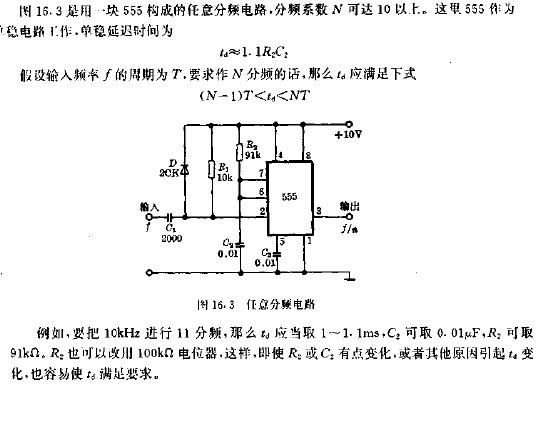

第三 ,小數分頻:首先講講如何進行n+0.5分頻,這種分頻需要對輸入時鐘進行操作。基本的設計思想:對于進行n+0.5分頻,首先進行模n的計數,在計數到n-1時,輸出時鐘賦為‘1’,回到計數0時,又賦為0,因此,可以知道,當計數值為n-1時,輸出時鐘才為1,因此,只要保持計數值n-1為半個輸入時鐘周期,即實現了n+0.5分頻時鐘,因此保持n-1為半個時鐘周期即是一個難點。從中可以發現,因為計數器是通過時鐘上升沿計數,因此可以在計數為n-1時對計數觸發時鐘進行翻轉,那么時鐘的下降沿變成了上升沿。即在計數值為n-1期間的時鐘下降沿變成了上升沿,則計數值n-1只保持了半個時鐘周期,由于時鐘翻轉下降沿變成上升沿,因此計數值變為0。因此,每產生一個n+0.5分頻時鐘的周期,觸發時鐘都是要翻轉一次.

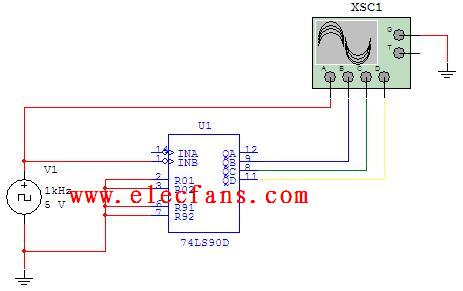

下面是根據上面思想寫的三分頻程序,1/3和50%占空比的程序.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

--? Uncomment the following lines to use the declarations that are

--? provided for instantiating Xilinx primitive components.

--library UNISIM;

--use UNISIM.VComponents.all;

entity division3 is

? port (clk: in std_logic;

??????? out1: out std_logic);

end division3;

architecture Behavioral of division3 is

?signal division2,division4 :std_logic:='0';

?signal temp1,temp2:integer range 0 to 10;

?

begin

?p1:process(clk)

??begin

???if rising_edge(clk) then

????temp1 <=temp1+1;

????if temp1=1 then

?????division2<='1';

????elsif temp1=2 then

?????? division2<='0';

?????temp1<=0;

????end if;

????? end if;

?end process p1;

?p2:process(clk)

??begin

??if clk'event and clk='0' then

????temp2<=temp2+1;

?????if temp2=1 then

??

??????division4<='1';

?????elsif temp2=2 then

??????division4<='0';

??????temp2<=0;

????end if;

??? end if;

?? end process p2;

?p3:process(division2,division4)

?begin

???out1<=division2 or division4;

?end process p3;

?

end Behavioral; (50%)

把上面的部分截取就可以得到異步的.

電子發燒友App

電子發燒友App

評論