電子鐘VHDL設計

電子鐘VHDL設計

標簽/分類:

1.系統設計要求

???(1)具有時、分、秒計數顯示功能,小時為24進制,分鐘和秒為60進制。

??(2)可以根據需要設置復位、清零、置位等功能。

2.系統設計方案概述

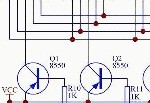

???根據系統設計要求,系統設計采用自頂向下設計方法,由秒計數模塊、分計數模塊、時計數模塊、時間設置模塊和譯碼模塊五部分組成。

3.參考VHDL源程序

??(1)秒計數模塊的VHDL源程序(second.vhd)

library?ieee;

use?ieee.std_logic_1164.all;

use?ieee.std_logic_unsigned.all;

entity?second?is

??port(clk,reset,semin:in?std_logic;

????????enmin:out?std_logic;

????????daout:out?std_logic_vector(6?downto?0));

end?second;

architecture?rtl?of?second?is

????signal?count:std_logic_vector(6?downto?0);

????signal?enmin_1,enmin_2:std_logic;

????begin

??????daout<=count;

??????enmin_2<=(semin?and?clk);

??????enmin<=(enmin_1?or?enmin_2);

??????process(clk,reset,semin)

?????????begin

???????????if(reset='0')then

??????????????count<="0000000";

??????????????enmin_1<='0';

???????????elsif(clk'event?and?clk='1')then

??????????????if(count(3?downto?0)="1001"screen.width/2)this.style.width=screen.width/2;" border=0>then

?????????????????if(count<16#60#)then

?????????????????????if(count="1011001"screen.width/2)this.style.width=screen.width/2;" border=0>then

????????????????????????enmin_1<='1';count<="0000000";

?????????????????????else

?????????????????????????count<=count+7;

?????????????????????end?if;

?????????????????else

????????????????????count<="0000000";

?????????????????end?if;

??????????????elsif(count<16#60#)then

?????????????????count<=count+1;

?????????????????enmin_1<='0';

??????????????else

?????????????????count<="0000000";enmin_1<='0';

??????????????end?if;

???????????end?if;

???????end?process;

?end?rtl;

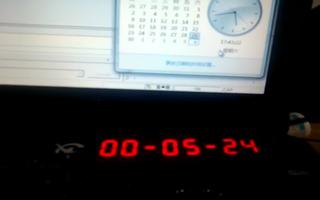

仿真:?

(2)分計數模塊VHDL程序(minute.vhd)

library?ieee;

use?ieee.std_logic_1164.all;

use?ieee.std_logic_unsigned.all;

entity?minute?is

??port(clk,reset,clks,sethour:in?std_logic;

????????enhour:out?std_logic;

????????daout:out?std_logic_vector(6?downto?0));

end?minute;

architecture?rtl?of?minute?is

????signal?count:std_logic_vector(6?downto?0);

????signal?enhour_1,enhour_2:std_logic;

????begin

??????daout<=count;

??????enhour_2<=(sethour?and?clk);

??????enhour<=(enhour_1?or?enhour_2);

??????process(clk,reset,sethour)

?????????begin

???????????if(reset='0')then

??????????????count<="0000000";

??????????????enhour_1<='0';

???????????elsif(clk'event?and?clk='1')then

??????????????if(count(3?downto?0)="1001"screen.width/2)this.style.width=screen.width/2;" border=0>then

?????????????????if(count<16#60#)then

?????????????????????if(count="1011001"screen.width/2)this.style.width=screen.width/2;" border=0>then

????????????????????????enhour_1<='1';count<="0000000";

?????????????????????else

?????????????????????????count<=count+7;

?????????????????????????enhour_1<='0';

?????????????????????end?if;

?????????????????else

????????????????????count<="0000000";

?????????????????end?if;

??????????????elsif(count<16#60#)then

?????????????????count<=count+1;

?????????????????enhour_1<='0'?after?100?ns;

??????????????else

?????????????????count<="0000000";enhour_1<='0';

??????????????end?if;

???????????end?if;

???????end?process;

?end?rtl;

仿真?

(3)時計數模塊VHDL源程序(hour.vhd)

library?ieee;

use?ieee.std_logic_1164.all;

use?ieee.std_logic_unsigned.all;

entity?hour?is

??port(clk,reset:in?std_logic;

???????daout:out?std_logic_vector(5?downto?0));

end?hour;

architecture?rtl?of?hour?is

????signal?count:std_logic_vector(5?downto?0);

????????begin

??????daout<=count;

??????process(clk,reset)

????????begin

???????????if(reset='0')then

??????????????count<="000000";

??????????????

???????????elsif(clk'event?and?clk='1')then

??????????????if(count(3?downto?0)="1001"screen.width/2)this.style.width=screen.width/2;" border=0>then

?????????????????if(count<16#23#)then

????????????????????count<=count+7;

?????????????????else

????????????????????count<="000000";

?????????????????end?if;

??????????????elsif(count<16#23#)then

?????????????????count<=count+1;

??????????????else

?????????????????count<="000000";

??????????????end?if;

???????????end?if;

???????end?process;

?end?rtl;

仿真?

(4)時間設置模塊VHDL程序(settime.vhd)

library?ieee;

use?ieee.std_logic_1164.all;

use?ieee.std_logic_unsigned.all;

use?ieee.std_logic_arith.all;

entity?settime?is

??port(clk,reset:in?std_logic;

????????sec,min:in?std_logic_vector(6?downto?0);

????????hour:in?std_logic_vector(5?downto?0);

????????dp:out?std_logic;

????????sel:out?std_logic_vector(5?downto?0);

????????daout:out?std_logic_vector(3?downto?0));

end?settime;

architecture?rtl?of?settime?is

????signal?count:std_logic_vector(2?downto?0);

????begin

????process(clk,reset)

?????????begin

???????????if(reset='0')then

??????????????count<="000";

???????????elsif(clk'event?and?clk='1')then

??????????????if(count>="101"screen.width/2)this.style.width=screen.width/2;" border=0>then

?????????????????count<="000";

??????????????else

?????????????????count<=count+1;

??????????????end?if;

??????????????

???????????end?if;

????end?process;

????process(clk,reset)

????????begin

???????????if(reset='0')then

??????????????daout<="0000";

??????????????dp<='0';

??????????????sel<="111111";

???????????elsif(clk'event?and?clk='1')then

????????????case?count?is

??????????????when"000"=>daout<=sec(3?downto?0);

?????????????????????????dp<='0';

?????????????????????????sel<="111110";

??????????????when"001"=>daout(3)<='0';

?????????????????????????daout(2?downto?0)<=sec(6?downto?4);

?????????????????????????dp<='0';

?????????????????????????sel<="111101";

??????????????when"010"=>daout<=min(3?downto?0);

?????????????????????????dp<='1';

?????????????????????????sel<="111011";

??????????????when"011"=>daout(3)<='0';

?????????????????????????daout(2?downto?0)<=min(6?downto?4);

?????????????????????????dp<='0';

?????????????????????????sel<="110111";

??????????????when"100"=>daout<=hour(3?downto?0);

?????????????????????????dp<='1';

?????????????????????????sel<="101111";

??????????????when"101"=>daout(3?downto?2)<="00";

?????????????????????????daout(1?downto?0)<=hour(5?downto?4);

?????????????????????????dp<='0';

?????????????????????????sel<="011111";

??????????????when?others=>daout<="0000";

???????????????????????????dp<='0';

???????????????????????????sel<="111111";

????????????end?case;

?????????end?if;

??????end?process;

end?rtl;

仿真?

(5)譯碼顯示模塊的VHDL程序(deled.vhd)

library?ieee;

use?ieee.std_logic_1164.all;

use?ieee.std_logic_unsigned.all;

entity?deled?is?

port(num:?in?std_logic_vector(3?downto?0);

?????led:?out?std_logic_vector(6?downto?0));

end?deled;

architecture?rtl?of?deled?is?

?begin?

??????led<="1111110"when?num="0000"else

???????????"0110000"when?num="0001"else

???????????"1101101"when?num="0010"else

???????????"1111001"when?num="0011"else

???????????"0110011"when?num="0100"else

???????????"1011011"when?num="0101"else

???????????"1011111"when?num="0110"else

???????????"1110000"when?num="0111"else

???????????"1111111"when?num="1000"else

???????????"1111011"when?num="1001"else

???????????"1110111"when?num="1010"else

???????????"0011111"when?num="1011"else

???????????"1001110"when?num="1100"else

???????????"0111101"when?num="1101"else

???????????"1001111"when?num="1110"else

???????????"1000111"when?num="1111";

??end?rtl;

電子發燒友App

電子發燒友App

評論