a) 什么是Setup 和Holdup時(shí)間?

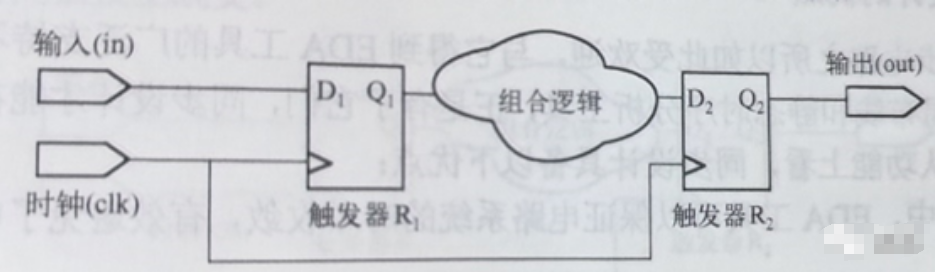

建立時(shí)間(setup time)是指在觸發(fā)器的時(shí)鐘信號(hào)上升沿到來(lái)以前,數(shù)據(jù)穩(wěn)定不變的時(shí)間,如果建立時(shí)間不夠,數(shù)據(jù)將不能在這個(gè)時(shí)鐘上升沿被打入觸發(fā)器;保持時(shí)間(hold time)是指在觸發(fā)器的時(shí)鐘信號(hào)上升沿到來(lái)以后,數(shù)據(jù)穩(wěn)定不變的時(shí)間, 如果保持時(shí)間不夠,數(shù)據(jù)同樣不能被打入觸發(fā)器。

b) 什么是競(jìng)爭(zhēng)與冒險(xiǎn)現(xiàn)象?怎樣判斷?如何消除?

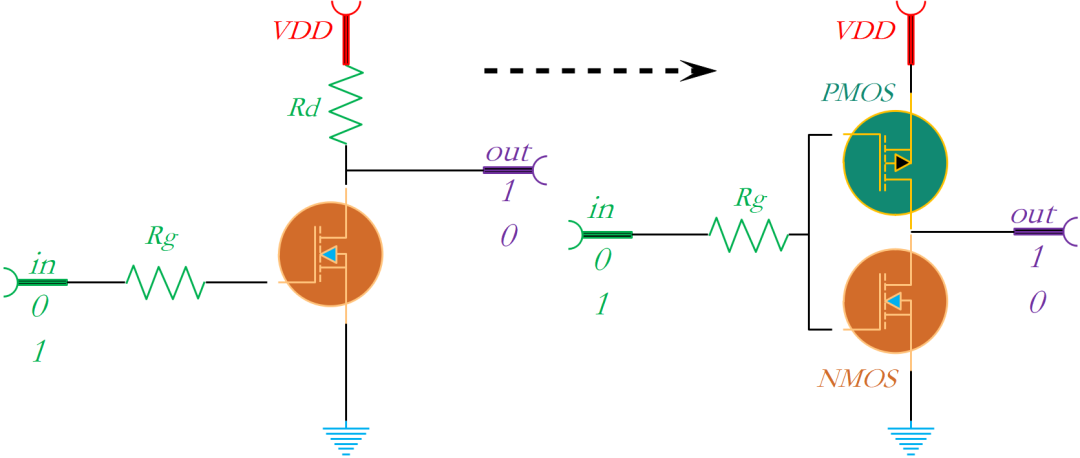

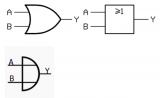

信號(hào)在FPGA器件內(nèi)部通過連線和邏輯單元時(shí),都有一定的延時(shí)。延時(shí)的大小與連線的長(zhǎng)短和邏輯單元的數(shù)目有關(guān),同時(shí)還受器件的制造工藝、工作電壓、溫度等條件的影響。信號(hào)的高低電平轉(zhuǎn)換也需要一定的過渡時(shí)間。由于存在這兩方面因素,多路信號(hào)的電平值發(fā)生變化時(shí),在信號(hào)變化的瞬間,組合邏輯的輸出有先后順序,并不是同時(shí)變化,往往會(huì)出現(xiàn)一些不正確的尖峰信號(hào),這些尖峰信號(hào)稱為"毛刺"。如果一個(gè)組合邏輯電路中有"毛刺"出現(xiàn),就說(shuō)明該電路存在"冒險(xiǎn)"。用D觸發(fā)器,格雷碼計(jì)數(shù)器,同步電路等優(yōu)秀的設(shè)計(jì)方案可以消除。

c) 請(qǐng)畫出用D觸發(fā)器實(shí)現(xiàn)2倍分頻的邏輯電路?

就是把D觸發(fā)器的輸出端加非門接到D端。

d) 什么是"線與"邏輯,要實(shí)現(xiàn)它,在硬件特性上有什么具體要求?

將幾個(gè)OC門結(jié)構(gòu)與非門輸出并聯(lián),當(dāng)每個(gè)OC門輸出為高電平時(shí),總輸出才為高,這種連接方式稱為線與。

e) 什么是同步邏輯和異步邏輯?

整個(gè)設(shè)計(jì)中只有一個(gè)全局時(shí)鐘成為同步邏輯。

多時(shí)鐘系統(tǒng)邏輯設(shè)計(jì)成為異步邏輯。

f) 請(qǐng)畫出微機(jī)接口電路中,典型的輸入設(shè)備與微機(jī)接口邏輯示意圖(數(shù)據(jù)接口、控制接口、所存器/緩沖器)。

是不是結(jié)構(gòu)圖?

g) 你知道那些常用邏輯電平?TTL與COMS電平可以直接互連嗎?

TTL,cmos,不能直連

LVDS:LVDS(Low Voltage Differential Signal)即低電壓差分信號(hào),LVDS接口又稱RS644總線接口,是20世紀(jì)90年代才出現(xiàn)的一種數(shù)據(jù)傳輸和接口技術(shù)。

ECL:(EmitterCoupled Logic)即射極耦合邏輯,是帶有射隨輸出結(jié)構(gòu)的典型輸入輸出接口電路

CML: CML電平是所有高速數(shù)據(jù)接口中最簡(jiǎn)單的一種。其輸入和輸出是匹配好的,減少了外圍器件,適合于更高頻段工作。

什么是同步邏輯和異步邏輯?

相關(guān)推薦

用邏輯筆測(cè)量信號(hào)的邏輯狀態(tài)屬于?

用邏輯筆測(cè)量信號(hào)的邏輯狀態(tài)屬于?? 信號(hào)的邏輯狀態(tài)是指該信號(hào)所表達(dá)的信息在邏輯上的真假性質(zhì),即1或0的狀態(tài)。在數(shù)字電路設(shè)計(jì)中,邏輯狀態(tài)是非常重要的概念,因?yàn)橹挥姓_地確定信號(hào)的邏輯狀態(tài),才能正確地

2023-09-19 17:16:11 110

110

110

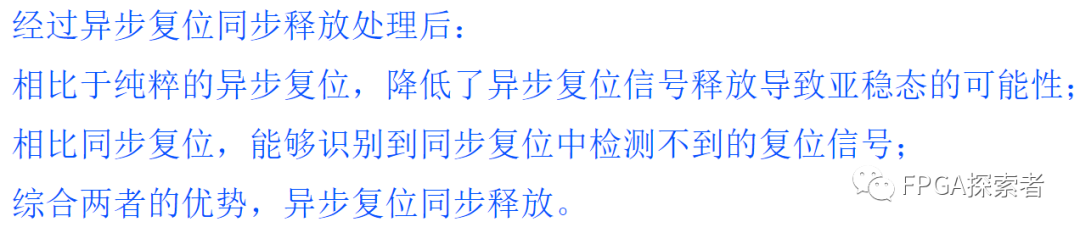

110FPGA學(xué)習(xí)-異步復(fù)位,同步釋放

點(diǎn)擊上方 藍(lán)字 關(guān)注我們 系統(tǒng)的復(fù)位對(duì)于系統(tǒng)穩(wěn)定工作至關(guān)重要,最佳的復(fù)位方式為:異步復(fù)位,同步釋放。以下是轉(zhuǎn)載博客,原文標(biāo)題及鏈接如下: 復(fù)位最佳方式:異步復(fù)位,同步釋放 異步復(fù)位; 異步

2023-09-09 14:15:01 124

124

124

124

異步邏輯器件之反相器、緩沖器(驅(qū)動(dòng)器)和收發(fā)器

引言:在異步邏輯器件中,信號(hào)不與時(shí)鐘信號(hào)同步,或者說(shuō)該信號(hào)壓根就沒有對(duì)位的時(shí)鐘信號(hào)。本節(jié)簡(jiǎn)述基本的異步邏輯--->1位拓?fù)浜投辔煌負(fù)涞木彌_器、反相器、驅(qū)動(dòng)器和收發(fā)器。

2023-09-04 15:59:03 356

356

356

356

soc中的組合邏輯和時(shí)序邏輯應(yīng)用說(shuō)明

芯片設(shè)計(jì)是現(xiàn)代電子設(shè)備的重要組成部分,其中組合邏輯和時(shí)序邏輯是芯片設(shè)計(jì)中非常重要的概念。組合邏輯和時(shí)序邏輯的設(shè)計(jì)對(duì)于構(gòu)建復(fù)雜的電路系統(tǒng)至關(guān)重要。

2023-08-30 09:32:15 511

511

511

511同步電路與異步電路有何區(qū)別

同步電路與異步電路有何區(qū)別 同步電路和異步電路是數(shù)字電路中兩種類型的電路,兩種電路在功能、結(jié)構(gòu)、時(shí)序要求等方面都存在差異。同步電路和異步電路分別適用于不同類型的應(yīng)用場(chǎng)景,因此在設(shè)計(jì)數(shù)字電路時(shí)要根據(jù)

2023-08-27 16:57:02 1852

1852

1852

1852Xilinx FPGA異步復(fù)位同步釋放—同步后的復(fù)位該當(dāng)作同步復(fù)位還是異步復(fù)位?

針對(duì)異步復(fù)位、同步釋放,一直沒搞明白在使用同步化以后的復(fù)位信號(hào)時(shí),到底是使用同步復(fù)位還是異步復(fù)位?

2023-06-21 09:59:15 277

277

277

277

數(shù)字邏輯電路下載

;nbsp; 集成同步計(jì)數(shù)器 5.3 異步計(jì)數(shù)器 5.3.1 異步計(jì)數(shù)器分析 5.3.2

2008-05-15 21:57:28

時(shí)序邏輯電路設(shè)計(jì)之同步計(jì)數(shù)器

時(shí)序電路的考察主要涉及分析與設(shè)計(jì)兩個(gè)部分,上文介紹了時(shí)序邏輯電路的一些分析方法,重點(diǎn)介紹了同步時(shí)序電路分析的步驟與注意事項(xiàng)。 本文就時(shí)序邏輯電路設(shè)計(jì)的相關(guān)問題進(jìn)行討論,重點(diǎn)介紹時(shí)序邏輯電路的核心部分——計(jì)數(shù)器。

2023-05-22 17:01:29 680

680

680

680

為什么在Verilog HDL設(shè)計(jì)中一定要用同步而不能用異步時(shí)序邏輯?

同步時(shí)序邏輯是指表示狀態(tài)的寄存器組的值只可能在唯一確定的觸發(fā)條件發(fā)生時(shí)刻改變。只能由時(shí)鐘的正跳沿或負(fù)跳沿觸發(fā)的狀態(tài)機(jī)就是一例。always @(posedge clock) 就是一個(gè)同步時(shí)序邏輯

2023-03-29 17:40:28 346

346

346

346FPGA入門之功能描述-時(shí)序邏輯

時(shí)序邏輯的代碼一般有兩種: 同步復(fù)位的時(shí)序邏輯和異步復(fù)位的時(shí)序邏輯。在同步復(fù)位的時(shí)序邏輯中復(fù)位不是立即有效,而在時(shí)鐘上升沿時(shí)復(fù)位才有效。 其代碼結(jié)構(gòu)如下:

2023-03-21 10:47:07 238

238

238

238FPGA中何時(shí)用組合邏輯或時(shí)序邏輯

數(shù)字邏輯電路分為組合邏輯電路和時(shí)序邏輯電路。時(shí)序邏輯電路是由組合邏輯電路和時(shí)序邏輯器件構(gòu)成(觸發(fā)器),即數(shù)字邏輯電路是由組合邏輯和時(shí)序邏輯器件構(gòu)成。

2023-03-21 09:49:49 258

258

258

258同步電路設(shè)計(jì)和異步電路設(shè)計(jì)的特點(diǎn)

同步邏輯是時(shí)鐘之間有固定的因果關(guān)系。異步邏輯是各時(shí)鐘之間沒有固定的因果關(guān)系。

2023-01-17 16:53:16 2692

2692

2692

2692

可編程邏輯器件有哪些?什么是同步邏輯和異步邏輯?

在組合邏輯電路中,由于門電路的輸入信號(hào)經(jīng)過的通路不盡相同,所產(chǎn)生的延時(shí)也就會(huì)不同,從而導(dǎo)致到達(dá)該門的時(shí)間不一致,我們把這種現(xiàn)象叫做競(jìng)爭(zhēng)。由于競(jìng)爭(zhēng)而在電路輸出端可能產(chǎn)生尖峰脈沖或毛刺的現(xiàn)象叫冒險(xiǎn)。

2022-12-09 09:23:31 524

524

524

524FPGA之組合邏輯與時(shí)序邏輯、同步邏輯與異步邏輯的概念

數(shù)字電路根據(jù)邏輯功能的不同特點(diǎn),可以分成兩大類:一類叫做組合邏輯電路,簡(jiǎn)稱組合電路或組合邏輯;另一類叫做時(shí)序邏輯電路,簡(jiǎn)稱時(shí)序電路或時(shí)序邏輯。

2022-12-01 09:04:04 336

336

336

336FPGA與CPLD的區(qū)別

什么是同步邏輯和異步邏輯?同步邏輯是時(shí)鐘之間有固定的因果關(guān)系。異步邏輯是各時(shí)鐘之間沒有固定的因果關(guān)系。

2022-11-07 20:02:53 489

489

489

489Verilog時(shí)序邏輯中同步計(jì)數(shù)器的功能和應(yīng)用

沒有任何寄存器邏輯,RTL設(shè)計(jì)是不完整的。RTL是寄存器傳輸級(jí)或邏輯,用于描述依賴于當(dāng)前輸入和過去輸出的數(shù)字邏輯。

2022-03-15 11:06:03 2368

2368

2368

2368【FPGA】異步復(fù)位,同步釋放的理解

異步復(fù)位,同步釋放的理解目錄目錄 同步復(fù)位和異步復(fù)位 異步復(fù)位 同步復(fù)位 那么同步復(fù)位和異步復(fù)位到底孰優(yōu)孰劣呢? 異步復(fù)位、同步釋放 問題1 問題2 問題3 問題4 問題5 參考資料同步

2022-01-17 12:53:57 4

4

4

4數(shù)字IC設(shè)計(jì)工程師筆試面試經(jīng)典100題-有答案

轉(zhuǎn)自知乎答主ictown_數(shù)字IC設(shè)計(jì)工程師筆試面試經(jīng)典100題-有答案-陳恩1:什么是同步邏輯和異步邏輯?(漢王)同步邏輯是時(shí)鐘之間有固定的因果關(guān)系。異步邏輯是各時(shí)鐘之間沒有固定的因果關(guān)系。同步

2021-11-06 10:36:00 19

19

19

19數(shù)字IC設(shè)計(jì)工程師筆試面試經(jīng)典100題

本文來(lái)自芯社區(qū),謝謝。1:什么是同步邏輯和異步邏輯? 同步邏輯是時(shí)鐘之間有固定的因果關(guān)系。異步邏輯是各時(shí)鐘之間沒有固定的因果關(guān)系。 同步時(shí)序邏輯電路的特點(diǎn):各觸發(fā)器的時(shí)鐘端全部連接在一起,并接在系統(tǒng)

2021-11-06 10:21:02 4

4

4

4淺析數(shù)字邏輯電路之邏輯門或邏輯

上篇文章我們講解了與邏輯, 緩沖器和非門只差一個(gè)圈嗎? 而與之對(duì)應(yīng)的就是或邏輯,在數(shù)字電路中與、或、非為三大基礎(chǔ)邏輯門電路,其后續(xù)的與非、或非、同或、異或,都是建立在基礎(chǔ)邏輯門電路的基礎(chǔ)上邊。 那么

2021-10-29 11:09:43 7163

7163

7163

7163

簡(jiǎn)述CDC當(dāng)中最典型錯(cuò)誤案例

一、主要概念 同步邏輯和異步邏輯:時(shí)鐘域?yàn)橛蓡蝹€(gè)時(shí)鐘或具有固定相位關(guān)系的時(shí)鐘驅(qū)動(dòng)的設(shè)計(jì)部分。也就是說(shuō),在一個(gè)模塊中一個(gè)時(shí)鐘和他的翻轉(zhuǎn)或者分頻時(shí)鐘認(rèn)為是相同的時(shí)鐘域,其所驅(qū)動(dòng)的邏輯是同步邏輯。在一個(gè)

2021-04-12 16:47:53 8045

8045

8045

8045

什么是同步邏輯和異步邏輯?同步電路和異步電路的區(qū)別是什么?

同步電路是由時(shí)序電路(寄存器和各種觸發(fā)器)和組合邏輯電路構(gòu)成的電路,其所有操作都是在嚴(yán)格的時(shí)鐘控制下完成的。這些時(shí)序電路共享同一個(gè)時(shí)鐘CLK,而所有的狀態(tài)變化都是在時(shí)鐘的上升沿(或下降沿)完成的。

2021-01-04 10:53:37 13650

13650

13650

13650數(shù)字電路設(shè)計(jì)之同步時(shí)序邏輯電路

了解嗎? (1)純組合邏輯電路的缺點(diǎn)在哪? (3)純組合邏輯電路完成不了什么功能? (2)為什么需要時(shí)鐘和寄存器呢? 帶著這三個(gè)疑問我們來(lái)認(rèn)識(shí)一下時(shí)序邏輯電路。 二. 同步時(shí)序邏輯電路的作用 1. 時(shí)序邏輯電路對(duì)于組合邏輯的毛刺具有容忍度,

2020-12-25 14:39:28 3607

3607

3607

3607

異步和同步電路的區(qū)別 同步時(shí)序設(shè)計(jì)規(guī)則

產(chǎn)生毛刺,且易受環(huán)境的影響,不利于器件的移植; 同步電路 1. 電路的核心邏輯是由各種各樣的觸發(fā)器實(shí)現(xiàn)的,所以比較容易使用寄存器的異步復(fù)位/置位端,以使整個(gè)電路有一個(gè)確定的初始狀態(tài); 2. 整個(gè)電路是由時(shí)鐘沿驅(qū)動(dòng)的; 3. 以觸發(fā)器為主體的同步時(shí)序電

2020-12-05 11:53:41 9613

9613

9613

9613FPGA設(shè)計(jì)中涉及的10個(gè)知識(shí)點(diǎn)

1、什么是同步邏輯和異步邏輯? 同步時(shí)序邏輯電路的特點(diǎn):電路中所有的觸發(fā)器都是與同一個(gè)時(shí)鐘或者該時(shí)鐘的衍生時(shí)鐘驅(qū)動(dòng),而且當(dāng)時(shí)鐘脈沖到來(lái)時(shí),電路的狀態(tài)才能改變。改變后的狀態(tài)將一直保持到下 一個(gè)時(shí)鐘脈沖

2020-11-19 15:13:15 1214

1214

1214

1214

IC設(shè)計(jì)中同步復(fù)位與異步復(fù)位的區(qū)別

1、什么是同步邏輯和異步邏輯,同步電路和異步電路的區(qū)別是什么? 同步邏輯是時(shí)鐘之間有固定的因果關(guān)系。異步邏輯是各時(shí)鐘之間沒有固定的因果關(guān)系。 電路設(shè)計(jì)可分類為同步電路和異步電路設(shè)計(jì)。同步電路利用

2020-11-09 14:58:34 8729

8729

8729

8729FPGA的經(jīng)典面試題和解答方法合集

1:什么是同步邏輯和異步邏輯?(漢王)

同步邏輯是時(shí)鐘之間有固定的因果關(guān)系。異步邏輯是各時(shí)鐘之間沒有固定的因果關(guān)系。答案應(yīng)該與上面問題一致〔補(bǔ)充〕:同步時(shí)序邏輯電路的特點(diǎn):各觸發(fā)器的時(shí)鐘端全部連接

2020-09-04 17:18:30 5

5

5

5如何設(shè)計(jì)轉(zhuǎn)換映射指導(dǎo)成功的異步狀態(tài)機(jī)

雖然ASIC公司和“良好的工程實(shí)踐”強(qiáng)調(diào)同步設(shè)計(jì)技術(shù),但時(shí)鐘速度的增加使用速度高達(dá)50至200 MHz,這迫使設(shè)計(jì)人員實(shí)施異步邏輯電路。不幸的是,雖然大多數(shù)數(shù)字設(shè)計(jì)工程師都熟悉組合和同步時(shí)序邏輯

2019-08-08 11:11:42 2447

2447

2447

2447

Xilinx FPGA的同步復(fù)位和異步復(fù)位

對(duì)于xilinx 7系列的FPGA而言,flip-flop支持高有效的異步復(fù)/置位和同步復(fù)位/置位。對(duì)普通邏輯設(shè)計(jì),同步復(fù)位和異步復(fù)位沒有區(qū)別,當(dāng)然由于器件內(nèi)部信號(hào)均為高有效,因此推薦使用高有效的控制信號(hào),最好使用高有效的同步復(fù)位。輸入復(fù)位信號(hào)的低有效在頂層放置反相器可以被吸收到IOB中。

2018-07-13 09:31:00 5911

5911

5911

5911如何區(qū)分同步復(fù)位和異步復(fù)位?

同步復(fù)位,何時(shí)采用異步復(fù)位;2. 復(fù)位電路是用來(lái)干嘛的;3. 激勵(lì)和響應(yīng)的分析(單拍潛伏期)是否適用與復(fù)位邏輯。 1. 電路中,何時(shí)采用同步或異步,取決與設(shè)計(jì)者,取決于當(dāng)前設(shè)計(jì)電路的需要。一般而言:高速邏輯應(yīng)該采用同步復(fù)位,

2018-06-11 15:15:11 6087

6087

6087

6087時(shí)序邏輯電路分析有幾個(gè)步驟(同步時(shí)序邏輯電路的分析方法)

分析時(shí)序邏輯電路也就是找出該時(shí)序邏輯電路的邏輯功能,即找出時(shí)序邏輯電路的狀態(tài)和輸出變量在輸入變量和時(shí)鐘信號(hào)作用下的變化規(guī)律。上面講過的時(shí)序邏輯電路的驅(qū)動(dòng)方程、狀態(tài)方程和輸出方程就全面地描述了時(shí)序邏輯電路的邏輯功能。

2018-01-30 18:55:32 120321

120321

120321

120321

什么是同步邏輯和異步邏輯,同步電路和異步電路的區(qū)別

異步電路:主要是組合邏輯電路,用于產(chǎn)生地址譯碼器、FIFO或RAM的讀寫控制信號(hào)脈沖,但它同時(shí)也用在時(shí)序電路中,此時(shí)它沒有統(tǒng)一的時(shí)鐘,狀態(tài)變化的時(shí)刻是不穩(wěn)定的,通常輸入信號(hào)只在電路處于穩(wěn)定狀態(tài)時(shí)才

2017-11-30 09:35:40 30261

30261

30261

30261

UART邏輯實(shí)現(xiàn)高速異步串行通信

介紹一種利用cPLD實(shí)現(xiàn)高速異步串行通信的方法,主要適用于必須使用高速異步串行通信,而對(duì)誤碼率要求又不是很高的應(yīng)用環(huán)境,如基于Rs485協(xié)議的共線語(yǔ)音通信系統(tǒng)。對(duì)實(shí)現(xiàn)方法進(jìn)行詳細(xì)的說(shuō)明,并指出該方法

2017-11-10 14:21:43 4

4

4

4邏輯門是什么?基礎(chǔ)數(shù)字邏輯門詳解

邏輯門是邏輯電路的基本組成部分,可以由晶體管來(lái)構(gòu)成,邏輯門大致可以分為基本門、萬(wàn)用門和延伸門等三種,其中基本門又可以分為與門、或門和非門三種。邏輯門可以使信號(hào)的高低電平轉(zhuǎn)化為響應(yīng)的邏輯信號(hào),從而實(shí)現(xiàn)邏輯運(yùn)算

2017-05-22 14:16:38 53353

53353

53353

53353

FPGA面試筆試數(shù)電部分

什么是同步邏輯和異步邏輯?(漢王),同步邏輯是時(shí)鐘之間有固定的因果關(guān)系。異步邏輯是各時(shí)鐘之間沒有固定的因果關(guān)系。

2012-01-18 16:32:53 2536

2536

2536

2536邏輯運(yùn)算,什么是邏輯運(yùn)算

邏輯運(yùn)算,什么是邏輯運(yùn)算 計(jì)算機(jī)中除了進(jìn)行加、減、乘、除等基本算術(shù)運(yùn)算外,還可對(duì)兩個(gè)或一個(gè)邏輯數(shù)進(jìn)行邏輯運(yùn)算。所謂邏輯數(shù),是指不帶符號(hào)的二進(jìn)制

2010-04-13 10:48:38 29945

29945

29945

29945邏輯加密卡,邏輯加密卡是什么意思

邏輯加密卡,邏輯加密卡是什么意思

邏輯加密存儲(chǔ)卡(Smart Card With Security Logic)主要是由EEPROM存儲(chǔ)單元陣列和密碼控制邏輯單元所構(gòu)成。

2010-04-02 13:35:45 4633

4633

4633

4633華為同步電路設(shè)計(jì)規(guī)范

華為同步電路設(shè)計(jì)規(guī)范

為了增加可編程邏輯器件電路工作的穩(wěn)定性,一定要加強(qiáng)可編程邏輯器件設(shè)計(jì)的規(guī)范要求,要盡量采用同步電路設(shè)計(jì)。對(duì)于設(shè)計(jì)中的異步

2010-02-11 10:04:19 125

125

125

125FPGA工程師面試試題集錦

FPGA工程師面試試題集錦1、同步電路和異步電路的區(qū)別是什么?(仕蘭微電子)2、什么是同步邏輯和異步邏輯?(漢王筆試)同步邏輯是時(shí)鐘之間有固定的因果關(guān)系。異步

2009-09-28 16:36:22 73

73

73

73異步時(shí)序邏輯電路

異步時(shí)序邏輯電路:本章主要從同步時(shí)序邏輯電路與異步時(shí)序邏輯電路狀態(tài)改變方式不同的特殊性出發(fā), 系統(tǒng)的介紹異步時(shí)序邏輯電路的電路結(jié)構(gòu)、工作原理、分析方法和設(shè)計(jì)方法。

2009-09-01 09:12:34 59

59

59

59邏輯代數(shù)與邏輯函數(shù)

邏輯代數(shù)與邏輯函數(shù):本章主要討論分析和設(shè)計(jì)數(shù)字邏輯功能的數(shù)學(xué)。首先介紹邏輯代數(shù)中的基本運(yùn)算、基本公式, 常用定理和重要規(guī)則; 然后講述邏輯函數(shù)的形式與轉(zhuǎn)換; 最后介

2009-09-01 09:11:40 47

47

47

47同步時(shí)序邏輯電路

同步時(shí)序邏輯電路:本章系統(tǒng)的講授同步時(shí)序邏輯電路的工作原理、分析方法和設(shè)計(jì)方法。從同步時(shí)序邏輯電路模型與描述方法開始,介紹同步時(shí)序邏輯電路的分析步驟和方法。然后

2009-09-01 09:06:27 71

71

71

71組合邏輯電路的分析與設(shè)計(jì)-邏輯代數(shù)

組合邏輯電路的分析與設(shè)計(jì)-邏輯代數(shù)

在任何時(shí)刻,輸出狀態(tài)只決定于同一時(shí)刻各輸入狀態(tài)的組合,而與先前狀態(tài)無(wú)關(guān)的邏輯電路稱為組合邏輯電路。

2009-04-07 10:07:57 2503

2503

2503

2503

邏輯函數(shù)與邏輯問題的描述

邏輯函數(shù)與邏輯問題的描述

在討論了與、或、非三種基本邏輯運(yùn)算后,下面將從工程實(shí)際出發(fā),提出邏輯命題,然后用真值表加以描述,從真值表可以寫出邏輯函數(shù)。一

2009-04-06 23:56:35 1192

1192

1192

1192

二值數(shù)字邏輯和邏輯電平

二值數(shù)字邏輯和邏輯電平

二進(jìn)制數(shù)正好是利用二值數(shù)字邏輯中的0和1來(lái)表示的。二值數(shù)字邏輯是Binary Digital Logic的譯稱。 與模擬信

2009-04-06 23:37:10 3163

3163

3163

3163

第二十七講 同步時(shí)序邏輯電路的設(shè)計(jì)

第二十七講 同步時(shí)序邏輯電路的設(shè)計(jì)

7.5 同步時(shí)序邏輯電路的設(shè)計(jì)用SSI觸發(fā)器16進(jìn)制以內(nèi)7.5.1 同步時(shí)序邏輯電路的設(shè)計(jì)方法

2009-03-30 16:31:56 3156

3156

3156

3156

時(shí)序邏輯電路

實(shí)驗(yàn)十六 時(shí)序邏輯電路? 實(shí)驗(yàn)(1) 計(jì)數(shù)器?一、實(shí)驗(yàn)?zāi)康?⒈ 熟悉計(jì)數(shù)器的設(shè)計(jì)方法及工作原理。?⒉ 了解同步計(jì)數(shù)器與異步計(jì)數(shù)器的區(qū)別。?⒊ 應(yīng)用

2008-09-24 22:17:08 3155

3155

3155

3155

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論