組合邏輯電路實驗實驗三 組合邏輯電路一、 實驗目的1、 掌握組合邏輯電路的功能測試2、 驗證半加器和全加器的邏輯功能3、 學會

2009-03-20 18:11:09

做任何模塊前,要確定輸入輸出端口有哪些,有一個整體的概念;方便以后模塊調用;

2023-10-10 14:10:56 86

86

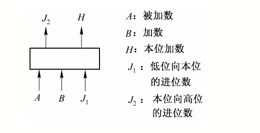

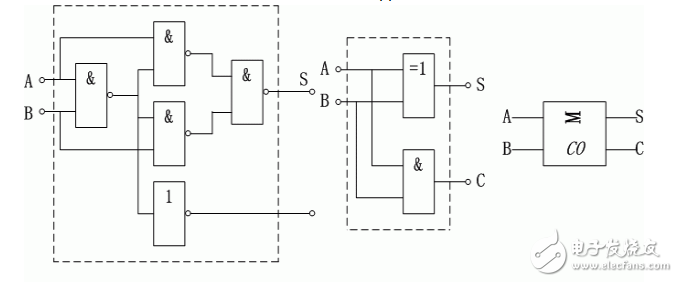

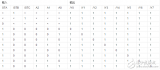

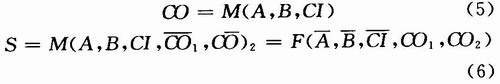

按照半加器和全加器的真值表寫出輸出端的邏輯表達式,對半加器,輸出的進位端是量輸入的“與”,輸出的計算結果是量輸入的異或;對全加器,也按照邏輯表達式做。

2023-06-25 17:38:51 451

451

電子發燒友網站提供《在Spartan 6 FPGA上從頭開始實現全加器.zip》資料免費下載

2023-06-15 10:13:28 0

0 大家好!今天給大家分享的是4位全加器的代碼以及仿真程序。俗話說:“千里之行,始于足下。”對于初學者來說, 加法器是fpga初學者入門必須掌握的內容。我們很多朋友在入門時囫圇吞棗,一些基礎的東西沒有

2023-05-23 10:00:10 761

761

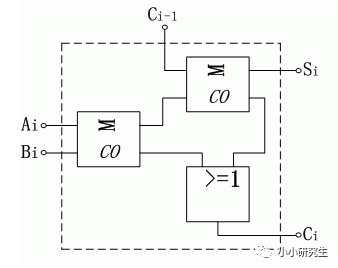

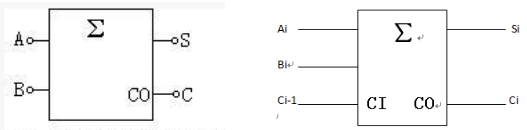

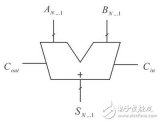

首先半加器是A+B構成了{C,S}。由于全加器多了一個低位的進位,就是將{C,S}再加上Ci-1。

2023-05-22 15:26:35 583

583

在上一節半加器中,介紹了全加器可看作兩個半加器和一個或門組成。

2023-05-14 15:07:47 837

837

Verilog數字系統設計四復雜組合邏輯實驗2文章目錄Verilog數字系統設計四前言一、什么是8位全加器和8為帶超前進位的全加器?二、編程1.要求:2.門級原語實現8位全加器:3.門級原語實現帶

2021-12-05 19:06:10 4

4 過1位全加器的詳細設計,掌握原理圖輸入以及Verilog的兩種設計方法。

2021-11-03 12:51:07 8

8 多思計算機組成原理網絡虛擬實驗系統計算機組成原理實驗一全加器實驗

2021-10-22 10:36:12 11

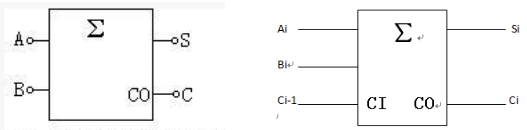

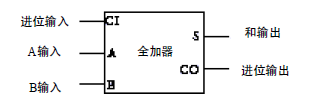

11 全加器英語名稱為full-adder,是用門電路實現兩個二進制數相加并求出和的組合線路,稱為一位全加器。一位全加器可以處理低位進位,并輸出本位加法進位,多個一位全加器進行級聯可以得到多位。全加器是形成三位算術和的組合電路,它由三個輸入和兩個輸出組成。

2021-06-29 09:14:46 53586

53586

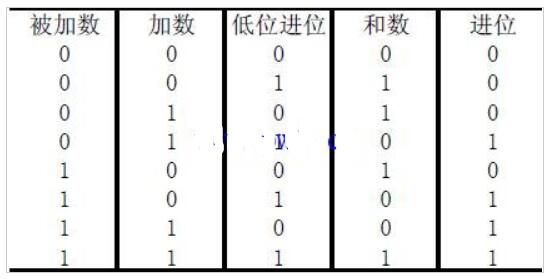

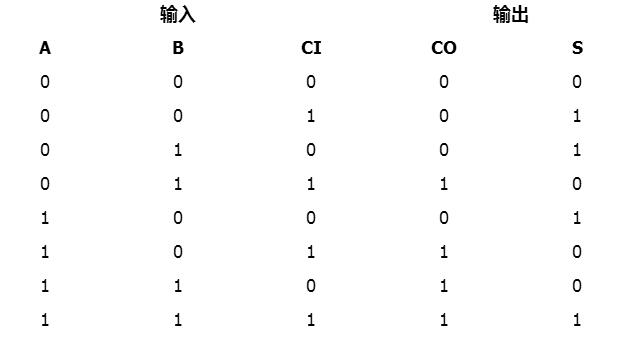

全加器能進行加數、被加數和低位來的進位信號相加,并依據求和作用給出該位的進位信號。依據它的功用,能夠列出它的真值表,如表1.2所示。

2021-02-18 14:33:09 52382

52382

主要內容:設計一個一位的全加器,從真值表開始,介紹門級實現,然后形成電路圖,對功能進行仿真驗證,最后再用行為級描述實現全加器功能,二者形成對比。把 Verilog 代碼,硬件電路,仿真波形三者對應起來。

2020-12-10 15:00:32 6

6 個四位串行加法器由4個全加器構成。全加器是串行加法器的子模塊,而全加器是由基本的邏輯門構成,這些基本的邏輯門就是所說的葉子模塊。這個設計中運用葉子模塊(基本邏輯門)搭建成子模塊(全加器),再用子模

2020-12-09 11:24:30 27

27 通過此實驗了解FPGA 開發軟件Quartus II 的使用方法及VHDL 的編程方法,學習用VHDL 語言來描述1 位全加器及電路的設計仿真和硬件測試。

2020-12-02 16:34:48 12

12 全加器的輸入端有三個,分別為A、B、C(低位的進位);兩個輸出S(和);C(運算產生的進位)。

2020-04-23 09:59:42 96058

96058

本文主要介紹了全加器邏輯表達式及全加器的邏輯功能。

2020-04-23 09:51:14 105979

105979

全加器是數字信號處理器微處理器中的重要單元,它不僅能完成加法,還能參與減法、乘法、除法等運算,所以,。提高全加器性能具有重要意義。本文分析了兩種普通全加器,運用布爾代數對全加器和的數、進位函數進行

2019-07-03 17:11:16 38

38 本文檔的主要內容詳細介紹的是VHDL語言設計的全加器源代碼和工程文件免費下載。

2019-06-03 08:00:00 4

4 電子發燒友網為你提供()MC14008B相關產品參數、數據手冊,更有MC14008B的引腳圖、接線圖、封裝手冊、中文資料、英文資料,MC14008B真值表,MC14008B管腳等資料,希望可以幫助到廣大的電子工程師們。

2019-04-18 21:54:09

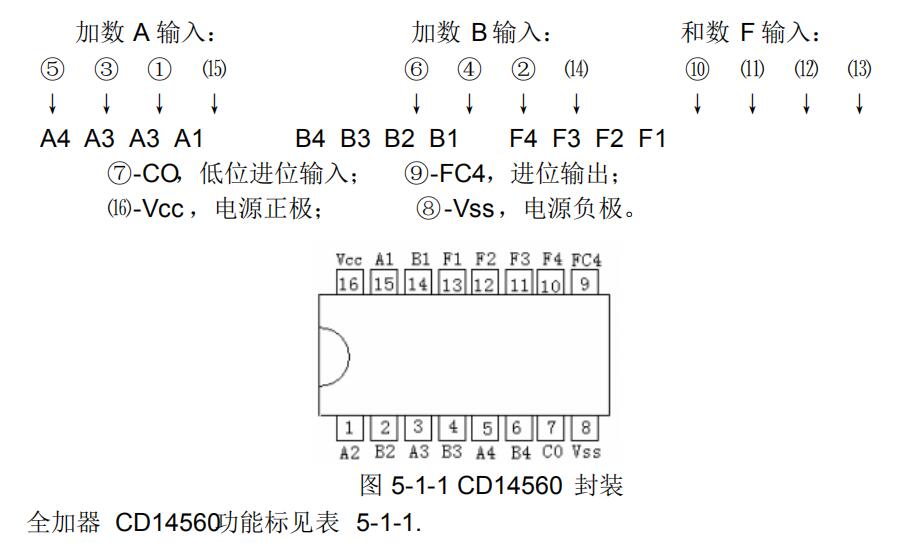

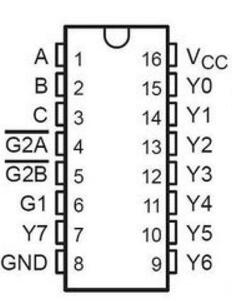

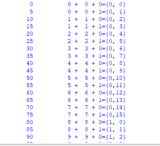

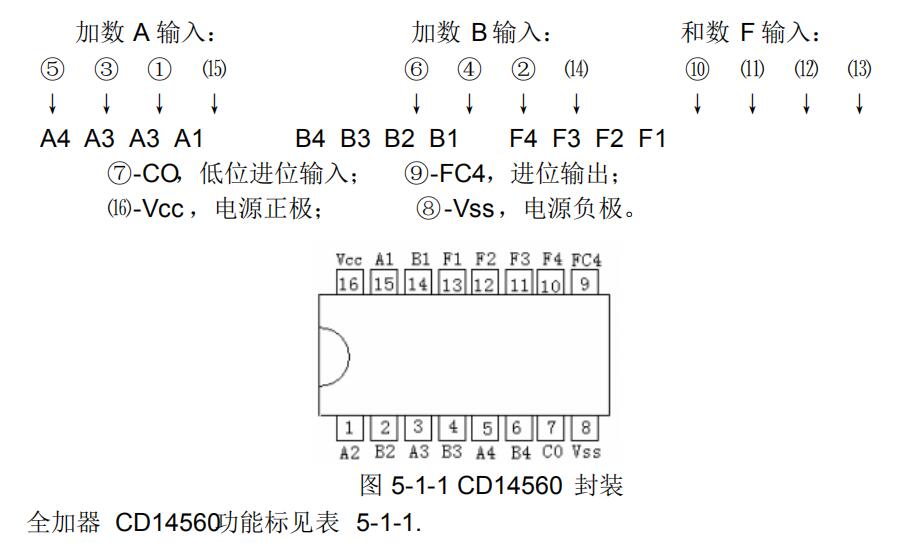

全加器 CD14560的工作原理 CD14560 是一塊十進制全加速集成電路,為 16 腳雙列直插封裝結構,可以完成一位十進制數的全加運算。輸入、輸出都是 BCD碼中的自然數,稱為 NBCD全加速。如圖 5-1-1 所示為 CD14560全加速的封裝。

2018-12-20 18:16:04 4157

4157

本文檔的主要內容詳細介紹的是74LS153利用雙四選一數據選擇器實現全加器的電路圖資料免費下載。

2018-11-26 08:00:00 502

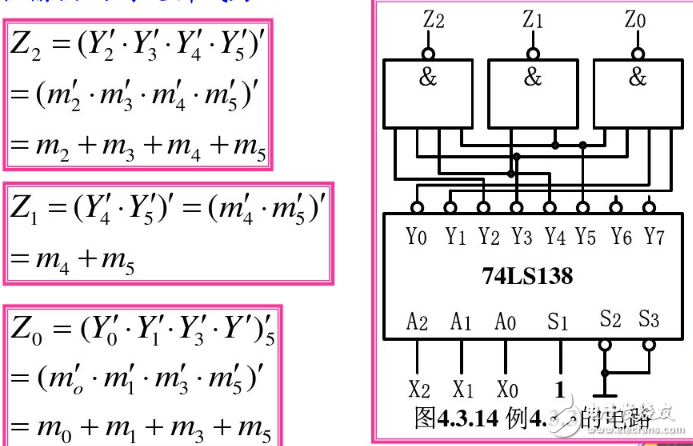

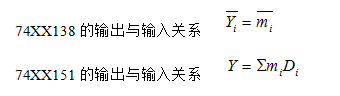

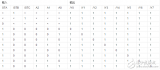

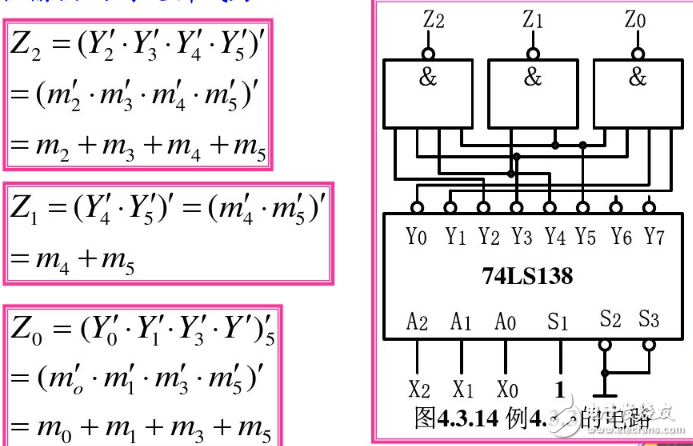

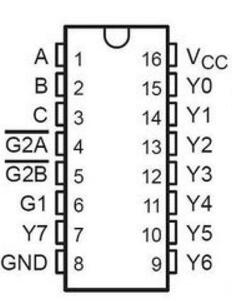

502 上圖中所使用的74LS138和74HC138兩者功能一樣,74HC138采用高速CMOS工藝制作,自身功耗低,輸出高低電平范圍寬。

2018-08-07 16:50:19 108764

108764

全加器英語名稱為full-adder,是用門電路實現兩個二進制數相加并求出和的組合線路,稱為一位全加器。

2018-07-25 16:03:28 73110

73110 全加器是一個能夠完成一位(二進制)數相加的部件。我們先來看一下兩個二進制數的加法運算是怎樣進行的。

2018-07-25 15:48:44 67834

67834

計算機最基本的任務之一是進行算數,在機器中四則運算——加、減、乘、除——都是分解成加法運算進行的,因此加法器便成為計算機中最基本的運算單元。

2018-07-25 15:14:09 37176

37176

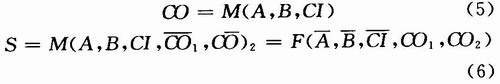

實際上,一個完整的加法器的輸入端有3個:A、B和低位的進位結果CI。

2018-07-25 14:52:06 37006

37006

半加器、全加器是組合電路中的基本元器件,也是CPU中處理加法運算的核心,理解、掌握并熟練應用是硬件課程的最基本要求。

2018-07-25 14:39:45 130197

130197

半加器+半加法和全加法是算術運算電路中的基本單元,它們是完成1位二進制相加的一種組合邏輯電路。

2018-07-25 11:37:16 321963

321963

加器是能夠計算低位進位的二進制加法電路。與半加器相比,全加器不只考慮本位計算結果是否有進位,也考慮上一位對本位的進位,可以把多個一位全加器級聯后做成多位全加器。

2018-07-25 11:15:53 65775

65775

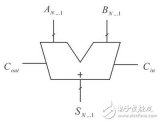

N位全加器將{AN,……,A1}、{BN,……,B1}和進位輸入Cin作為輸入,計算得到和{SN,……,S1}以及最高位的進位輸出Cout(見圖1)。每一位得到的和與進位輸出都直接受其上一位的影響,其進位輸出也會影響下一位。最終,整個全加器的和與輸出都受進位輸入Cin的影響。

2018-06-08 10:24:00 3995

3995

本文主要詳解四位全加器74ls83,首先介紹了74ls83特點及引腳圖、真值表,其次介紹了74ls83功能表、典型參數及邏輯圖,最后介紹了74ls83推薦工作條件、電性能以及74ls83交流(開關)參數,具體的跟隨小編一起來了解一下。

2018-05-31 09:12:06 91346

91346

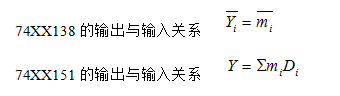

本文主要介紹了74ls151應用電路圖大全(全加器\表決器)。五人表決器,只要贊成人數大于或等于三,則表決通過。因此,只需將每位表決人的結果相加,判斷結果值。設五個開關A、B、C、D、E作為表決器

2018-05-07 11:38:47 99110

99110

本文主要介紹了用74ls151實現全加器設計電路。根據全加器的定義可知:輸入為:A,B,Ci其中A,B為被加數和加數,Ci為低位進位數。輸出為:S,Co,其中S為本位和數,Co為高位進位數。其邏輯關系為:S=A⊕B⊕Ci;Co=AB+(A⊕B)Ci。

2018-05-07 09:52:22 106645

106645

本文主要介紹了五款74ls138的應用電路圖。其中包括了74ls138全加器電路、74ls138搶答器電路、74ls138實現邏輯函數、74ls138全減器電路以及與74LS20組合的三人表決器電路。

2018-05-04 10:31:55 87718

87718

8位全加器可由2個4位的全加器串聯組成,因此,先由一個半加器構成一個全加器,再由4個1位全加器構成一個4位全加器并封裝成元器件。加法器間的進位可以串行方式實現,即將低位加法器的進位輸出cout與相臨的高位加法器的最低進位輸入信號cin相接最高位的輸出即為兩數之和。

2017-11-24 10:01:45 27671

27671

引言 在全加器設計中運用PG邏輯是非常普遍的,本文在設計和研究全加器時,根據現有的PG邏輯公式推導出了一種新的邏輯公式,并論證了兩者之間的等價關系。這一新的公式能夠指導全加器設計中的連線方式,靈活

2017-11-06 11:49:57 0

0 用兩片74LS138設計一個全加器。在考慮到74LS138譯碼器為3 線-8 線譯碼器,共有 54/74S138和 54/74LS138 兩種線路結構型式,其74LS138工作原理為:當一個選通端

2017-10-31 15:53:34 137363

137363

一種基于互補型單電子晶體管的全加器電路設計

2017-02-07 16:14:56 8

8 電子類基礎芯片資料,很好的手冊,工程師必備資料。

2016-05-31 15:42:56 9

9 FPGA學習的好資料,很實用的FPGA教程文檔,快來學習吧。

2016-05-12 14:05:52 23

23 FPGA學習資料,有興趣的同學可以下載看看。

2016-04-07 14:17:45 56

56 FPGA學習資料,有興趣的同學可以下載看看。

2016-04-07 14:04:26 18

18 實驗五 全加器、譯碼器及數碼顯示電路 一、實驗目的 1、掌握全加器邏輯功能,熟悉集成加法器功能及其使用方法。 2、掌握用七段譯碼器和七段數碼管顯示十進制數的方法。 3、掌握

2012-07-16 23:01:22 37

37 加法運算是數字系統中最基本的算術運算。為了能更好地利用加法器實現減法、乘法、除法、碼制轉換等運算,提出用Multisim虛擬仿真軟件中的邏輯轉換儀、字信號發生器、邏輯分析儀

2011-05-06 15:55:07 82

82 O 引言 加法運算是算術運算中最基本的運算。減法、乘法、除法及地址計算這些基于加法的運算已廣泛地應用于超大規模集成電路(VLSI)中。全加器是組成二進

2010-10-19 10:57:22 5079

5079

基于單電子晶體管的I-V特性和傳輸晶體管的設計思想,用多柵單電子晶體管作為傳輸晶體管,設計了一個由5個SET構成的全加器,相對于靜態互補邏輯設計的全加器,本文設計的全加器在器

2010-07-30 16:54:22 18

18 摘要:應用CMOS電路開關級設計技術對超前進位全加器進行了設計,并用PSPICE模擬進行了功能驗證.與傳統門級設計電路相比,本文設計的超前進位電路使用了較少的MOS管,并能保持

2010-05-28 08:18:20 25

25 什么是一位全加器,其原理是什么

加器是能夠計算低位進位的二進制加法電路

一位全加器由2個半加

2010-03-08 17:13:33 72422

72422 全加器,全加器是什么意思

full-adder 用門電路實現兩個二進數相加并求出和的組合線路,稱為一個全加器。

2010-03-08 17:04:58 78218

78218

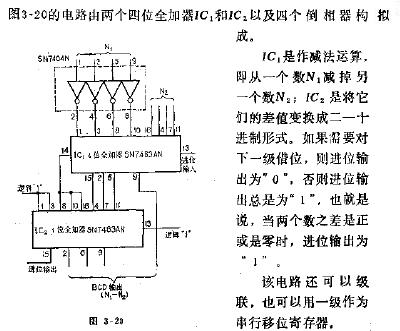

用四位全加器構成二一十進制加法器

2009-04-09 10:34:43 5490

5490

用兩個全加器構成二一十進制相減器

2009-04-09 10:34:19 739

739

CC4008中文資料:型由具有段間快速超前進位的4個全加器段組成。

2008-04-07 22:27:03 32

32

54/742834 位二進制超前進位全加器簡要說明:283為具有超前進位的 4 位全加器,共有 54/74283,54/74S28

2008-03-15 09:23:23 441

441

電子發燒友App

電子發燒友App

硬聲App

硬聲App

451

451

761

761

4

4 53586

53586

6

6 27

27 12

12 38

38

4157

4157

502

502 108764

108764

37176

37176

130197

130197

65775

65775

3995

3995

91346

91346

99110

99110

106645

106645

87718

87718

27671

27671

0

0 137363

137363

37

37 82

82 5079

5079

18

18 25

25 441

441

評論