D觸發器,是時序邏輯電路中必備的一個基本單元,學好 D 觸發器,是學好時序邏輯電路的前提條件,其重要性不亞于加法器,二者共同構成數字電路組合、時序邏輯的基礎。

2023-10-09 17:26:57 234

234

由于RS觸發器實現方式的不同,對輸入信號抖動(即短時間內多次變化)的響應也不同。原始的電路設計可能導致RS觸發器對輸入信號的抖動比較敏感。

2023-09-07 15:47:45 683

683 的存儲單元,具有時鐘同步的特性。其中,D觸發器是數字電路設計中使用最廣泛的一種觸發器類型之一,因為它具有簡單、穩定和多功能等優點。

2023-08-31 10:50:19 1436

1436

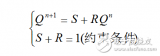

在傳統的異步 RS 觸發器中,當輸入的 R 和 S 同時為 1 時,會引發互鎖問題,輸出結果是不確定的。為了避免這個問題,常常使用帶有使能控制的同步觸發器,如帶有時鐘信號的 D 觸發器或 JK 觸發器。這些觸發器在時鐘邊沿上才會響應輸入信號,解決了異步 RS 觸發器的互鎖問題。

2023-08-28 15:44:35 641

641 文章中,我們將詳細探討觸發器的輸出狀態如何被決定的。 1. 異步觸發器 異步觸發器是一種最簡單的觸發器類型。它包括SR觸發器和D觸發器。SR觸發器由兩個輸入引腳“S”和“R”組成,D觸發器只有一個輸入引腳“D”。 SR觸發器有四

2023-08-24 15:50:23 276

276 用D觸發器設計一個序列發生器 怎么用D觸發器做序列信號發生器? 序列發生器是數字電子技術中常用的電路模塊之一,它可以用來生成一系列的數字信號序列。在數字電路中,D觸發器是一種被廣泛使用的數字邏輯組件

2023-08-24 15:50:17 549

549 什么是觸發器?觸發器的作用是什么?觸發器的觸發方式 觸發器是一種在數據庫中執行自動化操作的工具。它是一種特殊的存儲過程,可以監視數據庫表的變化,并在滿足特定條件時自動觸發一系列操作。觸發器通常

2023-08-24 15:50:15 852

852 數字系統往往是由多個觸發器所組成,這時常常需要各個觸發器按照一定的節拍同步動作,因此必須給電路加上一個統一的控制信號。

2023-07-05 10:49:41 296

296

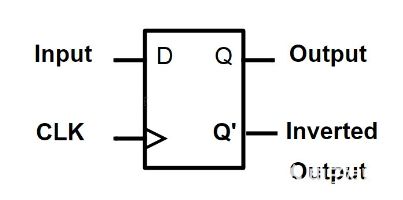

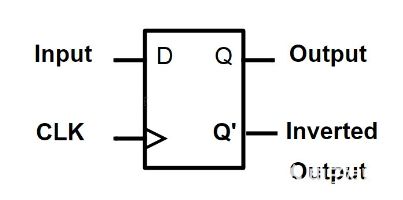

鎖存器和觸發器有時組合在一起,因為它們都可以在其輸出上存儲一位(1或0)。與鎖存器相比,觸發器是需要時鐘信號(Clk)的同步電路。D 觸發器僅在時鐘從

2023-06-29 11:50:18 5258

5258

本文旨在總結近期復習的數字電路D觸發器(邊沿觸發)的內容。

2023-05-22 16:54:29 3707

3707

本系列整理數字系統設計的相關知識體系架構,為了方便后續自己查閱與求職準備。對于FPGA和ASIC設計中,D觸發器是最常用的器件,也可以說是時序邏輯的核心,本文根據個人的思考歷程結合相關書籍內容和網上文章,聊一聊D觸發器與亞穩態的那些事。

2023-05-12 16:37:31 975

975

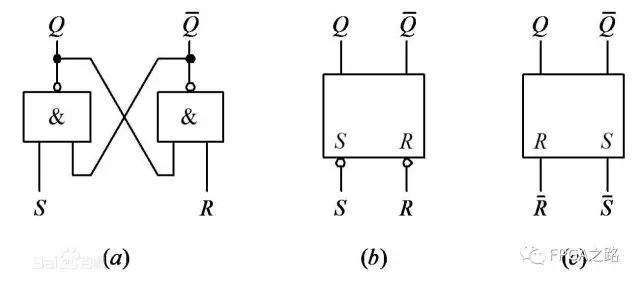

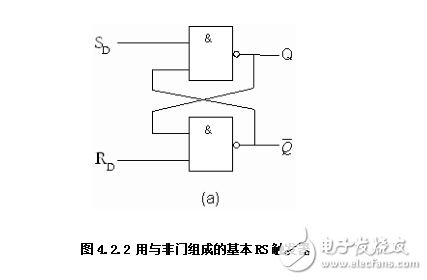

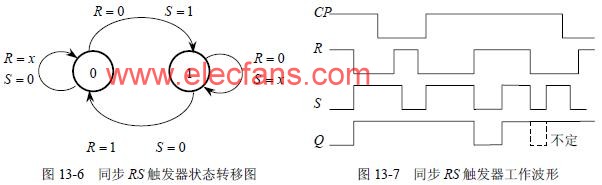

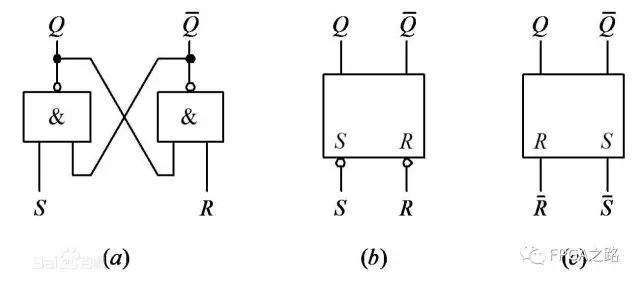

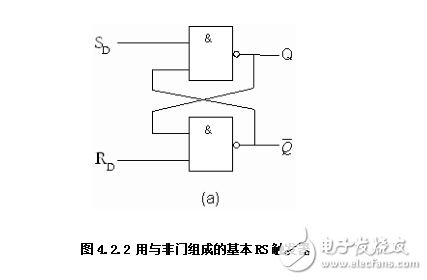

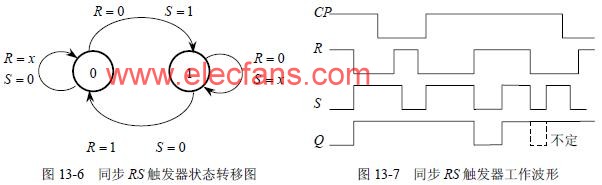

同步RS觸發器

在數字電路中,為協調各部分動作一致,常要求某些觸發器于同一時刻工作,所以要引入同步信號。電路結構如下:

2023-03-23 14:47:40 1087

1087

雙D型觸發器-HEF4013B

2023-02-15 18:49:50 0

0 單D型觸發器;上升沿觸發-74AHC_AHCT1G79

2023-02-14 19:13:27 1

1 低功耗D型觸發器;上升沿觸發-74AUP1G79

2023-02-14 18:43:30 1

1 單D型觸發器;上升沿觸發-74LVC1G80

2023-02-09 21:51:11 1

1 單D型觸發器;上升沿觸發-74LVC1G79

2023-02-09 21:50:57 0

0 低功耗D型觸發器;上升沿觸發-74AUP1G80

2023-02-07 19:00:48 0

0 D 觸發器或數據觸發器是一種觸發器,它只有一個數據輸入“D”和一個時鐘脈沖輸入, 這種觸發器也稱為延遲觸發器,經常用于許多時序電路,如寄存器、計數器等。下面一起來了解一下D觸發器不同應用下的電路圖。

2023-01-06 14:19:46 1874

1874 在數字電路中,為協調各部分動作一致,常要求某些觸發器于同一時刻工作,所以要引入同步信號。

2022-12-27 09:20:00 20885

20885 的輸出連接,其狀態由主觸發器的狀態決定,稱為從觸發器。電路結構 主從RS觸發器由兩個同步RS觸發器組成,它們分別稱為主觸發器和從觸發器。反相器使這兩個觸發器加上互補時鐘脈沖。如圖7.4.1所示。 工作原理: 當CP=1時,主觸發器的輸入門G7和G8打開

2022-10-19 19:16:03 16964

16964

D觸發器也稱為“延遲觸發器”或“數據觸發器”,主要用于存儲1位二進制數據,是數字電子產品中廣泛使用的觸發器之一。除了作為數字系統中的基本存儲元件外,D觸發器也被視為延遲線元件和零階保持元件。

2022-10-11 17:21:02 97371

97371

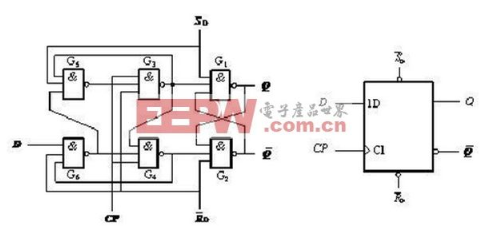

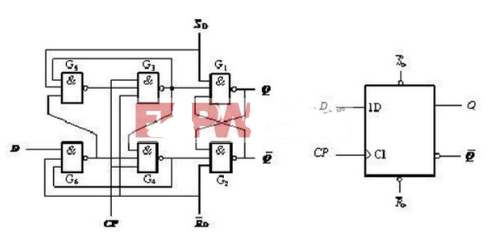

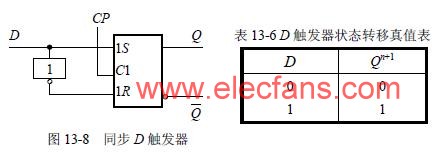

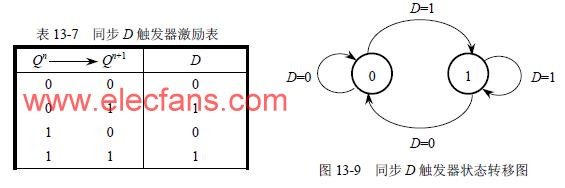

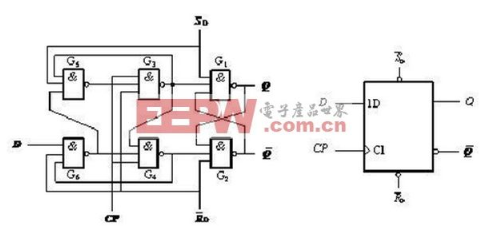

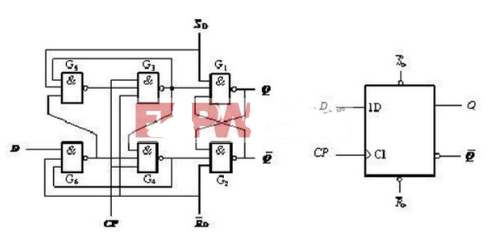

上圖是用與非門實現的D觸發器的邏輯結構圖,CP是時鐘信號輸入端,S和R分別是置位和清零信號,低有效; D是信號輸入端,Q信號輸出端;

2022-09-19 15:22:24 3240

3240 每個 Slice 有 8 個 FF 。四個可以配置為 D 型觸發器或電平敏感鎖存器,另外四個只能配置為 D 型觸發器,但是需要記得是:當原來的四個 FF 配置為鎖存器時,不能使用這四個 FF 。

2022-07-22 10:05:01 2518

2518 1、掌握觸發器功能的測試方法。

2、掌握基本RS觸發器的組成及工作原理。

3、掌握集成JK觸發器和D觸發器的邏輯功能及觸發方式。

4、掌握幾種主要觸發器之間相互轉換的方法。

5、通過實驗、體會CPLD芯片的高集成度和多I\O口。

2022-07-10 14:39:58 18

18 觸發器實驗1)熟悉常用觸發器的邏輯功能及測試方法。2)了解觸發器邏輯功能的轉換。三.實驗內容及步驟 (1) 基本RS觸發器邏輯功能測試(2) JK觸發器邏輯功能測試(3) D觸發器邏輯功能的測試

2009-03-20 10:01:05

D融發器工作原理及過程說明: SD和RD接至基本RS觸發器的輸入端,它們分別是預置和清零端,低電平有效。 ? ? ? ?當SD=0且RD=1時,不論輸入端D為何種狀態,都會使Q=1,Q非=0,即

2021-08-09 23:17:49 7277

7277 74LS74內含兩個獨立的D上升沿雙d觸發器,每個觸發器有數據輸入(D)、置位輸入( )復位輸入( )、時鐘輸入(CP)和數據輸出(Q)。 的低電平使輸出預置或清除,而與其它輸入端的電平無關。當

2021-06-04 15:40:41 63776

63776

脈沖觸發器由兩個相同的電平觸發的SR觸發器組成,其中左SR觸發器成為主觸發器,右手側稱為從觸發器。

2021-02-11 10:56:00 6965

6965

在分析維持-阻塞邊沿D觸發器的工作原理之前,讓我們先來看看 R0的復位功能 、S0的置位功能是如何實現的吧。

2020-10-18 11:26:31 19272

19272

JK觸發器是數字電路觸發器中的一種基本電路單元。JK觸發器具有置0、置1、保持和翻轉功能,在各類集成觸發器中,JK觸發器的功能最為齊全。在實際應用中,它不僅有很強的通用性,而且能靈活地轉換其他類型的觸發器。由JK觸發器可以構成D觸發器和T觸發器。

2019-11-08 14:48:44 79654

79654

首選我們來聊聊時序邏輯中最基礎的部分D觸發器的同步異步,同步復位即復位信號隨系統時鐘的邊沿觸發起作用,異步復位即復位信號不隨系統時鐘的邊沿觸發起作用,置數同理,rst_n表示低電平復位,我們都知道D

2019-07-26 10:17:16 23884

23884

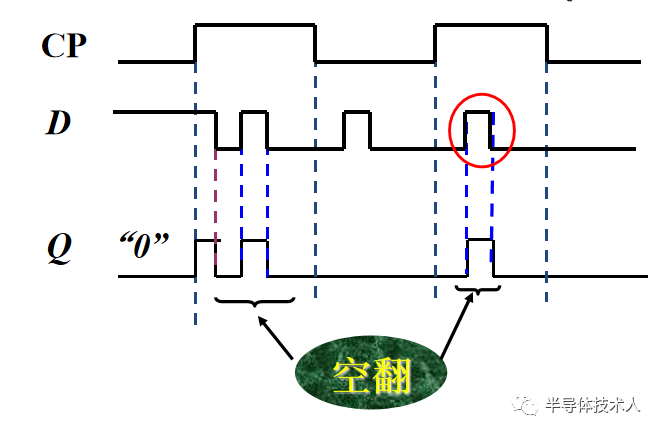

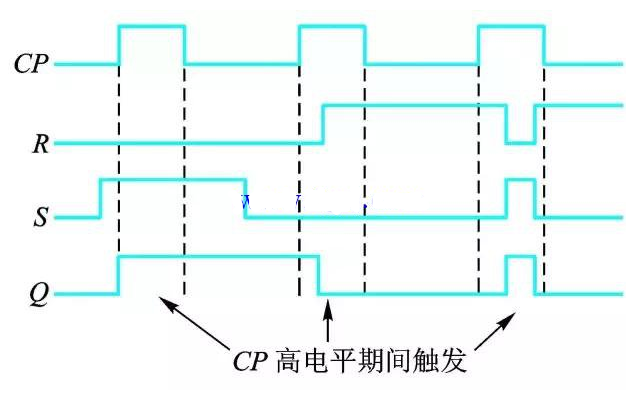

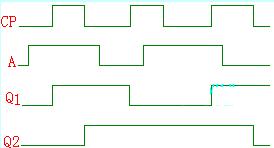

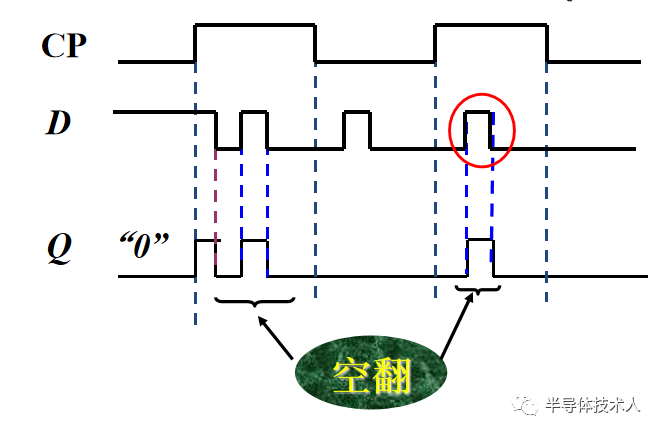

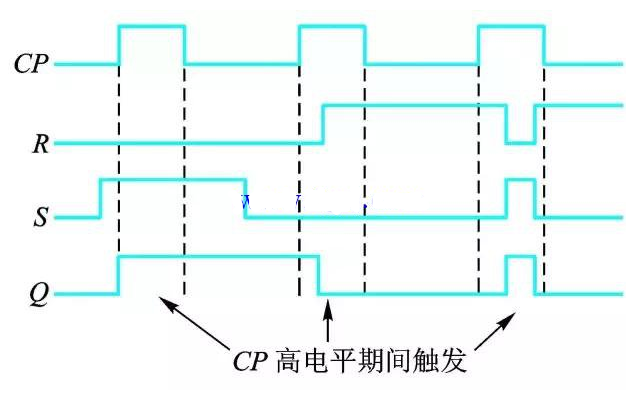

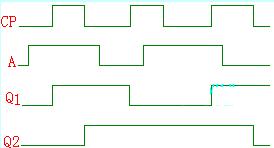

同步式觸發采用高電平觸發方式即在CP高電平期間,輸入信號起作用。同步式RS觸發器波形見下圖,在CP高電平期間,輸出會隨輸入信號變化,因此無法保證一個CP周期內觸發器只動作一次。

2019-07-15 09:23:29 36460

36460

CP=1時,門。。打開,門。。被封鎖,從觸發器保持原來狀態不變,D信號進入主觸發器。但是要特別注意,這時主觸發器只跟隨而不鎖存,即。。跟隨D變化,D怎么變。。也隨之怎么變。

2019-07-15 08:57:32 42337

42337

負跳沿觸發的主從觸發器工作時,必須在正跳沿前加入輸入信號。如果在CP 高電平期間輸入端出現干擾信號,那么就有可能使觸發器的狀態出錯。而邊沿觸發器允許在CP 觸發沿來到前一瞬間加入輸入信號。這樣,輸入端受干擾的時間大大縮短,受干擾的可能性就降低了。邊沿D觸發器也稱為維持-阻塞邊沿D觸發器。

2019-07-12 08:50:36 94674

94674

本文開始介紹了觸發器的定義和觸發器的特點,其次闡述了觸發器的分類和觸發器的作用,最后介紹了觸發器的工作原理。

2018-03-27 17:35:52 19880

19880 本文開始介紹了什么是單穩態觸發器以及單穩態觸發器的電路組成,其次闡述了單穩態觸發器特點、門電路構成的單穩態觸發器、D觸發器構成的單穩態觸發器,最后詳細的闡述了時基電路構成的單穩態觸發器。

2018-03-27 09:24:23 68948

68948

按照穩定工作狀態分,可分為雙穩態觸發器、單穩態觸發器、無穩態觸發器(多諧振蕩器)等;按照邏輯功能劃分,可分為RS觸發器、D觸發器、T觸發器、JK觸發器等幾類;按照電路結構劃分,可分為基本RS觸發器、同步觸發器(時鐘控制的觸發器)、主從型觸發器、維持-阻塞型觸發器和邊沿觸發器等幾種類型。

2018-01-31 15:02:50 26153

26153

邊沿觸發器,指的是接收時鐘脈沖CP 的某一約定跳變(正跳變或負跳變)來到時的輸入數據。在CP=l 及CP=0 期間以及CP非約定跳變到來時,觸發器不接收數據的觸發器。具有下列特點的觸發器稱為邊沿觸發方式觸發器,簡稱邊沿觸發器。

2018-01-31 09:02:33 68254

68254

JK觸發器是數字電路觸發器中的一種基本電路單元。JK觸發器具有置0、置1、保持和翻轉功能,在各類集成觸發器中,JK觸發器的功能最為齊全。在實際應用中,它不僅有很強的通用性,而且能靈活地轉換其他類型的觸發器。由JK觸發器可以構成D觸發器和T觸發器。

2017-12-25 17:30:03 172587

172587

實驗內容 將基本RS觸發器,同步RS觸發器,集成J-K觸發器,D觸發器同時集成一個CPLD芯片中模擬其功能,并研究其相互轉換的方法。 實驗的具體實現要連線測試。 原理圖 如圖6-1

2017-12-05 09:33:41 13

13 D觸發器(data flip-flop或delay flip-flop)由6個與非門組成,其中G1和G2構成基本RS觸發器。電平觸發的主從觸發器工作時,必須在正跳沿前加入輸入信號。如果在CP高電平期間輸入端出現干擾信號,那么就有可能使觸發器的狀態出錯。

2017-11-02 09:59:08 95590

95590

用一對互補的輸入信號送入RS 觸發器,就得到單輸入的 D 觸發器。由于D 觸發器有一對互補信號接至RS 觸發器的 輸入端,所以它避免了RS 輸入端同時為1 的不允許工作狀 態。D 觸發器通常用來暫時存儲一個比特的信息或用作時延 器件。當CLOCK=1 時,觸發器能把輸

2011-03-09 16:20:01 92

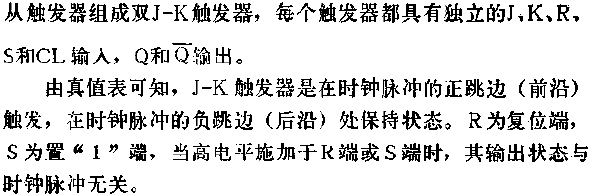

92 圖中所示是用J-K觸發器組成的D觸發器電路。

從J-K觸發器的邏輯圖已知在D觸發器端增

2010-09-24 00:21:27 5729

5729

J-K觸發器是一種多功能觸發器,它既具有R-S觸發器的功能,又具有D觸發器和T觸發器的功能,因此使用十分靈活

2010-09-24 00:12:06 1161

1161

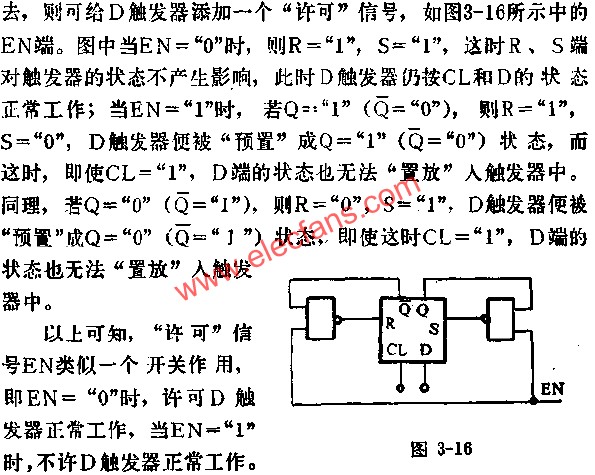

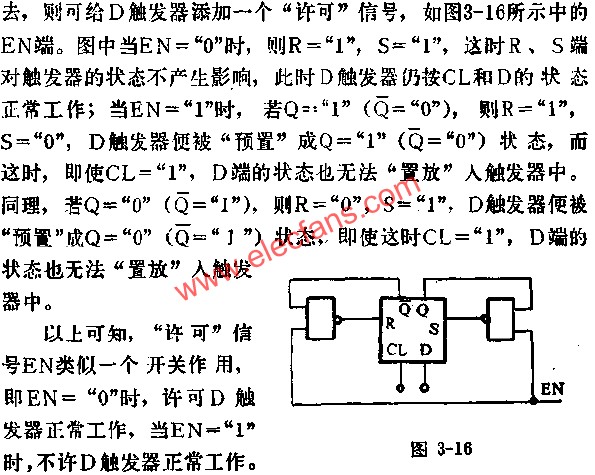

從D觸發器的真值表可知,當時鐘脈沖CL="1"時,數據輸入端D的狀態會被“置放”入觸發器中去,而與觸發器原狀無關。如果當時鐘沖CL="1",D端狀態不旋轉放入

2010-09-21 01:27:59 577

577

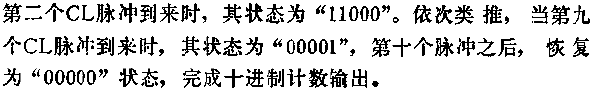

圖中所示是用CMOS電路D觸發器組成的十進制環形計數器.圖中先將D觸發器拼成移位寄存器,然后把最后一級D觸發器

2010-09-20 23:46:58 17359

17359

圖中所示是用CMOS電路D觸發器組成T型觸發器和J-K觸發器線路。圖示線路將D觸發器的Q端與D端相連,就可組成T

2010-09-20 03:31:35 15895

15895 觸發器的相互轉換 基本觸發器之間是可以互相轉換的,JK觸發器和D觸發器是兩種最常用的觸發器,別的觸發器可以通過這兩種觸發器轉化得來,它們

2010-09-18 08:56:19 3600

3600

本次重點內容:1、觸發器的概念和分類。2、同步觸發器、主從觸發器、邊沿觸發器的含義。

4.1.1 觸發器概述一、觸發

2010-08-19 08:57:47 18499

18499 1、掌握鎖存器、觸發器的電路結構和工作原理;

2、熟練掌握SR觸發器、JK觸發器、D觸發器及T 觸發器的邏輯功能;

3、正確理解鎖存器、觸發器的動態特性

2010-08-18 16:39:35 233

233 教學目標:1、 掌握鐘控同步RS觸發器的電路組成2、 掌握鐘控同步RS觸發器的工作原理及邏輯功能3、 了解觸發器的應用教學重難點:重點:鐘控同步 RS 觸

2010-08-18 14:57:41 16

16 一、空翻問題由于在CP=1期間,同步觸發器的觸發引導門都是開放的,觸發器都可以接收輸入信號而翻轉,所以在CP=1期間,如果輸入信號發生多次變化,觸發器的

2010-08-18 09:08:32 18635

18635

由與非門構成的同步RS觸發器如圖13-5(a)所示,其邏輯符號如圖13-5(b)所示。圖中門A和B構成基本觸發器,門C和E構成觸發引導電路。由圖13-5(a)可見,基本觸發器的輸

2010-08-18 09:00:00 14775

14775

觸發器的分類, 觸發器的電路

雙穩態器件有兩類:一類是觸發器,一類是鎖存器。鎖存器是觸發器的原始形式。基本

2010-03-09 09:59:59 1491

1491 施密特觸發器,施密特觸發器是什么意思

施密特觸發器也有兩個穩定狀態,但與一般觸發器不同的是,施密特觸發器采用電位觸發

2010-03-08 14:14:56 1763

1763 什么是RS觸發器,RS觸發器的工作原理是什么?

主從RS觸發器

2010-03-08 14:00:11 29331

29331 D觸發器工作原理是什么?

邊沿D 觸發器:

負跳沿觸發的主從觸發器工作時,必須在正跳沿前加入輸入信號。如果在CP 高電平期間輸入端出

2010-03-08 13:56:50 68940

68940

D觸發器,D觸發器是什么意思

邊沿D 觸發器: 電平觸發的主從觸發器工作時,必須在正跳沿前加入輸入信號。如果在CP 高

2010-03-08 13:53:13 4130

4130 JK觸發器原理是什么?

JK觸發器是一種功能較完善,應用很廣泛的雙穩態觸發器。圖9-5(a)所示是一種典型結構的JK觸發器——主從型JK觸

2010-03-08 13:41:11 23241

23241 JK觸發器,JK觸發器是什么意思

1.主從JK觸發器主從結構觸發器也可以徹底解決直接控制,防止空翻。這里以性能優良、廣泛使用的主從JK觸發器為

2010-03-08 13:36:29 5842

5842 CMOS觸發器的結構與工作原理

CMOS D觸發器足主-從結構形式的一種邊沿觸發器,CMOS T型觸發器、JK觸發器、計數單元、移位單元和各種時序電路都由其組成,因此儀

2009-10-17 08:52:27 6774

6774

維持阻塞D觸發器

(a) 邏輯電路 &

2009-09-30 18:23:59 17890

17890

40174 CMOS 六D觸發器:

2009-08-08 11:32:28 46

46 D觸發器實現二分頻電路(D觸發器構成的2分頻電路)&

2009-06-12 13:58:56 73460

73460

D觸發器的制作及電路圖

2009-05-19 09:35:49 33

33

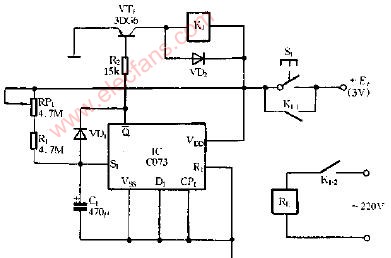

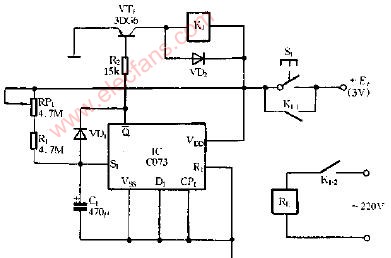

D觸發器構成的定時電路圖

2009-05-08 15:15:26 3107

3107

D觸發器電路圖

2009-05-08 14:26:44 3484

3484

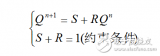

4.2.2 同步觸發器二、同步D觸發器1.電路結構2.邏輯功能3.特性方程4.狀態轉換圖三、同步JK觸發器1.電路結構2.邏輯功能3.特性方程4.狀態轉換

2009-03-30 16:17:07 3444

3444

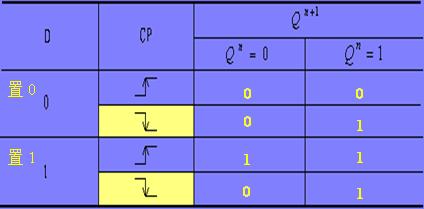

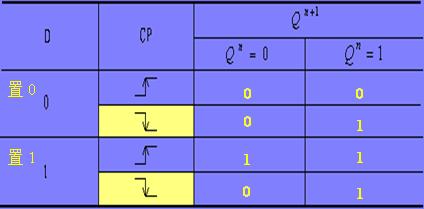

D觸發器邏輯功能表

同

2009-03-18 20:13:59 43773

43773

D觸發器的功能測試74LS74型雙D觸發器芯片引腳圖,D觸發器功能測試的引腳連線圖,D觸發器功能測試的引腳連線圖,用D觸發器構成二進制計數器,用D觸發器構成四位移位寄存器

J-K

2009-02-14 15:27:51 290

290 一、實驗目的1、掌握基本RS、JK、D和T觸發器的邏輯功能2、掌握集成觸發器的邏輯功能及使用方法3、熟悉觸發器之間相互轉換的方法二、實驗原理觸發器具有兩個穩

2008-12-19 00:40:23 48

48 同步式D觸發器邏輯電路圖

2008-10-20 09:58:19 7678

7678

D觸發器

同步式D觸發器邏輯電路圖

D觸發器功能

2008-10-20 09:57:54 1846

1846

【本章主要講授內容】 1.觸發器的性質與分類; 2.觸發器的功能; 3.觸發器的結構和觸發方式; 4.觸發器的時間參數。【本章重點、難點內容】

2008-10-20 09:53:54 59

59 d觸發器芯片有:

74HC74 74LS90? 雙D觸發器74LS74?

74LS364八D觸發器(三態)

2008-01-22 12:42:33 43218

43218

cd4013雙d觸發器

CD4013雙D觸發器做的脈沖4分頻器應用

-----------------------------. ┌─────

2008-01-09 23:48:45 4487

4487 D觸發器真值表分析:

1. D 觸發器真值表

Dn

2007-09-11 23:15:20 17600

17600 CD4013 雙D觸發器 *CD4027 雙JK觸發器 *CD4042 四鎖存D型觸發器 *CD4043

2006-04-17 21:18:32 3219

3219

當CP=0時,觸發器的狀態Q維持不變。當CP=1時,若D=1,則S=1,

當CP=0時,觸發器的狀態Q維持不變。當CP=1時,若D=1,則S=1, =0,故Qn+1=1;若D=0,則S=0,R=

=0,故Qn+1=1;若D=0,則S=0,R= S=1,故Qn+1=0。由此得到同步D觸發器的狀態轉移真值表13-6,由狀態轉移真值表可直接列出同步D觸發器的狀態方程Qn+1=D

S=1,故Qn+1=0。由此得到同步D觸發器的狀態轉移真值表13-6,由狀態轉移真值表可直接列出同步D觸發器的狀態方程Qn+1=D

電子發燒友App

電子發燒友App

評論