觸發(fā)器(trigger)是SQL server 提供給程序員和數(shù)據(jù)分析員來保證數(shù)據(jù)完整性的一種方法,是一種特殊類型的存儲過程,它是與表事件相關(guān)的特殊的存儲過程,它的執(zhí)行不是由程序調(diào)用,也不是手工啟動,而是由事件來觸發(fā),比如當對一個表進行操作( insert,delete, update)時就會激活它執(zhí)行。觸發(fā)器經(jīng)常用于加強數(shù)據(jù)的完整性約束和業(yè)務(wù)規(guī)則等。 觸發(fā)器可以從 DBA_TRIGGERS ,USER_TRIGGERS 數(shù)據(jù)字典中查到。SQL3的觸發(fā)器是一個能由系統(tǒng)自動執(zhí)行對數(shù)據(jù)庫修改的語句。

觸發(fā)器與存儲過程的唯一區(qū)別是觸發(fā)器不能執(zhí)行EXECUTE語句調(diào)用,而是在用戶執(zhí)行Transact-SQL語句時自動觸發(fā)執(zhí)行。

在Oracle中,觸發(fā)器是一種特殊的存儲過程,它在發(fā)生某種數(shù)據(jù)庫事件時由Oracle系統(tǒng)自動觸發(fā)發(fā)器,通常用于加強數(shù)據(jù)的完整性約束和業(yè)務(wù)規(guī)則等。

什么是觸發(fā)器---觸發(fā)器的功能

① 完成比約束更復雜的數(shù)據(jù)約束:觸發(fā)器可以實現(xiàn)比約束更為復雜的數(shù)據(jù)約束

② 檢查所做的SQL是否允許:觸發(fā)器可以檢查SQL所做的操作是否被允許。例如:在產(chǎn)品庫存表里,如果要刪除一條產(chǎn)品記錄,在刪除記錄時,觸發(fā)器可以檢查該產(chǎn)品庫存數(shù)量是否為零,如果不為零則取消該刪除操作。

③ 修改其它數(shù)據(jù)表里的數(shù)據(jù):當一個SQL語句對數(shù)據(jù)表進行操作的時候,觸發(fā)器可以根據(jù)該SQL語句的操作情況來對另一個數(shù)據(jù)表進行操作。例如:一個訂單取消的時候,那么觸發(fā)器可以自動修改產(chǎn)品庫存表,在訂購量的字段上減去被取消訂單的訂購數(shù)量。

④ 調(diào)用更多的存儲過程:約束的本身是不能調(diào)用存儲過程的,但是觸發(fā)器本身就是一種存儲過程,而存儲過程是可以嵌套使用的,所以觸發(fā)器也可以調(diào)用一個或多過存儲過程。

⑤ 發(fā)送SQL Mail:在SQL語句執(zhí)行完之后,觸發(fā)器可以判斷更改過的記錄是否達到一定條件,如果達到這個條件的話,觸發(fā)器可以自動調(diào)用SQL Mail來發(fā)送郵件。例如:當一個訂單交費之后,可以物流人員發(fā)送Email,通知他盡快發(fā)貨。

⑥ 返回自定義的錯誤信息:約束是不能返回信息的,而觸發(fā)器可以。例如插入一條重復記錄時,可以返回一個具體的友好的錯誤信息給前臺應(yīng)用程序。

⑦ 更改原本要操作的SQL語句:觸發(fā)器可以修改原本要操作的SQL語句,例如原本的SQL語句是要刪除數(shù)據(jù)表里的記錄,但該數(shù)據(jù)表里的記錄是最要記錄,不允許刪除的,那么觸發(fā)器可以不執(zhí)行該語句。

⑧ 防止數(shù)據(jù)表構(gòu)結(jié)更改或數(shù)據(jù)表被刪除:為了保護已經(jīng)建好的數(shù)據(jù)表,觸發(fā)器可以在接收到Drop和Alter開頭的SQL語句里,不進行對數(shù)據(jù)表的操作。

什么是觸發(fā)器---觸發(fā)器的組成

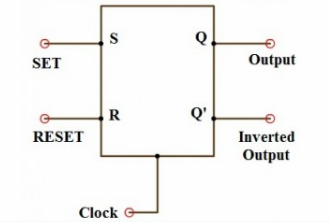

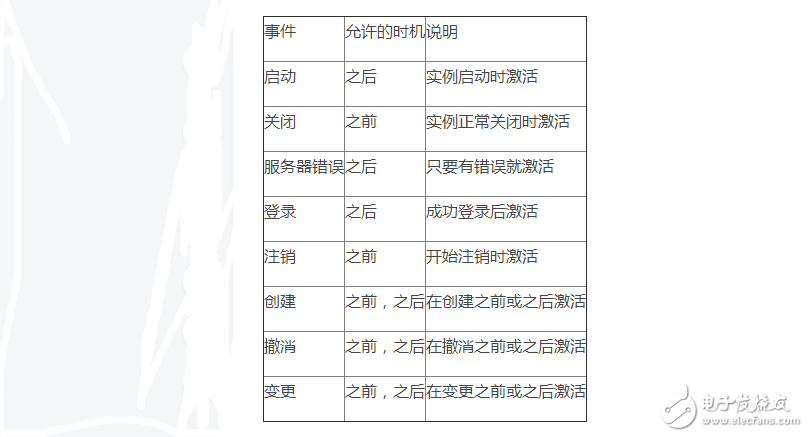

1. 觸發(fā)事件:引起觸發(fā)器被觸發(fā)的事件。 例如:DML語句(INSERT, UPDATE, DELETE語句對表或視圖執(zhí)行數(shù)據(jù)處理操作)、DDL語句(如CREATE、ALTER、DROP語句在數(shù)據(jù)庫中創(chuàng)建、修改、刪除模式對象)、數(shù)據(jù)庫系統(tǒng)事件(如系統(tǒng)啟動或退出、異常錯誤)、用戶事件(如登錄或退出數(shù)據(jù)庫)。

2. 觸發(fā)時間:即該TRIGGER是在觸發(fā)事件發(fā)生之前(BEFORE)還是之后(AFTER)觸發(fā),也就是觸發(fā)事件和該TRIGGER的操作順序。

3. 觸發(fā)操作:即該TRIGGER 被觸發(fā)之后的目的和意圖,正是觸發(fā)器本身要做的事情。 例如:PL/SQL塊。

4. 觸發(fā)對象:包括表、視圖、模式、數(shù)據(jù)庫。只有在這些對象上發(fā)生了符合觸發(fā)條件的觸發(fā)事件,才會執(zhí)行觸發(fā)操作。

5. 觸發(fā)條件:由WHEN子句指定一個邏輯表達式。只有當該表達式的值為TRUE時,遇到觸發(fā)事件才會自動執(zhí)行觸發(fā)器,使其執(zhí)行觸發(fā)操作。

6. 觸發(fā)頻率:說明觸發(fā)器內(nèi)定義的動作被執(zhí)行的次數(shù)。即語句級(STATEMENT)觸發(fā)器和行級(ROW)觸發(fā)器。

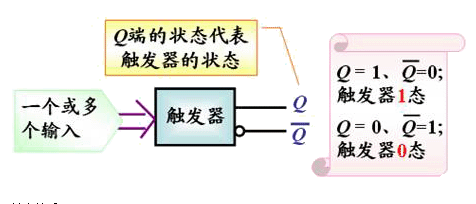

什么觸發(fā)器---觸發(fā)器的基本特性

觸發(fā)器有三個基本特性:

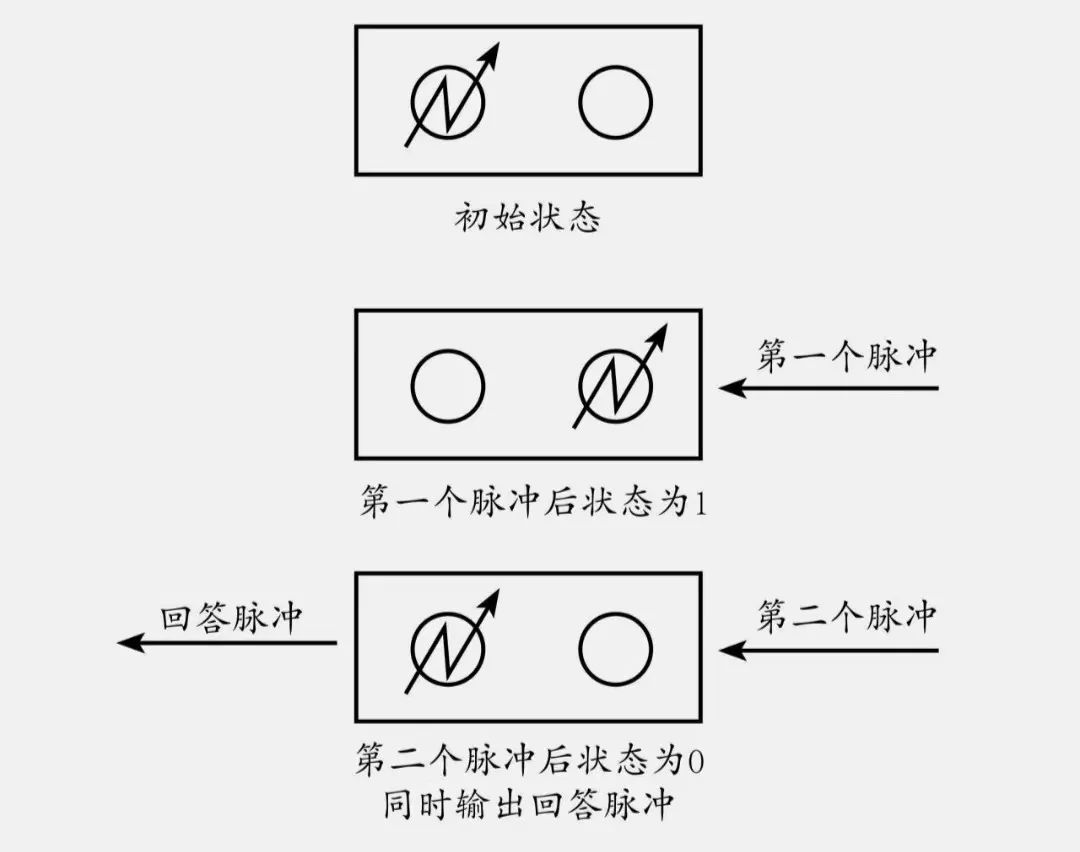

(1)有兩個穩(wěn)態(tài),可分別表示二進制數(shù)碼0和1,無外觸發(fā)時可維持穩(wěn)態(tài);

(2)外觸發(fā)下,兩個穩(wěn)態(tài)可相互轉(zhuǎn)換(稱翻轉(zhuǎn)),已轉(zhuǎn)換的穩(wěn)定狀態(tài)可長期保持下來,這就使得觸發(fā)器能夠記憶二進制信息,常用作二進制存儲單元。

? ? ? ??

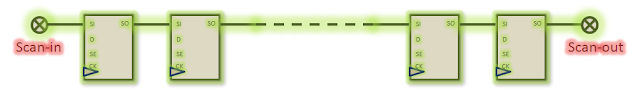

由于觸發(fā)器有兩個穩(wěn)定狀態(tài),它就有一定的記憶功能,使用一個觸發(fā)器可以記憶外部事件的兩種狀態(tài),如果需要記憶更多的狀態(tài),就要通過多個觸發(fā)器的連接來實現(xiàn)。由于一位二進制數(shù)也只有0和1兩個狀態(tài),所以,一個觸發(fā)器可以記憶一位二進制數(shù),N個觸發(fā)器,可以記憶N位二進制數(shù)。

什么是觸發(fā)器---觸發(fā)器的基本特點

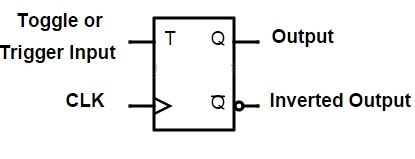

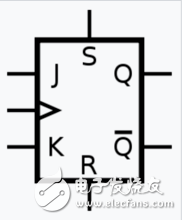

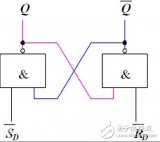

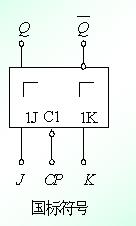

(1)具有兩個互補輸出端Q和/Q;

(2)具有“0”態(tài)和“1”態(tài)兩個穩(wěn)定狀態(tài);

(3)在外部信號作用下可實現(xiàn)狀態(tài)轉(zhuǎn)換,即翻轉(zhuǎn);

(4)外部信號消失時具有記憶功能,這就使得觸發(fā)器能夠記憶二進制信息。

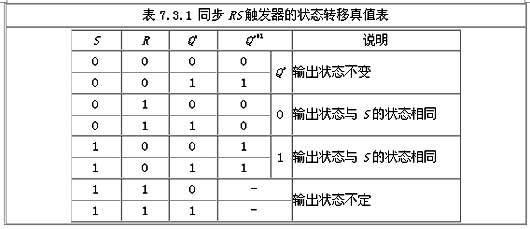

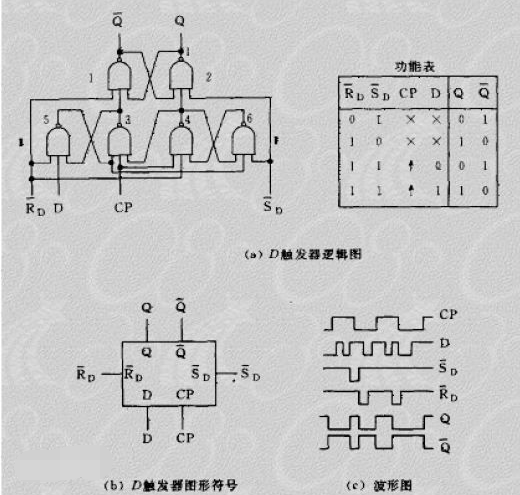

觸發(fā)器邏輯功能的表示方法有:

(1)狀態(tài)表或功能表:狀態(tài)表中包括輸入激勵信號取值,觸發(fā)器的原始狀態(tài)(亦稱初態(tài))取值和翻轉(zhuǎn)后的狀態(tài)(亦稱次態(tài))的取值。而功能表則只列出輸入激勵信號取值和觸發(fā)器次態(tài)取值,比較簡潔。

(2)狀態(tài)方程:由狀態(tài)表歸納而列寫出的邏輯方程。

(3)狀態(tài)轉(zhuǎn)換圖。

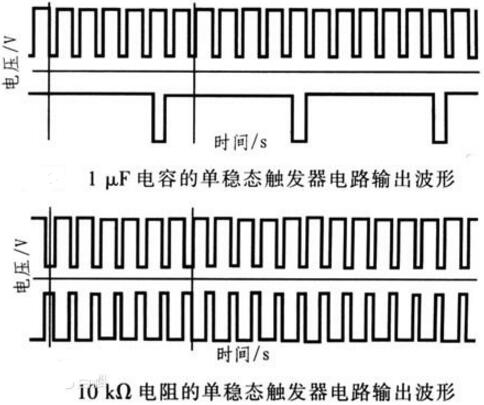

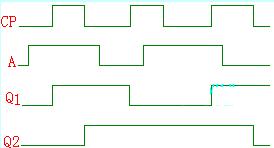

(4)波形圖(又稱時序圖):畫出對應(yīng)輸入狀態(tài)波形的輸出狀態(tài)波形。

鎖存器和觸發(fā)器的區(qū)別

鎖存器和觸發(fā)器是具有記憶功能的二進制存貯器件,是組成各種時序邏輯電路的基本器件之一。區(qū)別為:latch同其所有的輸入信號相關(guān),當輸入信號變化時latch就變化,沒有時鐘端;flip-flop受時鐘控制,只有在時鐘觸發(fā)時才采樣當前的輸入,產(chǎn)生輸出。當然因為latch和flip-flop二者都是時序邏輯,所以輸出不但同當前的輸入相關(guān)還同上一時間的輸出相關(guān)。

1、latch由電平觸發(fā),非同步控制。在使能信號有效時latch相當于通路,在使能信號無效時latch保持輸出狀態(tài)。DFF由時鐘沿觸發(fā),同步控制。

2、latch對輸入電平敏感,受布線延遲影響較大,很難保證輸出沒有毛刺產(chǎn)生;DFF則不易產(chǎn)生毛刺。

3、如果使用門電路來搭建latch和DFF,則latch消耗的門資源比DFF要少,這是latch比DFF優(yōu)越的地方。所以,在ASIC中使用 latch的集成度比DFF高,但在FPGA中正好相反,因為FPGA中沒有標準的latch單元,但有DFF單元,一個LATCH需要多個LE才能實現(xiàn)。latch是電平觸發(fā),相當于有一個使能端,且在激活之后(在使能電平的時候)相當于導線了,隨輸出而變化。在非使能狀態(tài)下是保持原來的信號,這就可以看出和flip-flop的差別,其實很多時候latch是不能代替ff的。 4、latch將靜態(tài)時序分析變得極為復雜。

5、目前l(fā)atch只在極高端電的路中使用,如intel 的P4等CPU。 FPGA中有l(wèi)atch單元,寄存器單元就可以配置成latch單元,在xilinx v2p的手冊將該單元成為register/latch單元,附件是xilinx半個slice的結(jié)構(gòu)圖。

一般的設(shè)計規(guī)則是:在絕大多數(shù)設(shè)計中避免產(chǎn)生latch。它會讓您設(shè)計的時序完蛋,并且它的隱蔽性很強,非老手不能查出。latch最大的危害在于不能過濾毛刺。這對于下一級電路是極其危險的。所以,只要能用D觸發(fā)器的地方,就不用latch。

有些地方?jīng)]有時鐘,也只能用latch了。比如現(xiàn)在用一個clk接到latch的使能端(假設(shè)是高電平使能),這樣需要的setup時間,就是數(shù)據(jù)在時鐘的下降沿之前需要的時間,但是如果是一個DFF,那么setup時間就是在時鐘的上升沿需要的時間。這就說明如果數(shù)據(jù)晚于控制信號的情況下,只能用latch,這種情況就是,前面所提到的latch timing borrow。基本上相當于借了一個高電平時間。也就是說,latch借的時間也是有限的。

對latch進行STA的分析其實也是可以,但是要對工具相當熟悉才行。不過很容易出錯。當前PrimeTime,是支持進行l(wèi)atch分析的。現(xiàn)在一些綜合工具內(nèi)置的STA分析功能也支持,比如RTL compiler, Design Compiler.除了ASIC里可以節(jié)省資源以外。latch在同步設(shè)計里出現(xiàn)的可能還是挺小的,現(xiàn)在處理過程中大都放在ff里打一下。

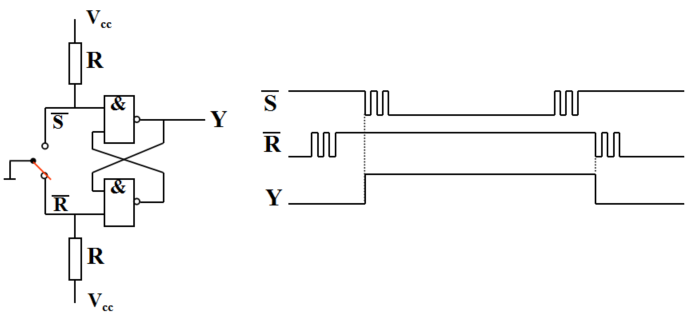

觸發(fā)器的觸發(fā)方式

觸發(fā)方式是研究觸發(fā)器翻轉(zhuǎn)時刻與時鐘脈沖間的關(guān)系,在各類觸發(fā)器中,存在三種觸發(fā)方式:電平觸發(fā)方式、主從觸發(fā)方式、邊沿觸發(fā)方式。

1、電平觸發(fā)方式

電平觸發(fā)方式分為二種:高電平觸發(fā)方式(在時鐘脈沖C=1期間翻轉(zhuǎn));低電平觸發(fā)方式(在時鐘脈沖C=0期間翻轉(zhuǎn))。

電平觸發(fā)方式結(jié)構(gòu)簡單、觸發(fā)速度快。在時鐘信號有效電平期間(C=1或C=0),觸發(fā)器總是處于可翻轉(zhuǎn)狀態(tài),輸入信號的變化都會引起觸發(fā)器狀態(tài)的變化。在時鐘信號無效電平期間,觸發(fā)器狀態(tài)保持不變。因此,在時鐘信號有效電平寬度較寬時,觸發(fā)器會連續(xù)不停地翻轉(zhuǎn)。如果要求每來一個C脈沖觸發(fā)器僅翻轉(zhuǎn)一次的話,則對時鐘脈沖的有效電平的寬度要求極為苛刻,所以實際中應(yīng)用并不廣泛。

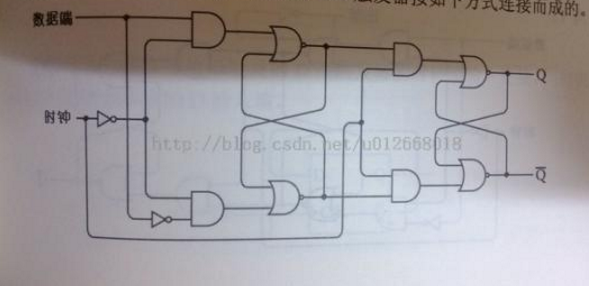

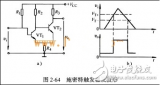

2、主從觸發(fā)方式

主從型JK觸發(fā)器、由主從型JK觸發(fā)器轉(zhuǎn)換的各種功能的觸發(fā)器都屬于這種觸發(fā)方式。這種觸發(fā)方式的工作特點是:克服了在C有效電平期間多次翻轉(zhuǎn)現(xiàn)象,具有一次翻轉(zhuǎn)特性。就是說,在C有效電平期間,主觸發(fā)器接受了輸入信號發(fā)生一次翻轉(zhuǎn)后,主觸發(fā)器狀態(tài)就一直保持不變,也不再隨輸入信號J。K的變化而變化。一次翻轉(zhuǎn)特性有利有弊:利在于克服了空翻現(xiàn)象;弊是帶來了抗干擾能力差的問題。

3、邊沿觸發(fā)方式

為了免除C=1期間輸入信號不許擾動的限制,可采用邊沿觸發(fā)方式。其特點是:觸發(fā)器只在時鐘跳轉(zhuǎn)時刻發(fā)生翻轉(zhuǎn),而在C=1或C=0期間,輸入端的任何變化都不影響輸出。比如前面介紹過的維持阻塞型的D觸發(fā)器。除此以外,當然也有邊沿觸發(fā)的JK觸發(fā)器。

如果翻轉(zhuǎn)發(fā)生在上升沿就叫“前邊沿觸發(fā)或正邊沿觸發(fā)”。如果翻轉(zhuǎn)發(fā)生在下降沿就叫“后邊沿觸發(fā)”或“負邊沿觸發(fā)”。

電子發(fā)燒友App

電子發(fā)燒友App

評論