在一篇以前的文章中,Timothy T.曾談到JESD204B接口標(biāo)準(zhǔn)(該標(biāo)準(zhǔn)越來越受歡迎,因為它能在高速數(shù)據(jù)采集系統(tǒng)里簡化設(shè)計)的時鐘要求。在本文中,筆者將談?wù)摱秳雍铣善髋c清除器的不同系統(tǒng)參考信號(SYSREF)模式,以及如何用它們來最大限度地提高JESD204B時鐘方案的性能。

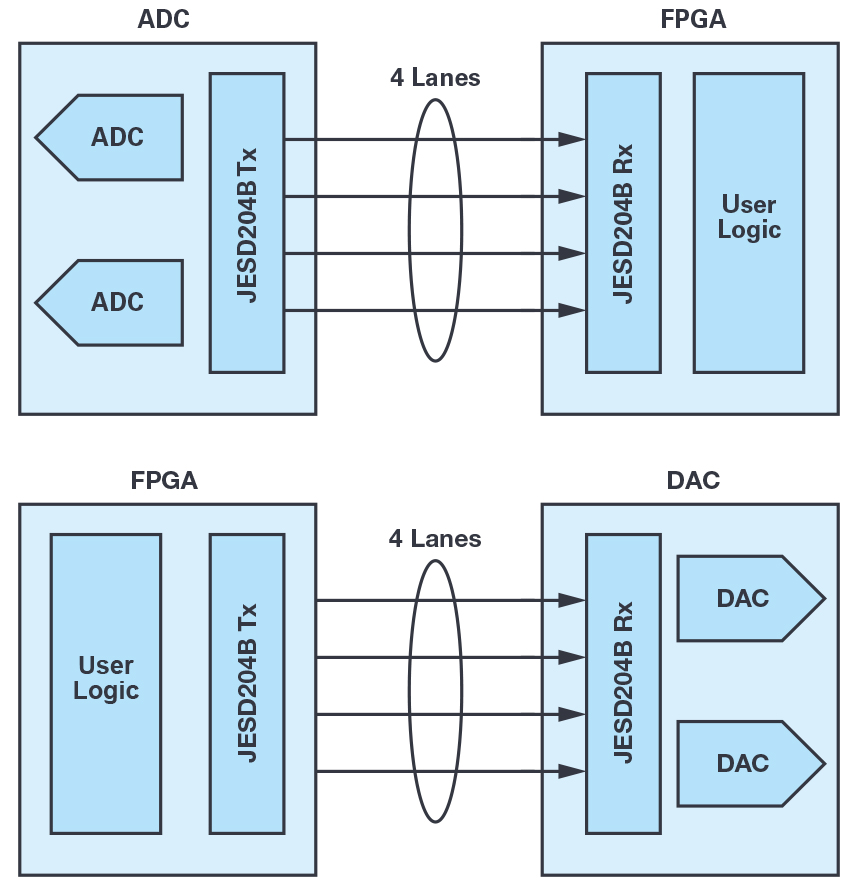

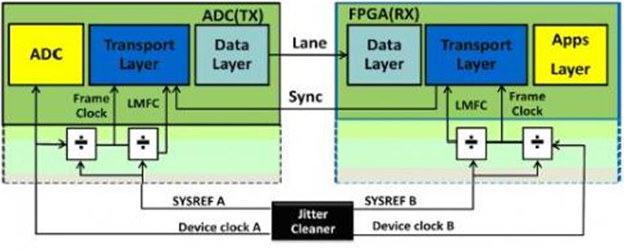

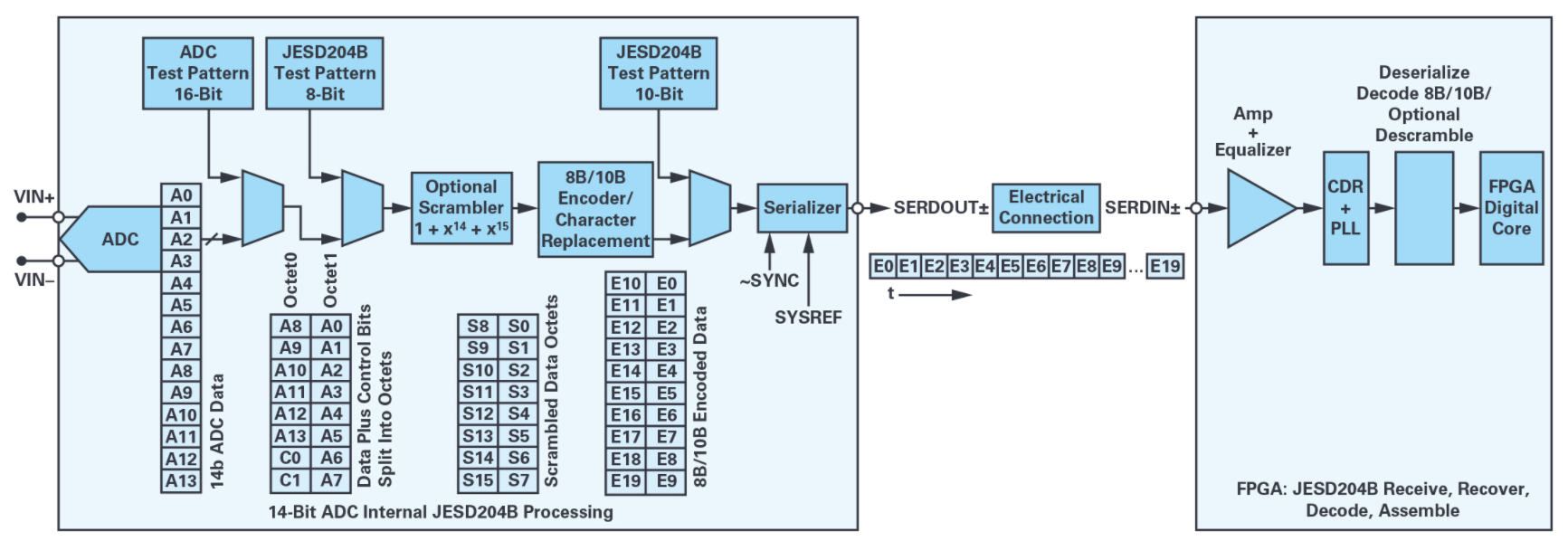

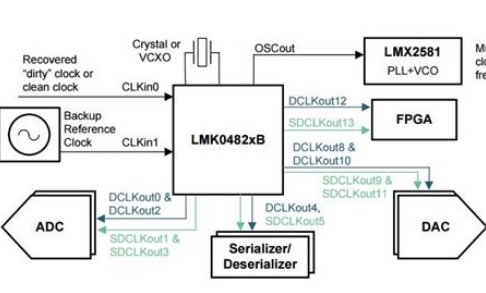

LMK04821系列器件為該話題提供了很好的范例研究素材,因為它們是高性能的雙環(huán)路抖動清除器,可在具有器件和SYSREF時鐘的子類1時鐘方案里驅(qū)動多達(dá)七個JESD204B轉(zhuǎn)換器或邏輯器件。圖1是典型JESD204B系統(tǒng)(以LMK04821系列器件作為時鐘解決方案)的高級方框圖。

圖1:典型的JEDEC JESD204B應(yīng)用方框圖

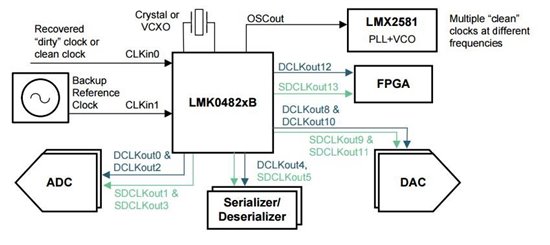

LMK04821憑借來自第二鎖相環(huán)(PLL)電壓控制振蕩器的單個SYSREF時鐘分頻器來產(chǎn)生SYSREF信號。信號從分頻器被分配到個別的輸出路徑。每個輸出路徑均包含數(shù)字和模擬延遲,以調(diào)節(jié)與器件時鐘有關(guān)的SYSREF相位。

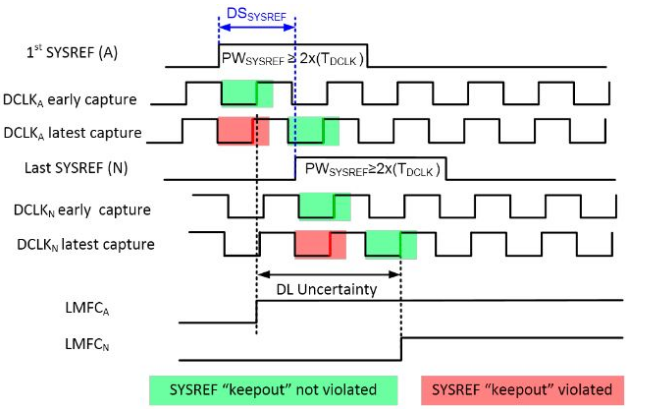

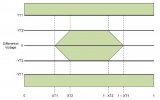

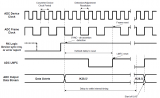

根據(jù)JESD204B標(biāo)準(zhǔn),SYSREF可采用不同的模式,如圖2所示。它可以是連續(xù)性(也稱為周期性)、有間隙的周期性或一次性信號。連續(xù)性和有間隙的周期性SYSREF的周期必須是本地多幀時鐘(LMFC)的整數(shù)倍,以避免多幀中間的SYSREF脈沖。

連續(xù)性模式允許連續(xù)性輸出。由于從SYSREF至器件時鐘存在串?dāng)_,因此許多開發(fā)人員不用連續(xù)性模式。但是,連續(xù)性模式使系統(tǒng)開發(fā)人員能在兩個信號之間手動設(shè)置恰當(dāng)?shù)拇_定性相位關(guān)系。設(shè)置后,它可變?yōu)橛虚g隙的周期性SYSREF。

在有間隙的周期性或一次性模式中,SYSREF時鐘分頻器的輸出通過脈沖發(fā)生器被饋送給輸出路徑。脈沖發(fā)生器用門控制SYSREF信號,只讓少數(shù)脈沖通過。脈沖數(shù)可被設(shè)定為一個、兩個、四個或八個。因為沒有周期性信號,所以從SYSREF至器件時鐘的串?dāng)_被最大限度地減少。

LMK0482x中另一類有間隙的周期性SYSREF模式是請求模式,只要SYNC/SYSREF_REQ引腳為高電平,該模式就能輸出SYSREF脈沖的連續(xù)流。

圖2:LMK0482x的SYSREF模式是:a)連續(xù)性SYSREF;b)脈沖式SYSREF(一次性或有間隙的周期性模式);c)SYSREF請求(有間隙的周期性模式)

在LMK04821器件中,內(nèi)部SYSREF分配路徑與輸出分頻器同步路徑共享。因此,它需要一個特定的寄存器寫入序列,以支持同步輸出和無干擾SYSREF脈沖的產(chǎn)生。在表1中,筆者描述的方法都與它們的寄存器寫入序列一起列出。表1還展示了內(nèi)容為十進(jìn)制值的內(nèi)部寄存器字段名。具有相同編號的步驟可以互換。

?

表1:能啟用不同SYSREF模式的寄存器寫入序列

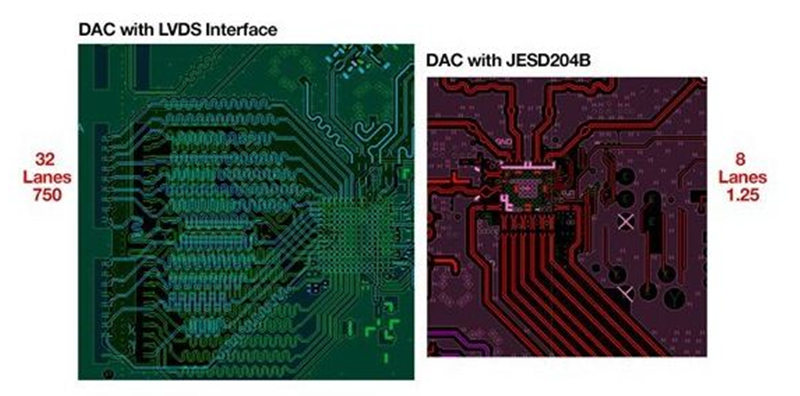

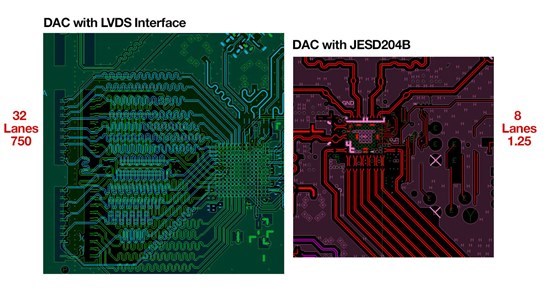

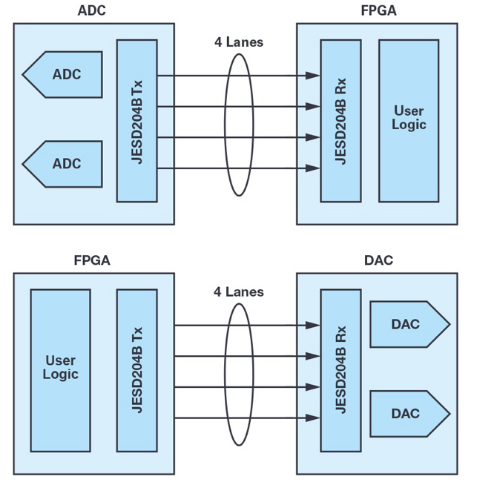

JESD204B標(biāo)準(zhǔn)是減少布局工作量,同時在信號轉(zhuǎn)換器和邏輯器件之間采用串行化數(shù)據(jù)傳輸。通過充分利用JESD204B致能時鐘器件的SYSREF模式,您可在整個系統(tǒng)中輕松創(chuàng)建確定性的相位關(guān)系。

其它資源

閱讀有關(guān)JESD204B子類的博客系列。

閱讀這篇與JESD204B子類1時鐘時序要求相關(guān)的博客文章。

閱讀Thomas Neu的白皮書 ——?《是否已準(zhǔn)備好向JESD204B跨躍?》。

閱讀這篇《模擬應(yīng)用期刊》的文章 ——?《何時JESD204B接口是正確的選擇?》。

從“時序至關(guān)重要”博客系列獲取與各種時鐘和時序設(shè)計挑戰(zhàn)相關(guān)的有用設(shè)計小貼士。

電子發(fā)燒友App

電子發(fā)燒友App

評論