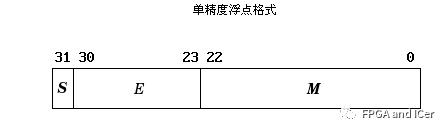

BCD碼(Binary-Coded Decimal?)亦稱(chēng)二進(jìn)碼十進(jìn)數(shù)或二-十進(jìn)制代碼。用4位二進(jìn)制數(shù)來(lái)表示1位十進(jìn)制數(shù)中的0~9這10個(gè)數(shù)碼。是一種二進(jìn)制的數(shù)字編碼形式,用二進(jìn)制編碼的十進(jìn)制代碼。BCD碼這種編碼形式利用了四個(gè)位元來(lái)儲(chǔ)存一個(gè)十進(jìn)制的數(shù)碼,使二進(jìn)制和十進(jìn)制之間的轉(zhuǎn)換得以快捷的進(jìn)行。

這種編碼技巧最常用于會(huì)計(jì)系統(tǒng)的設(shè)計(jì)里,因?yàn)闀?huì)計(jì)制度經(jīng)常需要對(duì)很長(zhǎng)的數(shù)字串作準(zhǔn)確的計(jì)算。相對(duì)于一般的浮點(diǎn)式記數(shù)法,采用BCD碼,既可保存數(shù)值的精確度,又可免去使電腦作浮點(diǎn)運(yùn)算時(shí)所耗費(fèi)的時(shí)間。此外,對(duì)于其他需要高精確度的計(jì)算,BCD編碼亦很常用。

由于十進(jìn)制數(shù)共有0、1、2、……、9十個(gè)數(shù)碼,因此,至少需要4位二進(jìn)制碼來(lái)表示1位十進(jìn)制數(shù)。4位二進(jìn)制碼共有2^4=16種碼組,在這16種代碼中,可以任選10種來(lái)表示10個(gè)十進(jìn)制數(shù)碼,共有N=16!/[10!*(16-10)!]等于8008種方案。常用的BCD代碼列于末。

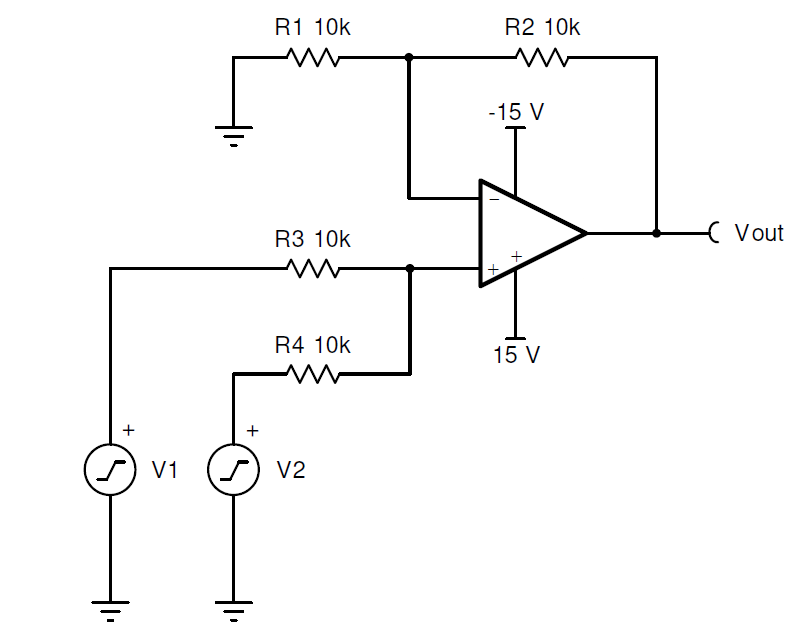

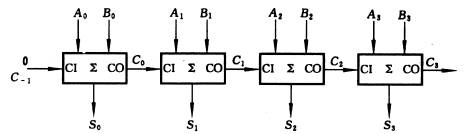

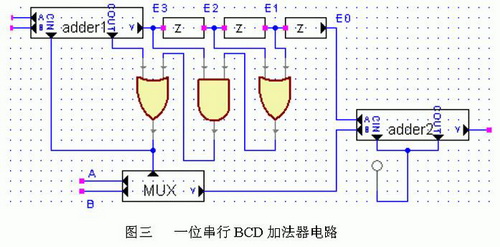

BCD碼加法器

在計(jì)算機(jī)內(nèi)部,出于存儲(chǔ)和計(jì)算方便的目的,采用基2碼對(duì)十進(jìn)制數(shù)進(jìn)行重新編碼,最少需要基2碼的位數(shù)為log210,取整數(shù)位4 ,4位基2碼有16種表示方法。

十進(jìn)制數(shù)的幾種4位編碼

8421碼又稱(chēng)BCD碼,是十進(jìn)制代碼中最常用的一種。在這種編碼方式中,每一位二值代碼的1都表示一個(gè)固定數(shù)值,將每一位的1代表的十進(jìn)制數(shù)加起來(lái),得到的結(jié)果就是它所代表的十進(jìn)制數(shù)碼。由于代碼中從左到右每一位的1分別表示8、4、2、1,所以將這種編碼稱(chēng)為8421碼。每一位的1代表的十進(jìn)制數(shù)稱(chēng)為這一位的權(quán)。8421碼中每一位的權(quán)是固定不變的,它屬于恒權(quán)代碼。

在計(jì)算機(jī)內(nèi)部實(shí)現(xiàn)BCD碼之間的算術(shù)運(yùn)算要復(fù)雜一些,即在某些情況下,對(duì)加法運(yùn)算的結(jié)果進(jìn)行修正。修正規(guī)則如下:

(1) 若兩個(gè)8421碼數(shù)相加之和等于或小于1001,不需修正。

(2) 若相加和在10-15之間,一方面應(yīng)向高位產(chǎn)生進(jìn)位,本身還要進(jìn)行加6修正,進(jìn)位是在加6修正時(shí)產(chǎn)生的。

(3) 若相加之和在16-18之間,向高位進(jìn)位會(huì)在相加過(guò)程中自己產(chǎn)生,對(duì)本位還要進(jìn)行加6修正。

實(shí)驗(yàn)代碼使用vhdl語(yǔ)言:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

ENTITY bcd IS

PORT( a : UNSIGNED(4 DOWNTO 0);

b : UNSIGNED(4 DOWNTO 0);

c : OUT STD_LOGIC_VECTOR(4 DOWNTO 0)

);

END bcd;

SIGNAL sum : STD_LOGIC_VECTOR(4 DOWNTO 0);

SIGNAL co : STD_LOGIC;

SIGNAL add : integer RANGE 0 TO 31;

BEGIN

add 《= conv_integer(a+b);

co 《= ‘1’ WHEN add》9 ELSE

‘0’;

sum 《= a+b+6 WHEN co=‘1’ ELSE

a+b;

c 《= sum;

END adding;

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論