一、什么是鎖存器

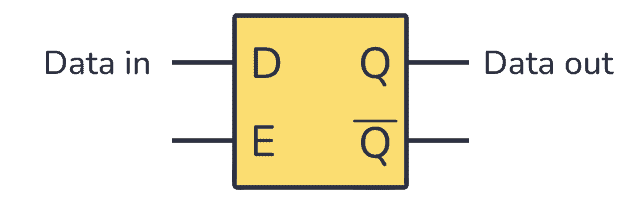

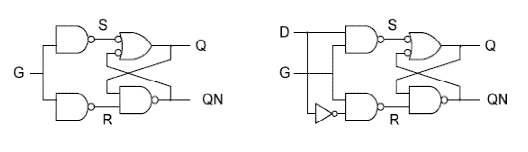

鎖存器(Latch)是一種對脈沖電平敏感的存儲單元電路,它們可以在特定輸入脈沖電平作用下改變狀態(tài)。鎖存,就是把信號暫存以維持某種電平狀態(tài)。鎖存器的最主要作用是緩存,其次完成高速的控制器與慢速的外設(shè)的不同步問題,再其次是解決驅(qū)動的問題,最后是解決一個I/O口既能輸出也能輸入的問題。鎖存器是利用電平控制數(shù)據(jù)的輸入,它包括不帶使能控制的鎖存器和帶使能控制的鎖存器。

二、鎖存器的工作原理

在LED和數(shù)碼管顯示方面,要維持一個數(shù)據(jù)的顯示,往往要持續(xù)的快速的刷新。尤其是在四段八位數(shù)碼管等這些要選通的顯示設(shè)備上。在人類能夠接受的刷新頻率之內(nèi),大概每三十毫秒就要刷新一次。這就大大占用了處理器的處理時間,消耗了處理器的處理能力,還浪費了處理器的功耗。

鎖存器的使用可以大大的緩解處理器在這方面的壓力。當處理器把數(shù)據(jù)傳輸?shù)芥i存器并將其鎖存后,鎖存器的輸出引腳便會一直保持數(shù)據(jù)狀態(tài)直到下一次鎖存新的數(shù)據(jù)為止。這樣在數(shù)碼管的顯示內(nèi)容不變之前,處理器的處理時間和IO引腳便可以釋放。可以看出,處理器處理的時間僅限于顯示內(nèi)容發(fā)生變化的時候,這在整個顯示時間上只是非常少的一個部分。而處理器在處理完后可以有更多的時間來執(zhí)行其他的任務(wù)。這就是鎖存器在LED和數(shù)碼管顯示方面的作用:節(jié)省了寶貴的MCU時間。

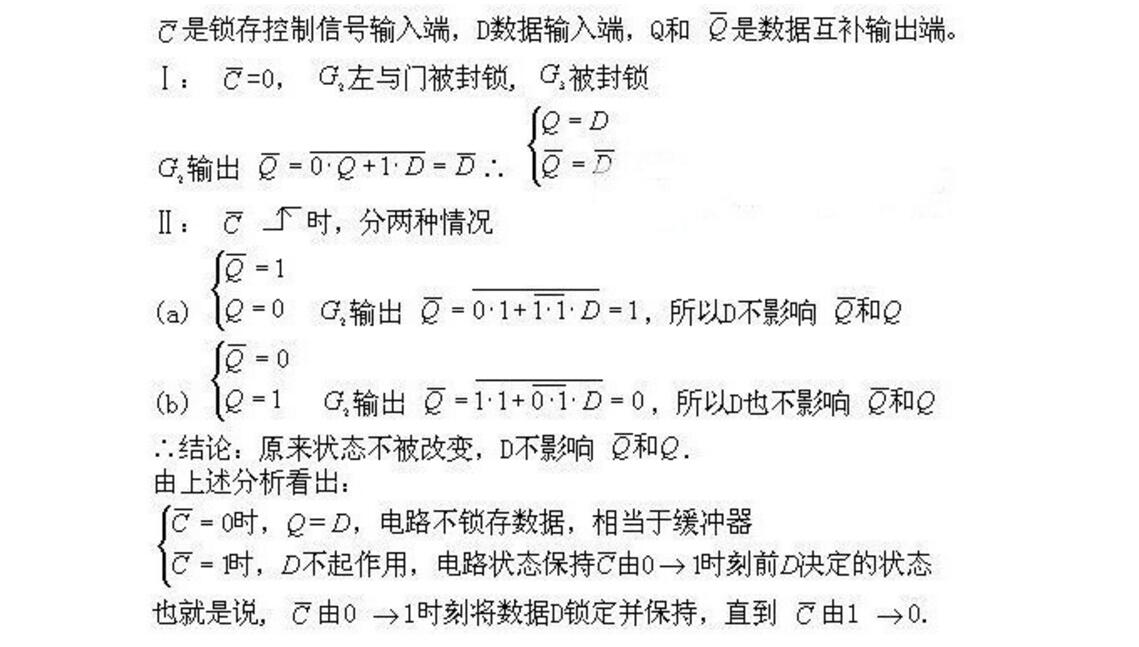

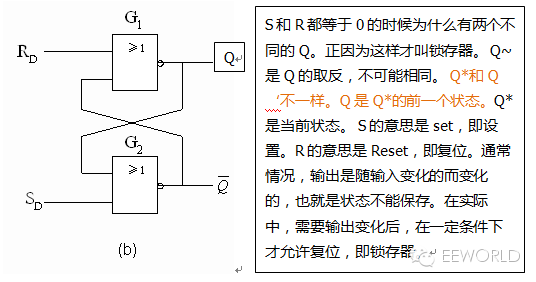

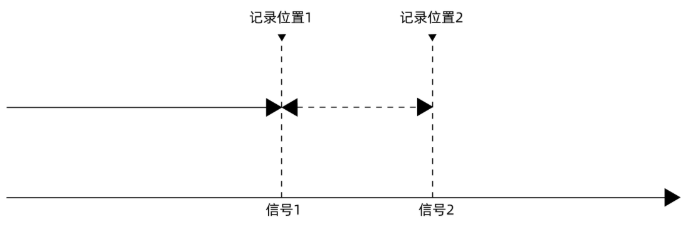

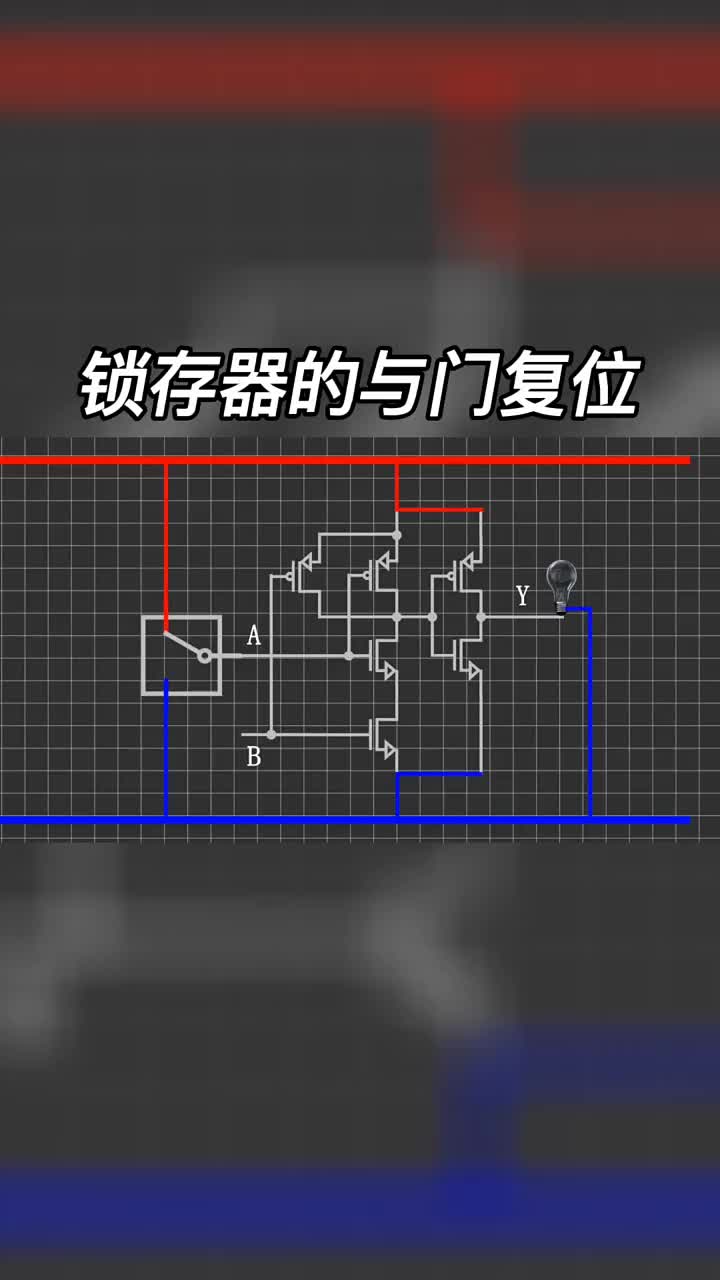

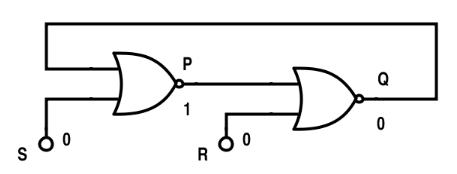

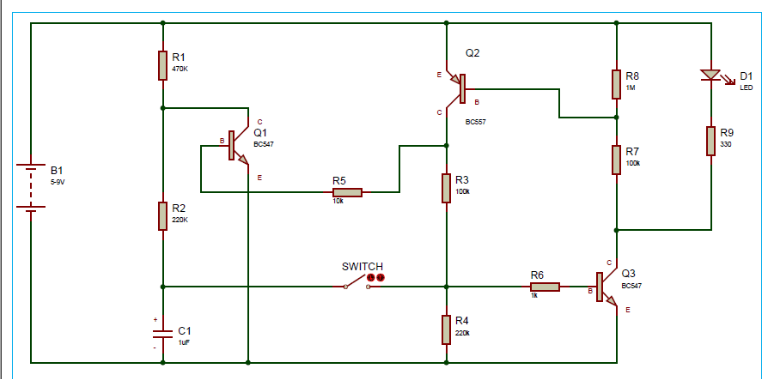

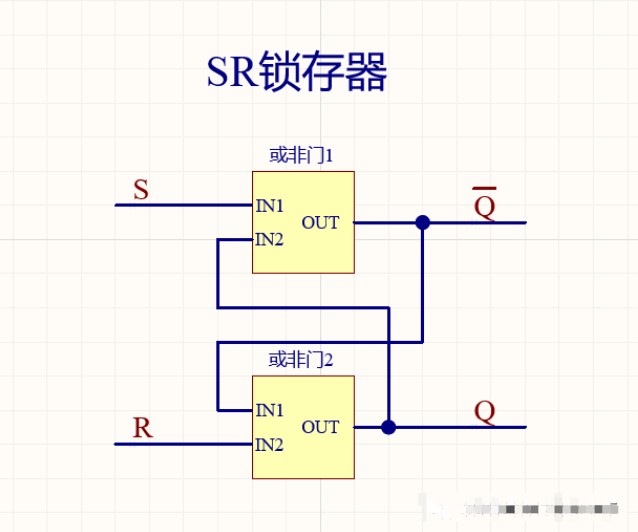

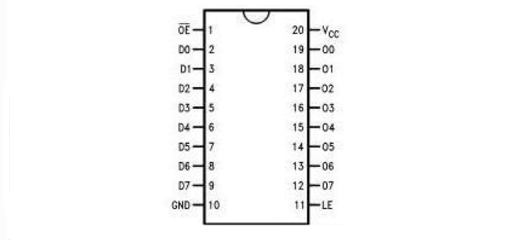

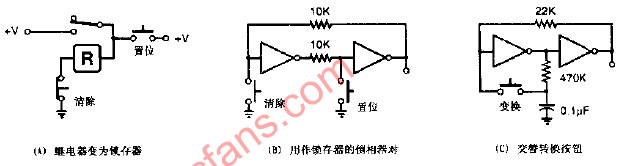

鎖存器的工作原理如下:

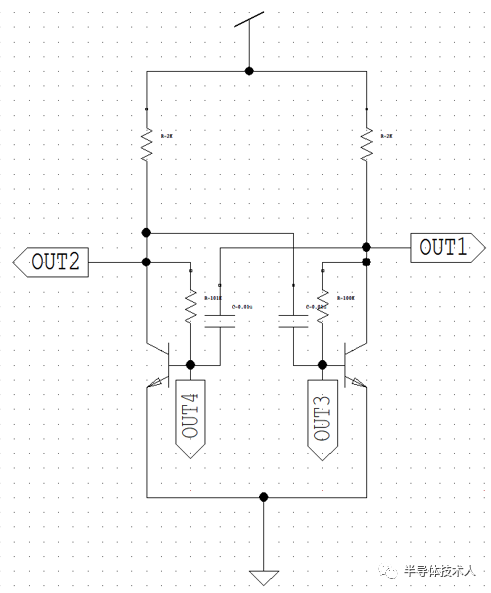

鎖存器原理圖

三、鎖存器的作用介紹

在LED和數(shù)碼管顯示方面,要維持一個數(shù)據(jù)的顯示,往往要持續(xù)的快速的刷新。尤其是在四段八位數(shù)碼管等這些要選通的顯示設(shè)備上。在人類能夠接受的刷新頻率之內(nèi),大概每三十毫秒就要刷新一次。這就大大占用了處理器的處理時間,消耗了處理器的處理能力,還浪費了處理器的功耗。

鎖存器的使用可以大大的緩解處理器在這方面的壓力。當處理器把數(shù)據(jù)傳輸?shù)芥i存器并將其鎖存后,鎖存器的輸出引腳便會一直保持數(shù)據(jù)狀態(tài)直到下一次鎖存新的數(shù)據(jù)為止。這樣在數(shù)碼管的顯示內(nèi)容不變之前,處理器的處理時間和IO引腳便可以釋放。可以看出,處理器處理的時間僅限于顯示內(nèi)容發(fā)生變化的時候,這在整個顯示時間上只是非常少的一個部分。而處理器在處理完后可以有更多的時間來執(zhí)行其他的任務(wù)。這就是鎖存器在LED和數(shù)碼管顯示方面的作用:節(jié)省了寶貴的MCU時間。

鎖存器和緩沖器的作用和區(qū)別:

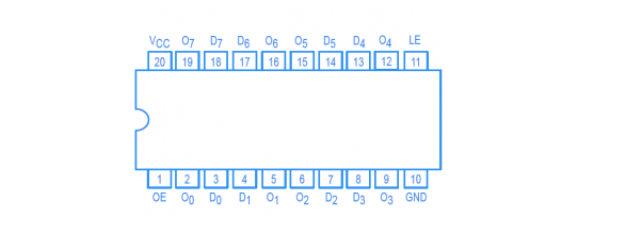

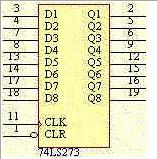

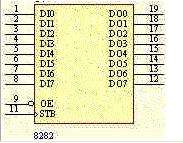

鎖存器就是把當前的狀態(tài)鎖存起來,使CPU送出的數(shù)據(jù)在接口電路的輸出端保持一段時間鎖存后狀態(tài)不再發(fā)生變化,直到解除鎖定。還有些芯片具有鎖存器,比如芯片74LS244就具有鎖存的功能,它可以通過把一個引腳置高后,輸出就會保持現(xiàn)有的狀態(tài),直到把該引腳清0后才能繼續(xù)變化。

緩沖寄存器又稱緩沖器,它分輸入緩沖器和輸出緩沖器兩種。前者的作用是將外設(shè)送來的數(shù)據(jù)暫時存放,以便處理器將它取走;后者的作用是用來暫時存放處理器送往外設(shè)的數(shù)據(jù)。有了數(shù)控緩沖器,就可以使高速工作的CPU與慢速工作的外設(shè)起協(xié)調(diào)和緩沖作用,實現(xiàn)數(shù)據(jù)傳送的同步。由于緩沖器接在數(shù)據(jù)總線上,故必須具有三態(tài)輸出功能。

電子發(fā)燒友App

電子發(fā)燒友App

評論