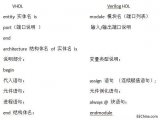

vhdl和verilog介紹

VHDL全名Very-High-Speed Integrated Circuit Hardware Description Language,誕生于1982年。1987年底,VHDL被IEEE和美國國防部確認為標準硬件描述語言 。自IEEE-1076(簡稱87版)之后,各EDA公司相繼推出自己的VHDL設計環境,或宣布自己的設計工具可以和VHDL接口。1993年,IEEE對VHDL進行了修訂,從更高的抽象層次和系統描述能力上擴展VHDL的內容,公布了新版本的VHDL,即IEEE標準的1076-1993版本,簡稱93版。VHDL和Verilog作為IEEE的工業標準硬件描述語言,得到眾多EDA公司支持,在電子工程領域,已成為事實上的通用硬件描述語言。

Verilog HDL是一種硬件描述語言(HDL:Hardware Description Language),以文本形式來描述數字系統硬件的結構和行為的語言,用它可以表示邏輯電路圖、邏輯表達式,還可以表示數字邏輯系統所完成的邏輯功能。 Verilog HDL和VHDL是世界上最流行的兩種硬件描述語言,都是在20世紀80年代中期開發出來的。前者由Gateway Design Automation公司(該公司于1989年被Cadence公司收購)開發。兩種HDL均為IEEE標準。

vhdl和verilog的共同點

1、能形式化地抽象表示電路的行為和結構;

2、支持邏輯設計中層次與范圍地描述;

3、可借用高級語言地精巧結構來簡化電路行為和結構;具有電路仿真與驗證機制以保證設計的正確性;

4、支持電路描述由高層到低層的綜合轉換;

5、硬件描述和實現工藝無關;

6、便于文檔管理;

7、易于理解和設計重用

vhdl和verilog的區別

Verilog HDL 推出已經有 20 年了,擁有廣泛的設計群體,成熟的資源也比 VHDL 豐富。 Verilog 更大的一個優勢是:它非常容易掌握,只要有 C 語言的編程基礎,通過比較短的時間,經過一些實際的操作,可以在 2 ~ 3 個月內掌握這種設計技術。而 VHDL 設計相對要難一點,這個是因為 VHDL 不是很直觀,需要有 Ada 編程基礎,一般認為至少要半年以上的專業培訓才能掌握。

目前版本的 Verilog HDL 和 VHDL 在行為級抽象建模的覆蓋面范圍方面有所不同。一般認為 Verilog 在系統級抽象方面要比 VHDL 略差一些,而在門級開關電路描述方面要強的多。

近 10 年來, EDA 界一直在對數字邏輯設計中究竟用哪一種硬件描述語言爭論不休,目前在美國,高層次數字系統設計領域中,應用 Verilog 和 VHDL 的比率是 80 %和 20 %;日本和***和美國差不多;而在歐洲 VHDL 發展的比較好。在中國很多集成電路設計公司都采用 Verilog。誰好誰壞看你個人的需求了。

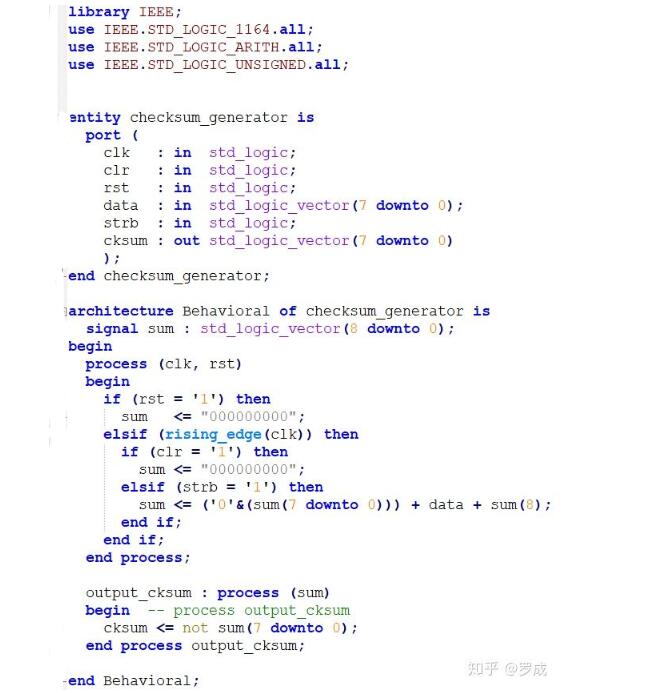

vhdl和verilog的應用實例

用VHDL/VerilogHD語言開發PLD/FPGA的完整流程為:

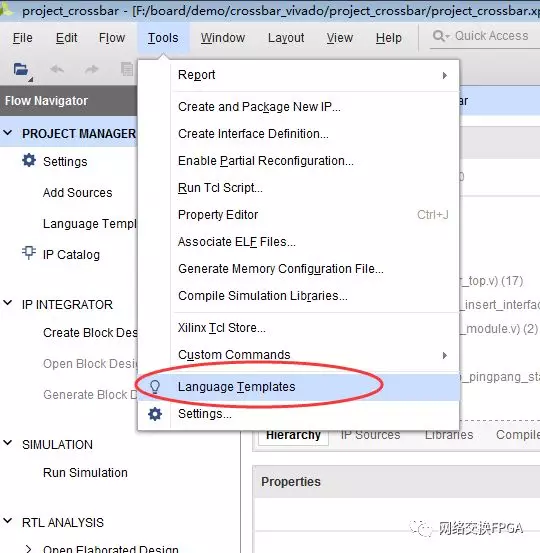

1、文本編輯:用任何文本編輯器都可以進行,也可以用專用的HDL編輯環境。通常VHDL文件保存為.vhd文件,Verilog文件保存為.v文件

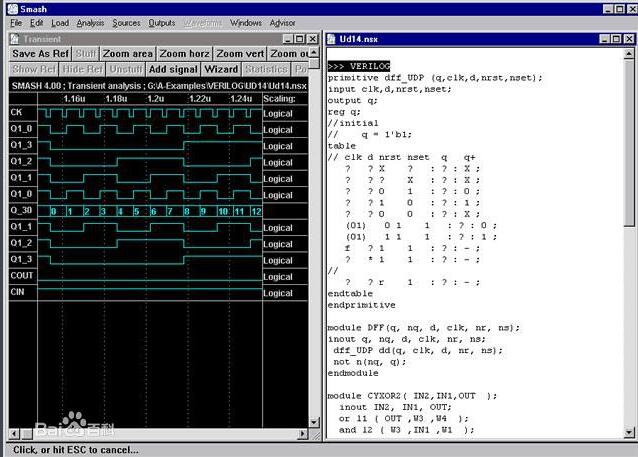

2、功能仿真:將文件調入HDL仿真軟件進行功能仿真,檢查邏輯功能是否正確(也叫前仿真,對簡單的設計可以跳過這一步,只在布線完成以后,進行時序仿真)

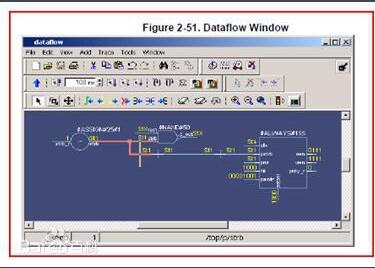

3、邏輯綜合:將源文件調入邏輯綜合軟件進行綜合,即把語言綜合成最簡的布爾表達式和信號的連接關系。邏輯綜合軟件會生成.edf(edif)的EDA工業標準文件。

4、布局布線:將.edf文件調入PLD廠家提供的軟件中進行布線,即把設計好的邏輯安放到PLD/FPGA內

5、時序仿真:需要利用在布局布線中獲得的精確參數,用仿真軟件驗證電路的時序。(也叫后仿真)

6、編程下載:確認仿真無誤后,將文件下載到芯片中 通常以上過程可以都在PLD/FPGA廠家提供的開發工具(如MAXPLUSII,Foundation,ISE)中完成,但許多集成的PLD開發軟件只支持VHDL/Verilog的子集,可能造成少數語法不能編譯,如果采用專用HDL工具分開執行,效果會更好,否則這么多出售專用HDL開發工具的公司就沒有存在的理由了。

vhdl和verilog哪個好

1、最近和朋友談到這個問題, 他們選的是 Verilog, 原因是IP 供貨商大多提供 Verilog, 如果你的 Project 是由頭做到尾都自己來, 不用別人的 IP 那么, 我想問題不大, 但如果你未來會開 ASIC 需要整合 IP 供貨商的 IP 那么建議你用 Verilog!

2、以前的一個說法是:在國外學界VHDL比較流行,在產業界Verilog比較流行。

3、說技術上有多大優勢都是沒什么意義的,有些東西也不是技術決定的,大家都覺得VHDL沒前途,它就沒有前途了。

4、 VHDL太陳腐了。Verilog2001標準剛推出來沒兩年,明年又要推出verilog2005標準了,現在草案都是第三稿了。再看看VHDL,一點發展動靜都沒有,怎么能跟得上時代的要求啊,怎么能做得了系統級概念設計、集成、仿真和驗證啊

5、verilog適合算法級,rtl,邏輯級,門級,而vhdl適合特大型的系統級設計,也就是在系統級抽象方面比verilog好。

6、I know both languages equally well.When asked which one I prefer,I usually answer that I was asked the wrong question.The right question should be“Which one do I hate the least?”And the answer to that question is :“the one I‘m not currently working with”。

7、Verilog code 運行快,simulation performance 好,所以netlist都用verilog,VHDL package 比較好,但寫得費事。

8、國內VHDL看到的更多一些,國外應該都是Verilog,你看看常見的這些EDA軟件對Verilog的支持程度就知道了,如Modelsim、Debussy、Synplify、LDV。 從我的實踐看,絕對是Verilog流行,當然,也可能是我孤陋寡聞了。選擇哪個語言其實是跟你在哪個公司上班有關,公司用哪個你就得用哪個,如果你現在還沒有上班,那你要看看你要應聘哪個公司,比如你應聘我們公司的話呢,那肯定就是Verilog了。從電路設計上說,道理都是相通的,上手還是不成問題,不過從語言、語法的角度講,差異還是很大的,要發揮語言、代碼本身的全部功能、潛力,沒有一兩年的使用是不行的。

9、應該說隨著IC設計的發展,用Verilog的越來越多,VHDL越來越少,我感覺這絕對是一個趨勢。其實語言本身是其次,重要的是你所在的團隊、公司用的是什么。你可能誤解了,國內幾個大公司IC設計都是用的Verilog,如huawei、中興等。

10、Verilog就像C,VHDL就像PASCAL。

11、VHDL比較嚴謹,Verilog比較自由,初學還是用VHDL比較好,初學用Verilog會比較容易出錯。在國外,VHDL是本科課程,Verilog是研究生課程。

電子發燒友App

電子發燒友App

評論