本文將對源同步定時如何優(yōu)化高速接口時序裕量進行討論。時序預算是對系統(tǒng)正常工作所需時序參數(shù)或時序要求的計算。

2012-03-20 10:46:32 2443

2443

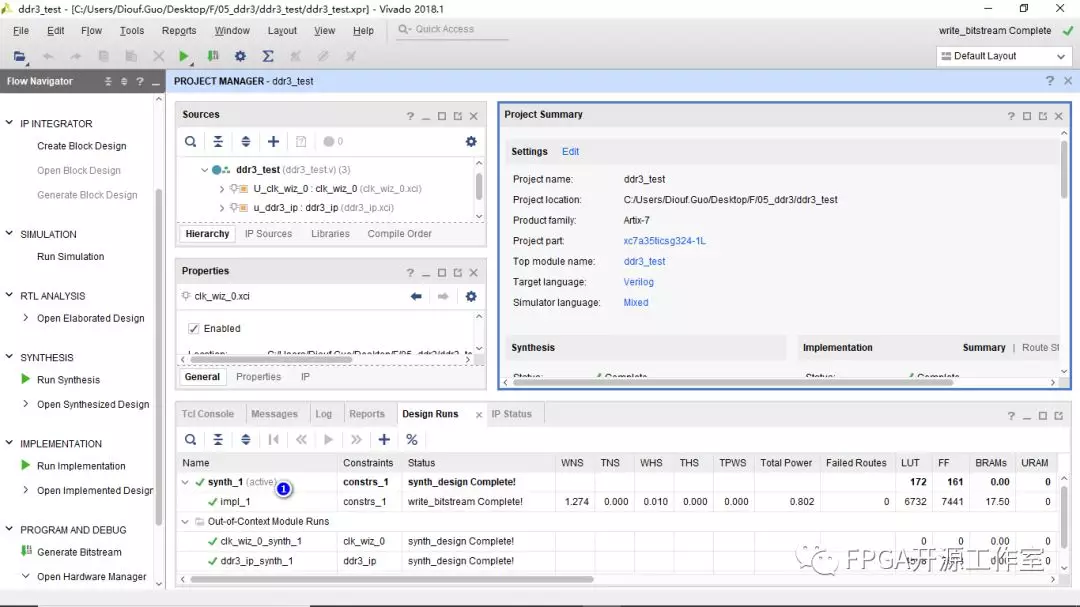

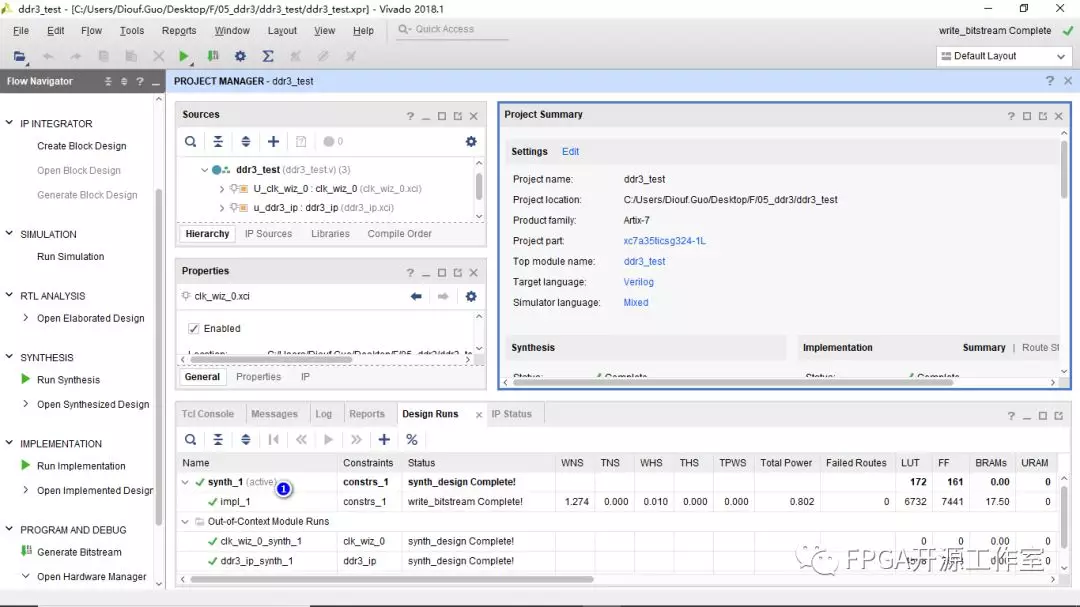

開發(fā)板完成。 軟件使用Vivado 2018.1。 參考工程:ddr3_test。 第五篇:mig讀寫時序下板實現(xiàn) 1頂層文件和約束文件 ddr3_test.v 參見參考工程:ddr3_test

2020-12-15 16:45:16 2476

2476

講解xilinx FPGA 使用mig IP對DDR3的讀寫控制,旨在讓大家更快的學習和應用DDR3。 本實驗和工程基于Digilent的Arty Artix-35T FPGA開發(fā)板完成。 軟件

2020-12-16 15:47:59 1691

1691

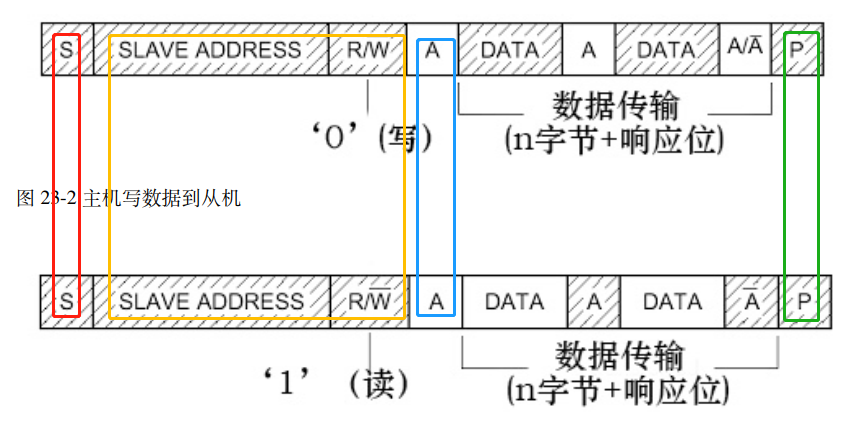

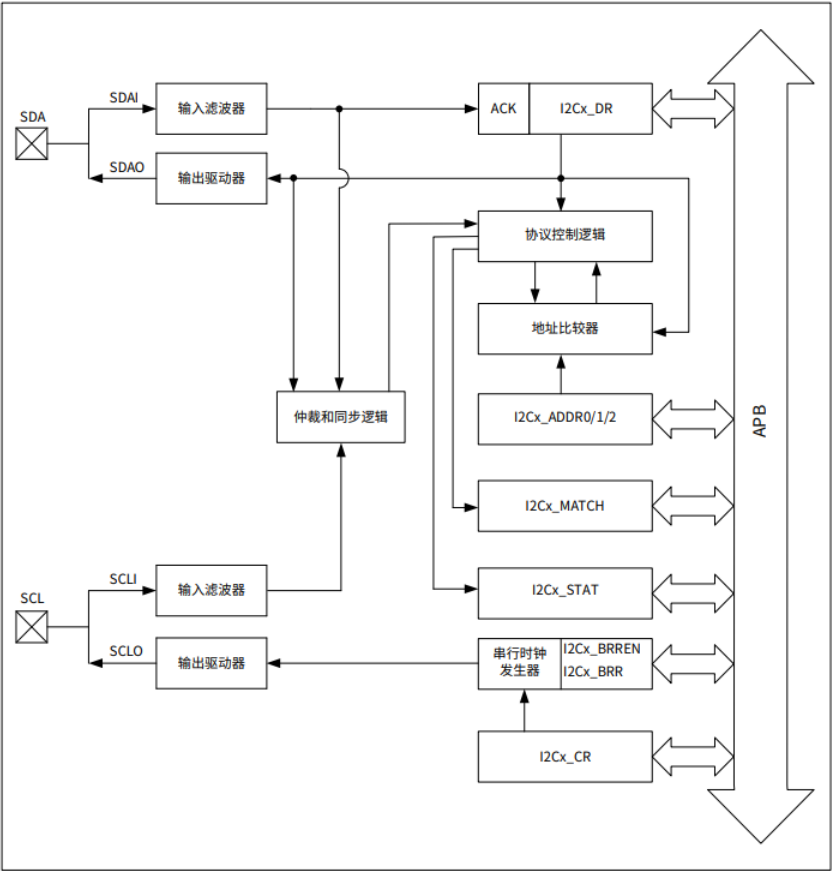

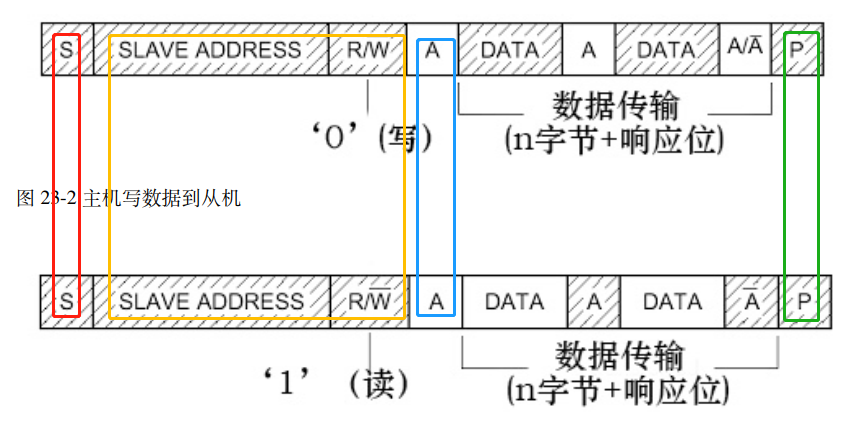

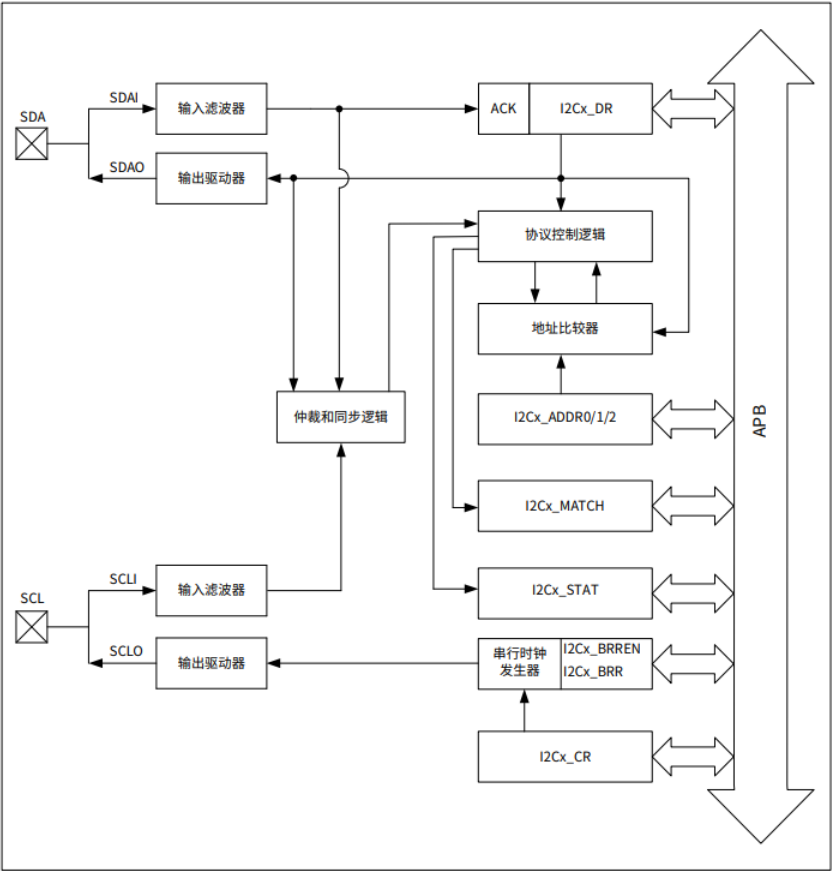

上篇推文對I2C總線的特性進行了介紹和描述。對于開發(fā)者而言,最重要的是編碼I2C的讀寫時序驅動。本篇推文主要總結和分享I2C總線主機端通信的編程實現(xiàn)思路,并不對應特定MCU的硬件I2C外設,此處需要加以區(qū)分。

2023-10-01 16:54:00 328

328

WebAssembly (Wasm) 正在成為一個廣受歡迎的編譯目標,幫助開發(fā)者構建可遷移平臺的應用。最近 Greptime 和 WasmEdge 協(xié)作,支持了在 WasmEdge 平臺上的 Wasm 應用通過 MySQL 協(xié)議讀寫 GreptimeDB 中的時序數(shù)據。

2023-12-22 11:03:26 425

425 在win8.1 pc上使用Vivado 2014.1,MIG IP生成器在啟動時收到Windows錯誤。相同的安裝文件已加載到win7 pc上,MIG IP生成器運行正常。在Win8.1機器上,我

2018-12-07 11:18:46

求助大神!!!FPGA對于DDR3讀寫,F(xiàn)PGA是virtex6系列配置MIG IP 核時,需要管腳分配1.原理圖上dm是直接接地,管腳分配那里該怎么辦2.系統(tǒng)時鐘之類的管腳分配,是需要在原理圖上找FPGA與DDR3之間的連線嗎?還是?

2018-03-16 18:45:10

最近阿威也在玩MIG ,然后對我問了一大堆問題,主要針對MIG的時鐘。后來發(fā)現(xiàn)自己理解得還是不夠。這么一討論更加清晰了,做個筆記吧。第一個時鐘,也就是MIG 對DDR接口的時鐘。因為我用的是ddr3

2019-05-21 07:21:10

請教各位大神,小弟剛學FPGA,現(xiàn)在在用spartan-3E的板子,想用上面的DDR SDRAM進行簡單的讀寫,用MIG生成DDR核之后出現(xiàn)了很多引腳,看了一些資料也不是很清楚,不知道怎么使用生成的這個IP核控制器來進行讀寫,希望大神們稍作指點

2013-06-20 20:43:56

DS1302數(shù)據讀寫時序圖

2012-08-05 21:34:50

LCM1602是什么?由哪些部分組成的?DS1602液晶顯示的讀寫時序有何作用呢?

2022-01-26 06:13:13

DS2411的讀寫時序和DS18B20一致,畢竟同一個公司出的。下面是代碼源文件 ds2411.c#include "ds2411.h"#include "

2022-01-17 07:04:16

大佬們,求助一下。下面兩張圖是正常的讀寫時序和非正常讀寫時序。非正常讀寫時序中,發(fā)現(xiàn)數(shù)據保持長度比較短,而且AED在無效時應該為高阻態(tài),有問題的那塊板子,在無效時,AED為0

2019-12-24 15:42:02

文章目錄EEPROM介紹EEPROM 單字節(jié)讀寫操作時序EEPROM 寫數(shù)據流程EEPROM 讀數(shù)據流程EEPROM介紹在實際的應用中,保存在單片機 RAM 中的數(shù)據,掉電后就丟失了,保存在單片機

2022-01-26 06:43:52

文章目錄EEPROM 多字節(jié)讀寫操作時序EEPROM 多字節(jié)讀寫操作時序我們讀取 EEPROM 的時候很簡單,EEPROM 根據我們所送的時序,直接就把數(shù)據送出來了,但是寫 EEPROM 卻沒有

2021-11-24 07:01:10

I2C讀寫時序I2CI2C寫時序I2C讀時序I2CI2C 總線上的每一個設備都可以作為主設備或者從設備,而且每一個設備都會對應一個唯一的地址(可以從 I2C 器件數(shù)據手冊得知),主從設備之間就是通過

2022-01-18 07:30:22

目錄OLED顯示實驗(8080接口方式)OLED接口說明讀寫流程簡述SSD1306 的 8080 并口讀寫時序解析OLED顯存的排列OLED基本操作流程OLED庫函數(shù)使用說明OLED庫函數(shù)使用示例

2021-12-03 06:07:01

看了芯片使用手冊,沒有看到,對其讀寫時序很模糊,求高手指導,謝謝

2012-07-10 22:10:27

?目錄0 引言1 SDIO接口1.1 SDIO接口有什么用?1.2 SDIO的功能框圖1.3 SDIO的命令與響應1.4 SDIO數(shù)據塊讀寫時序1.5 SDIO常用寄存器1.6 SD卡初始化流程

2022-02-21 06:58:01

SLE4442卡的讀寫時序,也是下降沿讀,上升沿寫嗎???求大神解惑!!!

2013-12-12 17:04:09

STM32 Cubemax(十三) ——SPI時序讀寫RFID-RC522目錄STM32 Cubemax(十三) ——SPI時序讀寫RFID-RC522前言一、SPI時序通信二、模塊接線三

2022-02-08 06:13:14

利用FTDI公司的FT232AM完成RS232和USB之間的接口轉換,然后再對USB接口實現(xiàn)間接的數(shù)據讀寫。

2021-04-26 06:41:48

X76F101MIG-3.0 - Secure SerialFlash - IC MICROSYSTEMS

2022-11-04 17:22:44

XILINX MIG(DDR3) IP的AXI接口與APP接口的區(qū)別以及優(yōu)缺點對比

2021-11-24 21:47:04

接口對于SRAM的讀操作時序,其波形如圖所示。對于SRAM的寫操作時序,其波形如圖所示。具體操作是這樣的,要寫數(shù)據時,(這里是相對于用FPGA操作SRAM而言的,軟件讀寫可能有時間順序的問題需要

2015-12-16 12:46:04

spi讀寫時序里,圖中圓圈處MISO和MOSI為什么不一樣代表什么時序

2017-04-09 20:29:25

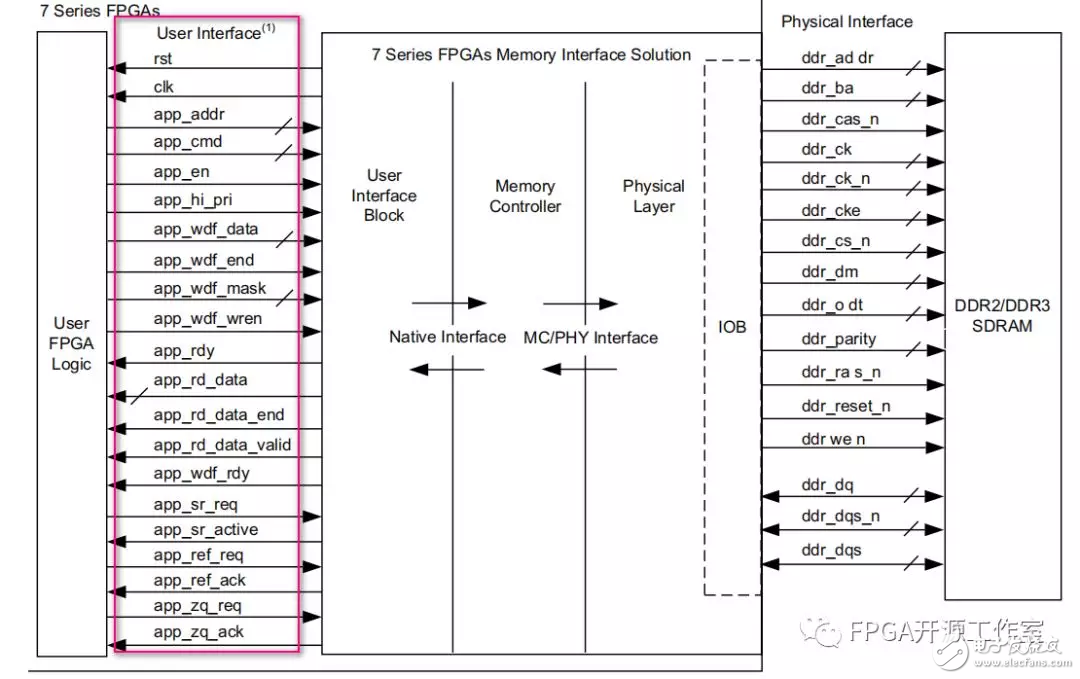

在DDR2 MIG的使用時,想把DDR2封裝成一個FIFO使用,但是有些問題不是太明白。在MIG的User Interface接口中,提供給控制器的數(shù)據是上升沿和下降沿的拼接,一個周期提供兩個數(shù)據到

2015-03-29 18:41:43

DDRSDRAM控制。首先在vivado中進入MIG參數(shù)設置界面因為不需要掛載到microblaze或者arm core上,取消勾選AXI4接口選擇當前使用的FPGA

2016-12-16 10:21:49

你好我在使用MIG CORE讀取LPDDR內存時遇到問題。我已經成功發(fā)送CMD命令,并且空信號已經返回,但是,我沒有成功發(fā)送讀命令,空信號沒有切換到“0”...在atchment,我已經發(fā)布了數(shù)字

2019-07-23 14:46:25

里的例子,ddr正常。但實際是要使用user design文件夾下的.v文件,此時如果編寫頂層讀寫控制程序對mig-39-2.v進行例化,應如何操作才能使用sim_tb_top.v仿真文件,(直接編寫一個

2018-06-22 17:14:40

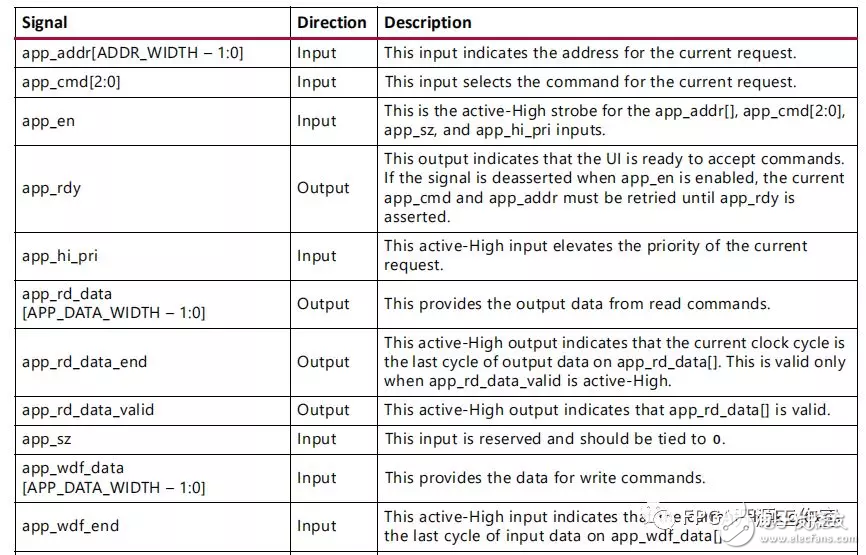

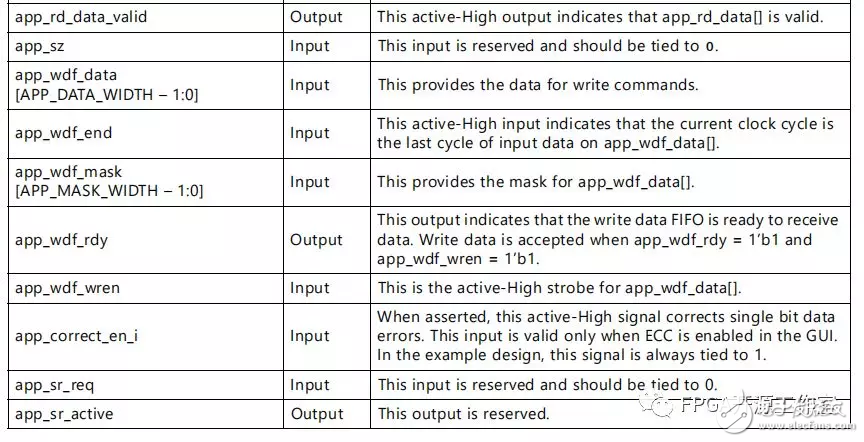

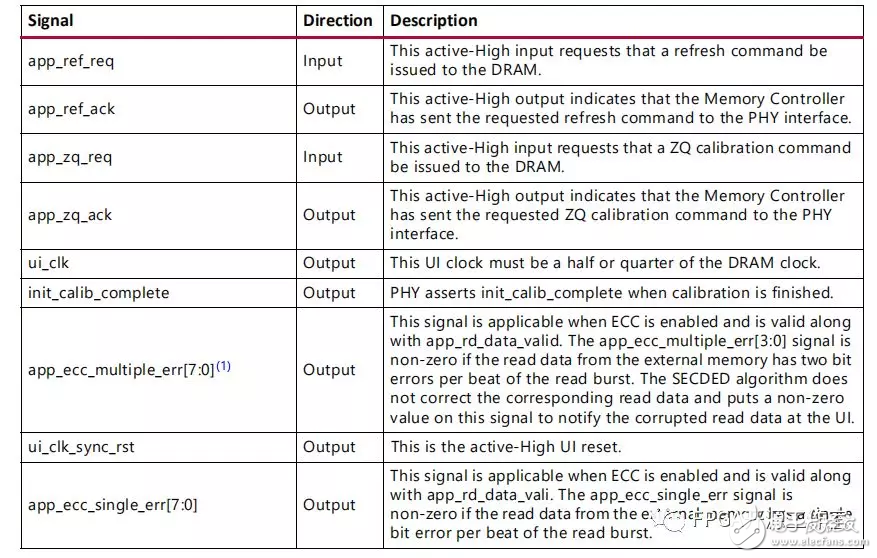

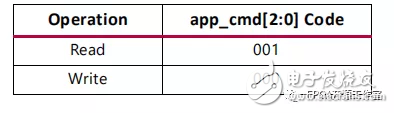

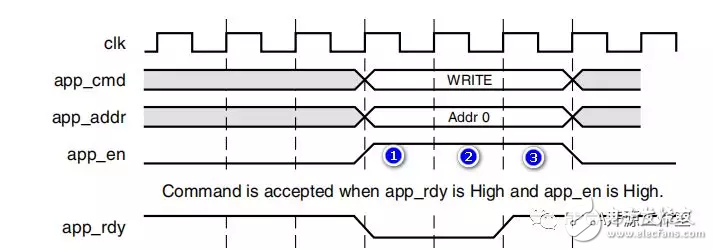

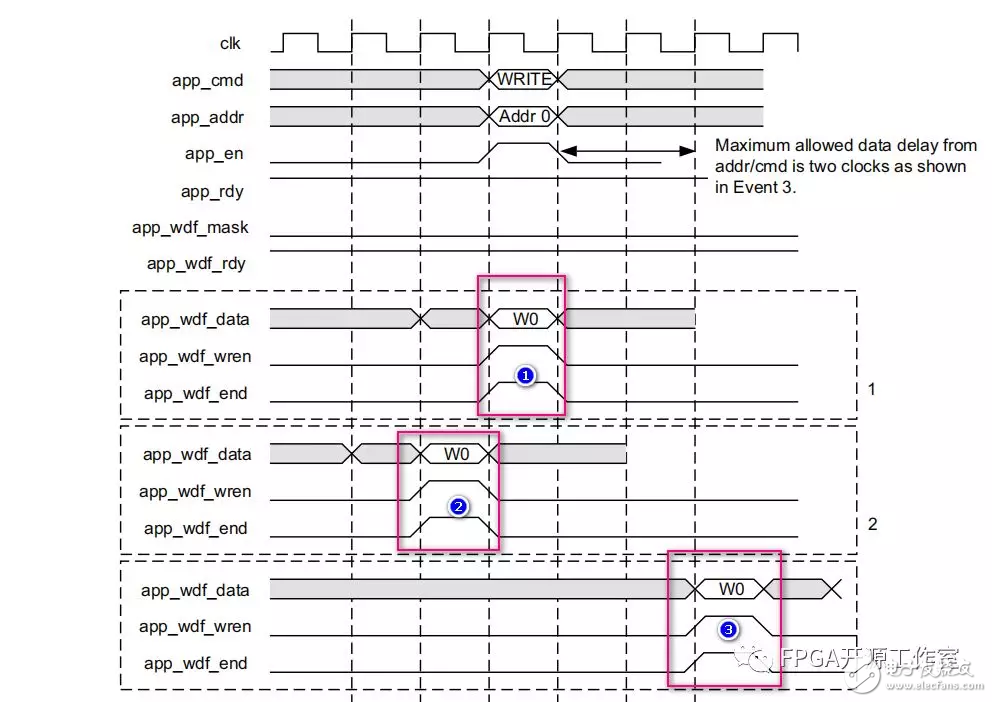

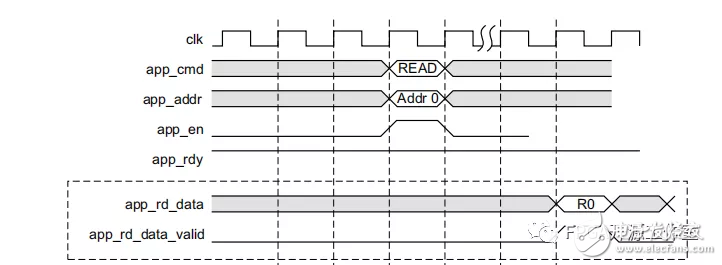

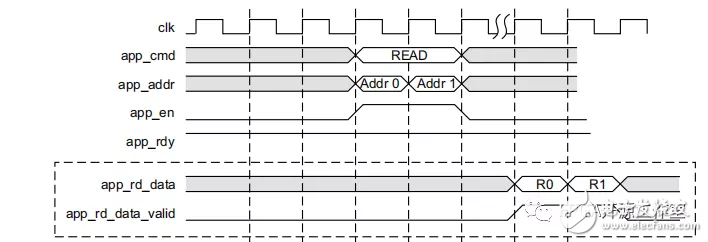

`例說FPGA連載42:DDR控制器集成與讀寫測試之DDR2 IP核接口時序特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 用戶邏輯

2016-11-03 17:43:53

項目中希望使用FPGA 對 DSP 進行HPI BOOT,(DSP 型號為c6748),所以使用了HPI接口,在調試過程中遇到了讀寫內部地址空間異常的情況。由于DSP上電順序為 核心 –>

2018-08-02 07:05:58

本帖最后由 elecfans跑堂 于 2015-9-14 09:21 編輯

最近在做FPGA板子用了兩片16位的FPGA,在MIG中發(fā)現(xiàn)ODT 和CK CS等信號需要分別連接到FPGA。如下圖,是我在MIG中設置的問題嗎?還是xilinx DDR2 MIG就要求這么做?

2015-09-13 14:21:32

我可以使用mig生成ddr控制器(xc6vlx130t)嗎?mig向導只支持ddr2和ddr3!

2020-06-12 07:32:48

鳥人我找不到TFT讀寫命令時序的說明, 目前只有在程序里看的求貼士。。。。

2020-08-06 06:09:37

摘要:RS 232接口是現(xiàn)在最常用的一種通信接口。隨著FPGA技術的高速發(fā)展,一些常見的接口電路的時序電路可以通過FPGA實現(xiàn),通過這種設計可減少電路系統(tǒng)元件的數(shù)量,提高系統(tǒng)集成度和可靠性。詳細闡述

2019-06-19 07:42:37

完成后續(xù)操作。三、MIG時序要求 Xilinx MIG v3.7 IP核的一般寫命令操作時序[7]如下圖所示:圖3 MIG用戶接口的時序要求(突發(fā)長度為8)由以上時序圖可以得到連續(xù)寫命令的控制要點:1

2018-08-30 09:59:01

摘要:介紹SDRAM的主要控制信號和基本命令時序,提出一種應用于解復用的支持多路讀寫的SDRAM接口設計,為需要大容量存儲器的電路設計提供了新思路。關鍵詞:SDRAM 解復用 接口 存儲器

2018-12-03 15:20:48

處理,拿走我需要的東西,拋棄什么不是。比我想在sdram緩沖這個。一旦第一個數(shù)據包被緩沖,下一個數(shù)據包就會進入,并且應該發(fā)送之前的數(shù)據包。這可能嗎?或者只能在當時讀寫。任何人都可以指出一些材料來學習

2020-08-04 10:51:22

nRF24L01+ 2.4GHz無線收發(fā)器的主要特性有哪些?如何使用SPI?如何對SPI的操作時序進行讀寫呢?

2021-12-20 06:32:33

SPI協(xié)議是什么?如何去實現(xiàn)SPI時序協(xié)議的基本讀寫呢?

2021-12-20 06:43:04

1 頁花費的時間相差4倍;1.AISgenD800K008軟件的具體配置如下:想知道,其中,哪些設置是有關nand emifa接口時鐘,時序設置的?2.手冊中EMIFA 時鐘的描述,請問如何在

2019-09-25 07:02:19

親愛的先生Vivado:v2016.4裝置:Artix-7我嘗試在Vivado中使用MIG設計DDR3 SODIMM接口。但是,MIG只生成一對ddr_ck。我認為DDR3 SODIMM需要2對ddr_ck,如ddr_ck0和ddr_ck1。我該如何生成2對ddr_ck?謝謝。

2020-08-24 06:45:17

你好我正在使用atlys主板,我必須在spartan-6上實現(xiàn)ddr2(MT47H64M16-25E)接口,...通過使用MIG及其示例設計,在模擬中一切正常....通過注意ddr2接口,例如

2019-10-28 07:46:43

各位前輩,我們的labview如何才能對isa接口進行操作呢?互連接口中的。i/0讀寫可以嗎?請前輩指條明路。。感激不盡

2012-11-09 14:18:25

我有一段時間讓惡意生成的內容工作。我是一個超級菜鳥,所以我認為這對我來說是一個非常普遍的過程,但我需要一只手學習如何克服困難。我想我來自編程,我希望MIG能夠生成應該自己編譯的庫。但是,我發(fā)現(xiàn)事實

2019-08-06 07:54:35

存儲器接口生成器(MIG)解決方案---Virtex-4 存儲器接口和Virtex-II Pro存儲器解決方案 Virtex-4? FPGAs solve

2009-10-24 12:02:14

LCD顯示模塊的外部接口一般采用并行方式,并行接口接口線的讀寫時序常見以下兩種模式: (1)8080模式。 這類模式通常有下列接口信號:Vcc(工作主電源)Vss(公共端)Vee(偏置負電

2022-02-09 07:34:38

STM32F103的FSMC硬件有哪些呢?怎樣以代碼形式去說明LCD的讀寫時序呢?

2021-10-29 06:26:30

所以我在Vivado 2013.4中有一個使用MIG 7 IP模塊的設計,它之前完成了合成和實現(xiàn)。我收到一條消息說合成和實現(xiàn)已經過時并決定再次運行它,據我所知,在此之前我沒有改變項目中的任何內容

2020-04-06 15:47:46

篇有關SDRAM接口讀寫時序的文章,希望能夠幫助不了解的同學對SDRAM數(shù)據讀寫有更進一步的認識。 一、SDRAM初始化在SDRAM內部有一個邏輯控制單元,并且有一個模式寄存器為其提供控制參數(shù)。每次

2020-01-04 19:20:52

分時鐘和復位信號由片外提供,參考時鐘200MHz。連接圖如下:validate沒問題,編譯下來也沒問題,MIG還分配了地址,但是DDR無法正常讀寫。生成bit文件后打開SDK用了自帶的測試例子

2018-04-24 18:44:45

你好,先生,當我使用mig 7核心時,我遇到了這些錯誤(合成傳遞),[放置30-69]實例U_mig_7series_0 / u_mig_7series_0_mig

2020-08-24 09:15:36

軟件模擬SPI時序實現(xiàn)25Q64讀寫操作單片機采用SPI/IIC通訊協(xié)議訪問外圍電子模塊如:顯示屏、EEPROM、FLASH、各種電子傳感器等等越來越多,掌握SPI/IIC通訊協(xié)議訪問外設非常必要

2021-11-30 07:35:18

軟件模擬SPI時序實現(xiàn)25Q64讀寫操作單片機采用SPI/IIC通訊協(xié)議訪問外圍電子模塊如:顯示屏、EEPROM、FLASH、各種電子傳感器等等越來越多,掌握SPI/IIC通訊協(xié)議訪問外設非常有必要

2022-02-17 06:07:26

時序的,本文采用的是模擬時序,下篇文章就介紹配置STM32的IIC硬件時序讀寫AT24C02和AT24C08。模擬時序更加方便移植到其他單片機,通用性更高,不分MCU;硬件時序效率更高,單每個MCU配置方法不同,依賴硬件本身支持。目前器件: 采用AT24C02 EEPROM存儲芯...

2021-12-08 06:27:13

頻率30kHz"54kHz,垂直掃描頻率50Hz"120Hz,帶寬75MHz。基于DSPBuilder的VGA接口設計方法本設計需要完成的功能包括產生VGA時序以及基于VGA接口

2019-06-04 05:00:12

時序的,上篇文章已經介紹了采用IIC模擬時序讀寫AT24C02,這篇文章介紹STM32的硬件IIC配置方法,并讀寫AT24C08。文章地址:https://xiaolong.blog.csdn.net/article/details/117586108模擬時序更加方便移植到其他單...

2021-11-30 07:48:38

分析了IDE接口硬盤控制寄存器模型;論述了IDE接口硬盤的讀寫幾項技術;給出了設計硬盤克隆軟件的思想和方法,方法針對硬盤物理扇區(qū)進行讀寫,與硬盤上安裝的具體操作系統(tǒng)

2009-02-22 23:47:29 76

76 51 系列單片機慢速讀寫的時序擴展

2009-05-15 14:28:16 18

18 SPI接口讀寫串行EEPROM:93C46為采用3線串行同步總線SPI接口方式的EEPROM,其芯片引腳名稱和功能描述如圖1-1:

2009-09-19 11:39:27 89

89 SRAM的簡單的讀寫操作教程

SRAM的讀寫時序比較簡單,作為異步時序設備,SRAM對于時鐘同步的要求不高,可以在低速下運行,下面就介紹SRAM的一次讀寫操作,在

2010-02-08 16:52:39 140

140 多路讀寫SDRAM接口設計

存儲器是容量數(shù)據處理電路的重要組成部分。隨著數(shù)據處理技術的進一步發(fā)展,對于存儲器的容量和性能提出了越來越高的要求。同步動態(tài)隨機

2009-12-04 11:10:47 698

698

USB接口的彩電存儲器讀寫器讀寫軟件

2011-03-19 11:00:11 1613

1613 SCCB的總線時序與I2C基本相同,它的響應信號ACK被稱為一個傳輸單元的第9位,分為Dont care和NA。Dont care位由從機產生;NA位由主機產生,由于SCCB不支持多字節(jié)的讀寫,NA位必須為高電平。另

2011-03-26 16:00:50 168

168 介紹如何利用EM Microelect ronic 公司的射頻卡讀寫基站芯片EM4094 和Arasan 公司的SDIO 接口芯片AC2200 來構建一種基于通用接口SDIO 的即插即用型的RFID 讀寫器,它可以在支持SDIO 接口的掌上電腦

2011-06-02 15:29:54 58

58 本內容詳細介紹了IC卡讀寫器接口函數(shù)規(guī)范,歡迎大家下載學習

2011-07-26 16:33:16 137

137 一、硬件說明 : 硬件接口圖如下所示: 接口及指示燈說明: 配件為:串口線一根,USB 接口線一根 二、硬件安裝 : 1、使用串口線連接讀寫器的RS232 串口接口和 PC 機的串口; 2、使用

2012-07-05 10:30:38 3332

3332 為適應RFID 讀寫器在不同應用系統(tǒng)中的要求,開發(fā)了一種以MSP430F149 單片機為核心的具有嵌入式以太網網絡接口的手持式RFID 讀寫器。

2012-10-23 16:03:05 3900

3900

經典款逆變氣保焊MIG250一體機整機接線圖。

2016-03-17 10:42:25 6

6 單片機擴展外部ROM或RAM讀寫時序,PPT介紹。

2016-12-12 21:36:19 9

9 根據 M SP430F 149 單片機和 SE D 1335 液晶控制器的性能特點,設計了基于 M SP430F149 單片機的手持式RFID 讀寫器的液晶顯示接口。并論述了 LCD 接口的硬件設計方法和軟件設計方法,給出了相應的硬件接口電路和按照顯示控制時序設計的控制程序流程圖。

2018-04-20 08:51:17 7

7 了解如何使用Vivado存儲器接口生成器(MIG)創(chuàng)建UltraScale存儲器接口設計。

本視頻將向您展示如何為UltraScale器件配置MIG IP內核,包括MIG IP I / O的I / O Bank規(guī)劃。

2018-11-22 07:13:00 2633

2633 DDR對于做項目來說,是必不可少的。一般用于數(shù)據緩存和平滑帶寬。今天介紹下Xilinx DDR控制器MIG IP核的例化及仿真。 FPGA芯片:XC7K325T(KC705) 開發(fā)工具:Vivado

2020-11-26 15:02:11 7386

7386

1. 文章研究主要問題雙弧脈沖 MIG 焊是一種低能量輸入焊接方法, 其原有的雙電源供電系統(tǒng)結構復雜、協(xié)同控制困難、易受干擾。2. 結論提出了雙弧脈沖 MIG 焊一體化專用電源的設計方案

2021-11-08 20:51:02 11

11 文章目錄EEPROM 多字節(jié)讀寫操作時序EEPROM 多字節(jié)讀寫操作時序我們讀取 EEPROM 的時候很簡單,EEPROM 根據我們所送的時序,直接就把數(shù)據送出來了,但是寫 EEPROM 卻沒有

2021-11-16 14:21:05 8

8 軟件模擬SPI時序實現(xiàn)25Q64讀寫操作單片機采用SPI/IIC通訊協(xié)議訪問外圍電子模塊如:顯示屏、EEPROM、FLASH、各種電子傳感器等等越來越多,掌握SPI/IIC通訊協(xié)議訪問外設非常有必要

2021-11-20 12:06:02 6

6 STM32入門開發(fā): 采用IIC硬件時序讀寫AT24C08(EEPROM)

2021-11-21 13:51:04 45

45 STM32 Cubemax(十三) ——SPI時序讀寫RFID-RC522目錄STM32 Cubemax(十三) ——SPI時序讀寫RFID-RC522前言一、SPI時序通信二、模塊接線

2021-12-04 20:36:09 51

51 軟件模擬SPI時序實現(xiàn)25Q64讀寫操作單片機采用SPI/IIC通訊協(xié)議訪問外圍電子模塊如:顯示屏、EEPROM、FLASH、各種電子傳感器等等越來越多,掌握SPI/IIC通訊協(xié)議訪問外設非常有必要

2021-12-22 19:14:54 15

15 基于vivado2020.1和zcu102開發(fā)板(rev1.1)開發(fā)項目,工程涉及DDR4(MIG)和PL端多個讀寫接口交互的問題,通過AXI interconnect進行互聯(lián)和仲裁(采用默認配置)。一個完整控制周期內(約100ms),各端口讀寫情況如下(AWSIZE均為4)。

2022-06-15 11:59:17 1630

1630 本文介紹了在低功耗系統(tǒng)中降低功耗同時保持測量和監(jiān)控應用所需的精度的時序因素和解決方案。它解釋了當所選ADC是逐次逼近寄存器(SAR)ADC時影響時序的因素。對于Σ-Δ(∑-Δ)架構,時序考慮因素有所不同(請參閱本系列文章的第1部分)。本文探討了模擬前端時序、ADC時序和數(shù)字接口時序中的信號鏈考慮因素。

2022-12-13 11:20:18 1056

1056

通信接口對于信息和產品的對接顯得尤為重要,RFID讀寫器的接口類型主要分為有限和無線兩大類。有線接口一般有多種通訊接口,如串口、網口或其他通信接口,無線接口主要是跟WIFI、藍牙等進行連接。讀寫

2022-10-28 18:09:07 929

929

本文開源一個FPGA項目:基于AXI總線的DDR3讀寫。之前的一篇文章介紹了DDR3簡單用戶接口的讀寫方式:《DDR3讀寫測試》,如果在某些項目中,我們需要把DDR掛載到AXI總線上,那就要通過MIG IP核提供的AXI接口來讀寫DDR。

2023-09-01 16:20:37 1896

1896

本文介紹一個FPGA開源項目:DDR3讀寫。該工程基于MIG控制器IP核對FPGA DDR3實現(xiàn)讀寫操作。

2023-09-01 16:23:19 743

743

CW32單片機I2C接口讀寫EEPROM芯片介紹

2023-11-09 17:42:12 499

499

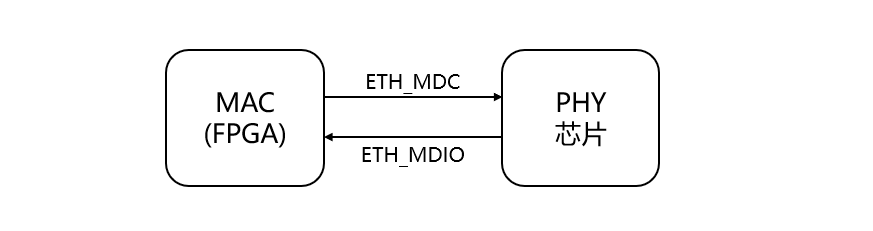

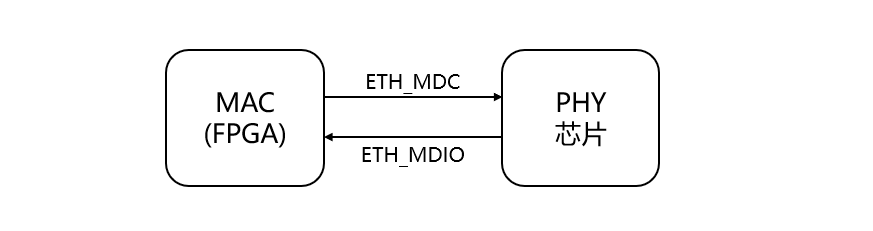

本文開源一個FPGA項目:MDIO接口讀寫測試。以太網通信模塊主要由 MAC (Media Access Control)控制器和物理層接口 PHY (Physical Layer)兩部分構成。其中

2023-10-01 09:46:00 983

983

電子發(fā)燒友網站提供《如何擴展USB接口進行對U盤的讀寫.doc》資料免費下載

2023-10-25 10:15:18 0

0 基于vivado2020.1和zcu102開發(fā)板(rev1.1)開發(fā)項目,工程涉及DDR4(MIG)和PL端多個讀寫接口交互的問題,通過AXI interconnect進行互聯(lián)和仲裁(采用默認配置)。

2023-12-01 09:04:23 363

363

電子發(fā)燒友App

電子發(fā)燒友App

評論