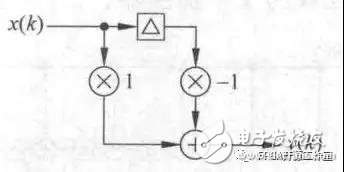

作者:lee 在實現多級CIC濾波器前我們先來了解滑動平均濾波器、微分器、積分器以及梳狀濾波器原理。CIC濾波器在通信信號處理中有著重要的應用。 這篇文章來介紹梳狀濾波器以及積分梳狀濾波器,為up

2020-11-21 09:57:00 5220

5220

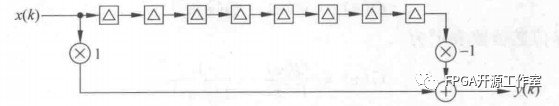

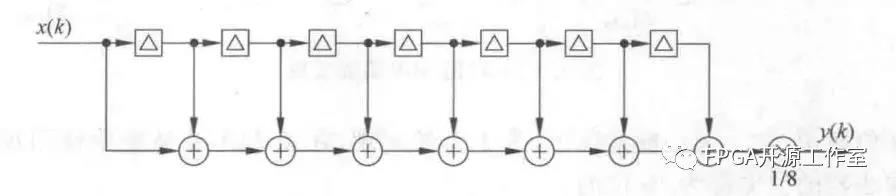

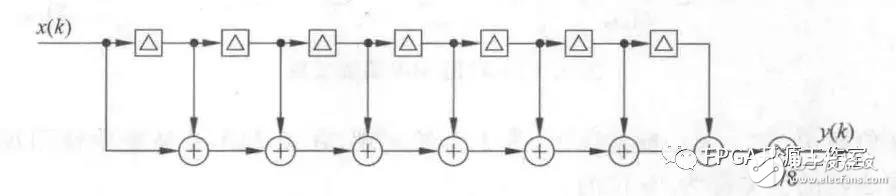

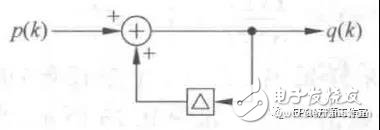

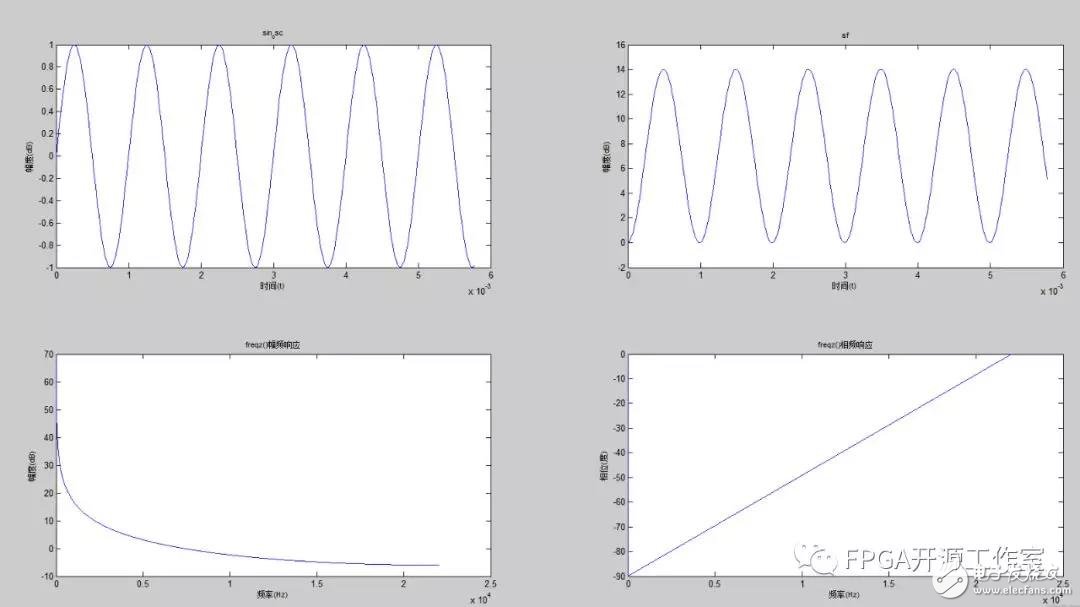

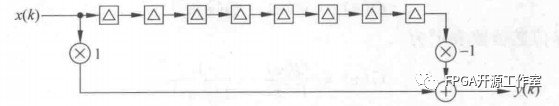

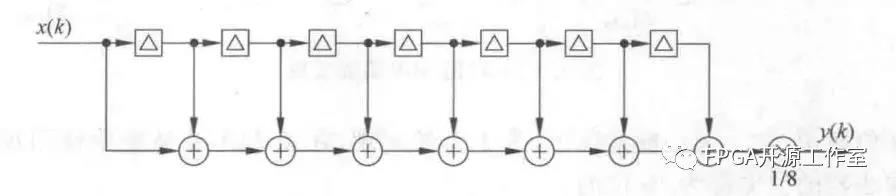

在實現多級CIC濾波器前我們先來了解滑動平均濾波器、微分器、積分器以及梳狀濾波器原理。CIC濾波器在通信信號處理中有著重要的應用。 1、滑動平均濾波器 圖1 8權值滑動平均濾波器結構 滑動平均濾波器

2020-12-03 11:55:06 5078

5078

作者: OpenSLee 1 概述 在數字信號處理中,CIC濾波器是FIR濾波器中最優的一種,其使用了積分,梳狀濾波器級聯的方式。 CIC濾波器由一對或多對積分-梳狀濾波器組成,在抽取CIC中,輸入

2020-12-05 10:21:00 2654

2654 在本文中,我們將簡要介紹不同類型的濾波器,然后學習如何實現移動平均濾波器并使用CIC架構對其進行優化。

2023-10-02 15:38:00 943

943

整數倍內插是先在已知抽樣序列的相鄰兩個抽樣點之間等間隔地插入(I-1)個零值點,然后進行低通濾波器,即可求得I倍內插的結果。

2020-11-20 09:55:22 6196

6196 文章主要講CIC理論基礎,下個文章講FPGA實現。級聯積分梳狀濾波器又稱CIC。這是多速率信號處理中一種結構簡單的濾波器,只需要加法器和寄存器即可實現,可以靈活的設置抽取因子和插值因子,并且CIC是一

2021-08-17 08:27:40

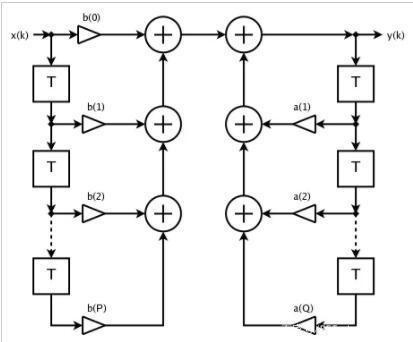

fpga實現濾波器fpga實現濾波器在利用FPGA實現數字信號處理方面,分布式算法發揮著關鍵作用,與傳統的乘加結構相比,具有并行處理的高效性特點。本文研究了一種16階FIR濾波器的FPGA設計方法

2012-08-12 11:50:16

。本文研究了一種16階FIR濾波器的FPGA設計方法,采用Verilog HDI語言描述設計文件,在Xilinx ISE 7.1i及ModelSim SE 6.1b平臺上進行了實驗仿真及時序分析,并探討了實際工程中硬件資源利用率及運算速度等問題。

2012-08-11 18:27:41

最近在做一個FPGA的課程設計,遇到一個比較煩人的問題,希望大神們可以指點迷律。一個16階的FIR濾波器,采用分布式算法實現的,采樣率1M,fc=100K,頻率到了30K以上時就會出現那些尖刺,很

2018-02-25 19:25:50

對CIC抽取濾波器的結構進行分解,得出一個能實現任意抽取因子的改進的CIC抽取濾波器的實現結構。最后的仿真表明:該設計方法使得CIC抽取濾波器性能得到改善,實現結構高效,在實際工程中有很大的應用價值

2010-06-02 10:07:03

系數分別為N1,N2,…,Ns的較小、較簡單的級聯濾波器。抽取系數滿足以下等式:在考慮各種濾波器的特性基礎上,抽取系統采取多級抽取組分組級聯的方式。為了有效利用FPGA資源,采用16倍CIC濾波器

2009-10-23 10:26:53

PRD1211,5 Vin,200 Vout,2 mA參考設計。本設計使用帶四倍電荷泵的升壓轉換器。它采用創新的4級電荷泵,將升壓級的輸出電壓提高4倍。可以使用許多不滿額定輸出電壓的器件。此外,級聯FET(Q1)用于提高ADP1613的電壓能力

2019-07-17 08:11:56

現在接收的455k左右的收音機信號,經過乘法后,要經過CIC濾波器和FIR濾波器,不知道該怎么設置參數,求解救啊,調了很久一只沒出來!!!!

2013-08-17 11:45:35

hamming窗,通帶截止頻率為3.2KHz.由于采樣率與通帶截止頻率相差太大,無法直接設計出滿足要求的FIR濾波器。于是就采用了積分梳狀濾波器CIC后接FIR濾波器,CIC是為了抽取已達到降低FIR采樣頻率

2013-05-26 19:57:13

抽取濾波器的硬件實現6.5.3 多相插值濾波器的基本理論6.5.4 多相插值濾波器的硬件實現6.6 CIC濾波器6.6.1 CIC濾波器的基本理論6.6.2 CIC濾波器的比特增長問題6.6.3

2012-04-24 09:33:23

低通濾波器,用來限制信號的頻帶,然后再進行抽取,這樣的話我們來算一下低通濾波器的截止頻率就是1/2倍的經抽取后的采樣速率,即fc = 1/2 * (F1/M) ,M是抽取倍數。而1/2*F1對應的數域頻率

2018-11-15 00:27:19

濾波器的階數與內插/抽取的倍數相同時,其結構更利于FPGA實現。比如抽取時,只需要將D個數據組成一組,相加作為一個輸出即可(即同時完成了濾波與抽取)。結合下面的實例理解(設CIC濾波器階數與抽取倍數都為5

2020-09-28 09:36:54

高通濾波器;采用方案2,利用無源LC濾波器技術來實現四階橢圓低通濾波器。 2 系統總體設計方案及實現方框圖本系統以單片機及FPGA為控制核心,由可控增益放大模塊、程控濾波模塊和幅頻特性測試模塊構成

2019-09-29 14:08:52

基于FPGA的四階IIR數字濾波器怎么樣?

2021-04-29 06:21:49

設計一般采用CIC、HB、FIR級聯的形式組成。同時,由于CIC濾波器的通帶性能實在太差,所以中間還要加上一級PFIR濾波器以平滑濾波器的通帶性能。

2019-09-20 06:13:11

本帖最后由 eehome 于 2013-1-5 09:50 編輯

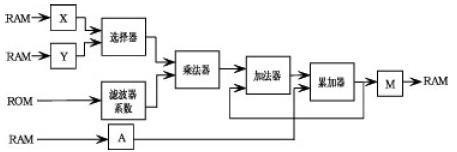

基于FPGA的FIR濾波器設計與實現 文章研究基于FPGA、采用分布式算法實現FIR濾波器的原理和方法,用

2012-08-11 15:32:34

基于FPGA的fir濾波器實現

2017-08-28 19:57:36

本帖最后由 eehome 于 2013-1-5 09:50 編輯

基于fpga的fir濾波器的實現

2012-08-17 16:42:33

成長,CIC低通濾波器得到了廣泛的應用。長期以來,CIC梳狀濾波器一般是在通用DSP處理器上實現的,由于DSP處理器的順序執行特性的限制,其速度很難滿足一些高速抽取與插值系統的需要。FPGA具有優良的全硬件并行執行的特性,研究CIC梳狀濾波器的設計及其FPGA實現具有重要的現實意義。

2019-09-23 07:22:30

濾波器是任何信號處理系統的關鍵組成部分,隨著現代應用的日趨復雜,濾波器設計的復雜程度也日益提高。采用 FPGA 設計和實現的高性能濾波器的能力是模擬方法所望塵莫及的。另外,采用FPGA

2019-09-18 08:28:47

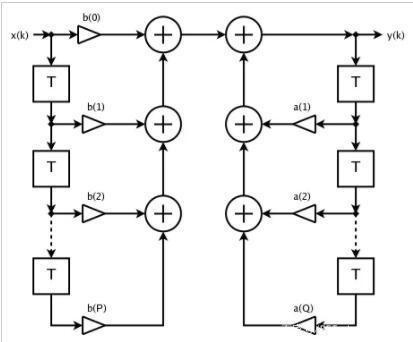

本文介紹了一種采用級聯結構在FPGA上實現IIR數字濾波器的方法。

2021-04-15 06:16:32

本文介紹了一種采用Xilinx公司的XC2V1000實現FIR抽取濾波器的設計方法。

2021-04-29 06:50:18

本文將介紹線路調制的FPGA實現,包括:線路調制單元數字化實現的總體設計,CIC和FIR濾波器的FPGA實現以及載波發生器單元的設計。

2021-04-29 06:41:28

濾波器在FPGA中的實現用FPGA來實現濾波器的設計優點用FPGA來設計濾波器,不但設計簡單,而且成本小,可靠性好。且無需像傳統的設計芯片一樣進行測試。主要優點:設計簡潔。若設計有誤,則只需

2021-07-30 07:03:10

如何用中檔FPGA實現多相濾波器?

2021-04-29 06:30:57

原先的fs就對應6pi,信號帶寬也就變成了2pi。 ??而抽取濾波器則剛好相反,對于3倍的插值濾波器,信號帶寬在數字頻率上,縮小了1/3。也就是原來0pi的區間縮小到0pi/3,因此信號的截止頻率

2020-12-24 16:03:16

ad9777芯片手冊的內插問題,對ad9777的寄存器進行配置,可以實現數據的四倍內插嘛?

2023-12-01 06:03:09

并行流水結構FIR的原理是什么基于并行流水線結構的可重配FIR濾波器的FPGA實現

2021-04-29 06:30:54

目前FIR濾波器的硬件實現的方式有哪幾種?怎么在FPGA上實現FIR濾波器的設計?

2021-05-07 06:03:13

)接收多通道數字數據 - 有16個數據通道通過SPI串行接口進入FPGA。數字數據被過采樣(10kHz采樣率)。每個樣本16位。(2)將多通道數據抽取/下采樣4倍(可能使用CIC濾波器,或CIC

2019-04-17 09:17:26

本文以實現抽取率為2的具有線性相位的3階FIR抽取濾波器為例,介紹了一種用XC2V1000型FPGA實現FIR抽取濾波器的設計方法。

2021-05-07 06:02:47

為什么要設計一種理想濾波器呢?CIC抽取濾波器是由哪些部分組成的?怎樣去設計一種CIC抽取濾波器并對其進行MATLAB仿真呢?

2021-11-19 07:29:44

256KHZ,輸出1bit數字信號,現需要降采樣,抽取因子128,要求最終輸出24bit,擬用三級結構,第一級為5階的抽取率為32的cic濾波器,第二級為抽取率為2的cic補償濾波器,第三極為半帶濾波器

2012-02-26 22:00:16

256KHZ,輸出1bit數字信號,現需要降采樣,抽取因子128,要求最終輸出24bit,擬用三級結構,第一級為5階的抽取率為32的cic濾波器,第二級為抽取率為2的cic補償濾波器,第三極為半帶濾波器,濾波器的截止頻率為1K。硬件實現,望各位大俠指點。wbpotato@163.com qq:446497438.

2012-02-26 15:52:55

分布式的濾波器算法是什么?一種基于FPGA分布式算法的濾波器設計實現

2021-04-29 07:13:23

用FPGA來實現濾波器的設計優點有哪些?

2021-11-05 07:59:53

(FIR,HBF,CIC)進行了簡要介紹,對其實際性能進行了對比分析。最后,采用Matlab與FPGA硬件平臺相結合的設計方法對性能最合適的FIR濾波器進行硬件實現、聯合仿真、測試與驗證,該設計方法

2010-04-22 11:30:26

設計采用ADP1613升壓轉換器和四倍電荷泵。它采用創新的4級電荷泵,將升壓級的輸出電壓提高4倍。可以使用許多不滿額定輸出電壓的器件。此外,級聯FET(Q1)用于提高ADP1613的電壓能力。使我們能夠使用非常便宜的集成FET升壓控制器

2019-07-16 06:35:37

誰有cic插值濾波器的代碼,能分享下嗎,實在不會

2017-04-18 20:01:06

硬件上實現了。四、FIR半帶濾波器的FPGA設計這次我們直接調用FIR濾波器的IP核來設計,非常的方便,我們只需要做一下頂層的理化,考慮一下有限字長的影響,就可以將工作交給IP去做,而且效率比我們自己寫

2015-08-29 15:33:49

適合應用在多速率信號處理的前端,作為抗混疊濾波器來用,或者是作為后端的抗混疊插值濾波器。七、多級 Hogenauer CIC抽取濾波器的FPGA實現 Hogenauer CIC抽取濾波器是一種特殊

2015-08-29 15:25:38

起見,我們自己定義濾波器的通阻帶,采樣頻率以及通阻帶衰減,盡量讓濾波器階數小一點,方便我們后邊的FPGA實現,畢竟這只是個例子,簡單一點比較好,如果真的當做工程設計來做,那就具體情況具體分析了 濾波器

2015-08-29 15:37:11

討論了軟件無線電接收機中數字下變頻處理技術中的CIC抽取濾波器結構原理,分析了CIC濾波器級聯ISOP濾波器進行抽取濾波的設計技術。驗證了ISOP濾波器對CIC濾波器帶內衰減補償的有

2009-05-26 20:44:21 21

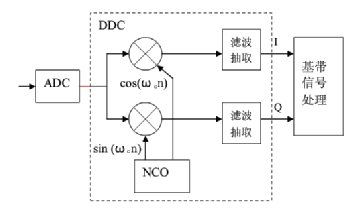

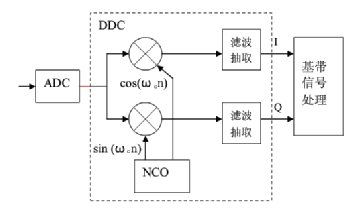

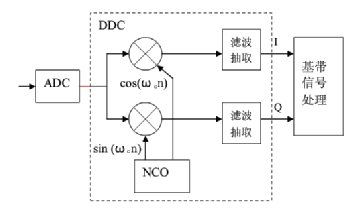

21 探討了DDC中抽取濾波系統的設計方法和基于DSP Builder的具體實現方案,采用CIC濾波器、HB濾波器、FIR濾波器三級級聯的方式來降低采樣率,并進行了模型仿真,結果表明設計是可行的

2009-09-17 11:35:08 23

23 插值和抽取濾波器被廣泛應用于現代通信系統中,然而基于傳統DSP 或者FPGA 的濾波器,具有數據率低和占用資源多的缺點。為了克服這些缺點,本文針對一種多核DSP 處理器, 提出

2009-11-27 15:26:57 9

9 在軟件無線電的下變頻模塊中,級聯梳狀積分濾波器有著重要的應用,其主要作用是信號的抽取與低通濾波。文中總結了級聯梳狀積分抽取濾波器的理論要點,并介紹了采用FPGA

2010-01-06 15:16:45 31

31 數字濾波器在FPGA中的實現

2010-02-09 10:21:27 76

76 設計一個由現場可編程門陣列(FPGA)控制的濾波器。該濾波器主要由3個模塊組成:前置放大、濾波電路、FPGA顯示與控制電路等利用FPGA作為放大器及程控濾波器電路中繼電器組的控制模

2010-07-17 18:00:09 45

45 在研究了低軌衛星DS-CDMA系統數字上變頻器的內插技術之后,提出了以成型濾波器、半帶濾波器和CIC濾波器等多級內插級聯的結構來實現抽樣率的變換.在具體實現上采用了基于多相結

2010-10-15 09:51:18 15

15 IIR數字濾波器設計-在FPGA上實現任意階IIR數字濾波器

摘 要:本文介紹了一種采用級聯結構在FPGA上實現任意階IIR數字濾波器的方法。此

2008-01-16 09:45:39 2276

2276

摘要: 針對在FPGA中實現FIR濾波器的關鍵--乘法運算的高效實現進行了研究,給了了將乘法化為查表的DA算法,并采用這一算法設計了FIR濾波器。通過FPGA仿零點驗證

2009-06-20 14:09:36 677

677

摘 要:為了降低地震數據采集系統的成本和功耗,采用數字信號處理器(DSP)實現-△模數轉換器中的數字抽取濾波器算法。通過采取查表法、倒序循環遍歷法以及模擬循環尋址法等優化方法,以較低工作頻率實現了四通道四級抽取濾波運算,達到了系統設計的要求。

2011-02-25 16:00:23 68

68 CIC濾波器是一種結構簡單、規整,占用存儲量小的濾波器,不需要乘法器,非常適用于高速采樣和插值比很大的場合。本文介紹了一般CIC濾波器的結構,展示了組成CIC濾波器的2個基本單元,以及它們各自的數學本質與Z變換下的意義。介紹了內插器和抽取器這2種CIC濾

2011-03-15 12:21:50 68

68 為補償傳統CIC濾波器的通帶衰減,提出一種改進型的CIC抽取濾波器,即在SCIC濾波器之后級聯一個二階多項式內插濾波器。基于硬件實現的要求,給出改進型CIC濾波器的FPGA高效實現原理圖。仿真結果表明改進的CIC濾波器具有更好的通阻帶特性。

2011-03-15 14:06:35 52

52 本文主要論述了用于音頻系統ADC的過采樣抽取濾波器的設計 系統論述了濾波器的多級實現

2011-04-19 10:21:56 94

94 為了解決高速抽取濾波器系統中傳統CIC濾波器旁瓣抑制不夠的問題,通過對級聯COSINE抽取濾波器和傳統CIC抽取濾波器的原理推導進行對比,分析出級聯COSINE濾波器在幅頻特性上同CIC濾波

2011-05-03 18:11:53 31

31 基于多速率信號處理原理,設計了用于下變頻的CIC抽取濾波器,由于CIC濾波器結構只用到加法器和延遲器,沒有乘法器,很適合用FPGA來實現,所以本文分析了CIC濾波器的原理,性能及影

2011-08-26 15:12:11 160

160 CIC濾波器是常用于多速率采樣抽取或內插過程中的高效濾波器,具有結構簡單,易于工程實現的特點。以提高采樣速率為例,首先介紹了內插理論和CtC濾波器原理,重點給出了CIC濾波器

2011-09-20 15:12:49 73

73 為了較好地解決軟件無線電技術應用中任意采樣率轉換的問題,本文引入了時變CIC濾波器。其對傳統的先內插后抽取的多級CIC結構的中間狀態進行等效變換,避免了在較高頻率下處理信

2011-09-20 15:26:46 57

57 為了產生調制信號的碼元速率能在大范圍內實時可變,采用插值濾波技術 多級積分梳狀濾波器。在分析多級濾波器的結構和特性的基礎上,闡述了一種利用剪除理論實現多級濾波器的高效

2011-12-26 18:33:08 25

25 本文首先對CIC、HB、FIR濾波器的原理及設計作了簡單的說明,最后用Matlab結合System generator對本文所設計的DDC濾波器作了一個仿真。

2012-08-06 15:34:48 10298

10298

文中基于多速率數字信號處理原理,設計了用于數字下變頻技術的CIC抽取濾波器。通過分析CIC濾波器的原理及性能參數,利用MATLAB設計了符合系統要求的CIC濾波器,并通過FPGA實現了CI

2013-04-15 19:29:28 71

71 條件,設計并實現了基于FPGA的菱形濾波窗口及其功能仿真,并對兩種濾波窗口的硬件結構進行FPGA資源消耗的對比,說明文中設計的菱形濾波器對消除地層噪聲干擾有很強的實用性。

2015-12-31 09:20:25 8

8 matlab與24倍插值CIC濾波器設計,有興趣的同學可以下載學習

2016-04-27 15:51:58 56

56 4階24倍抽取CIC濾波器設計,有興趣的同學可以下載學習

2016-04-27 15:51:58 26

26 基于FPGA的FIR濾波器設計與實現,下來看看

2016-05-10 11:49:02 38

38 研究了一種采用FPGA實現32階FIR濾波器硬件電路方案;討論了窗函數的選擇、濾波器的結構以及系數量化問題;研究了FIR濾波器的FPGA實現,各模塊的設計以及如何優化硬件資源,提高運行

2017-11-10 16:41:57 15

15 ISE 12.3在Xilinx xc5vsx95t-2ff1136 FPGA上實現了一種下采樣率為64的抽取濾波器。Modelsim仿真結果表明,該抽取濾波器設計是有效的,達到了設計指標。

2017-11-17 09:01:55 5303

5303 前端的調制器利用過采樣的方法將量化噪聲搬移到高頻段,后端的數字抽取濾波器必須再將高頻噪聲濾除,所以數字抽取濾波器的性能在整個Σ-? ADC中起著非常重要的作用。我們選用了一種抽取濾波器Sinck數字濾波器,它可以有效的濾除高頻噪聲滿足設計的需要,并且這種濾波器的算法中不需要乘法。

2018-07-18 18:31:00 3664

3664

(降2倍)和半帶濾波器(降2倍)組成。為了實現高頻工作,CIC濾波器采用兩級結構,第一級采用多相分解技術,使大部分結構工作在較低時鐘頻率下,極大地降低了CIC的功耗,第二級采用傳統結構。CIC補償濾波器使信號通帶平坦,半帶濾波器滿足了阻帶的衰減要求。

2018-02-21 12:08:00 1815

1815

文介紹了FIR抽取濾波器的工作原理,重點闡述了用XC2V1000實現FIR抽取濾波器的方法,并給出了仿真波形和設計特點。

2018-04-19 11:34:00 1846

1846

用FPGA實現抽取濾波器比較復雜,主要是因為在FPGA中缺乏實現乘法運算的有效結構,現在,FPGA中集成了硬件乘法器,使FPGA在數字信號處理方面有了長足的進步。本文介紹了一種采用Xilinx公司的XC2V1000實現FIR抽取濾波器的設計方法。

2018-04-28 11:50:00 1072

1072

通帶紋波和阻帶衰減等要求,數字抽取濾波器一般采用CIC濾波器、CIC補償濾波器、半帶濾波器三級級聯方式構成[1]。本文在此結構的基礎上,對CIC濾波器部分進行優化,通過級聯結構和多相分解技術,最終有效地降低了CIC濾波器的功耗,提升了濾波器的運算速度。

2018-06-29 14:32:00 11289

11289

用FPGA實現抽取濾波器比較復雜,主要是因為在FPGA中缺乏實現乘法運算的有效結構,現在,FPGA中集成了硬件乘法器,使FPGA在數字信號處理方面有了長足的進步。本文介紹了一種采用Xilinx公司的XC2V1000實現FIR抽取濾波器的設計方法。

2020-09-25 10:44:00 3

3 針對Σ△ADC輸出端存在的高頻噪聲問題,設計了一種 Sinc數字抽取濾波器,實現了Σ-△調制器輸出信號的高頻濾波。分析了Sinc濾波器的結構原理,基于 Spartan6FPGA進行濾波器的設計與實現

2020-08-26 17:12:00 14

14 WCDMA中規定了小區搜索的時隙同步過程采用匹配濾波器的方法實現,本論文主要研究匹配濾波器原理及FPGA實現結構。

2021-01-26 16:22:43 12

12 基于FPGA的_ADC數字抽取濾波器Sinc_3設計(現代電源技術基礎楊飛)-該文檔為基于FPGA的_ADC數字抽取濾波器Sinc_3設計總結文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-09-16 13:58:04 20

20 積分梳狀濾波器(CIC,Cascaded Integrator Comb),一般用于數字下變頻(DDC)和數字上變頻(DUC)系統。CIC 濾波器結構簡單,沒有乘法器,只有加法器、積分器和寄存器

2023-03-27 11:40:23 886

886

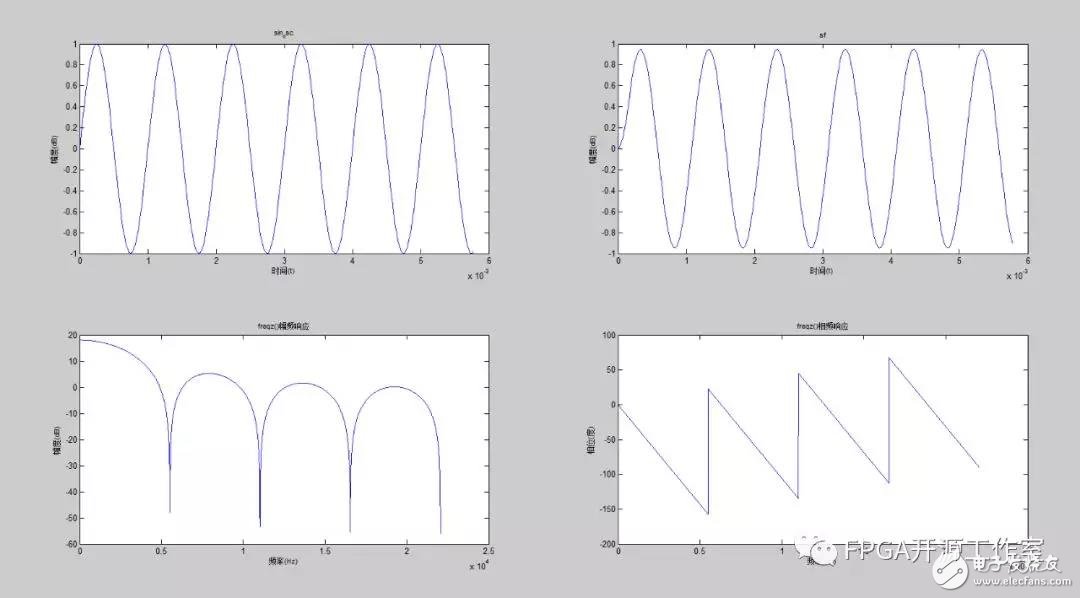

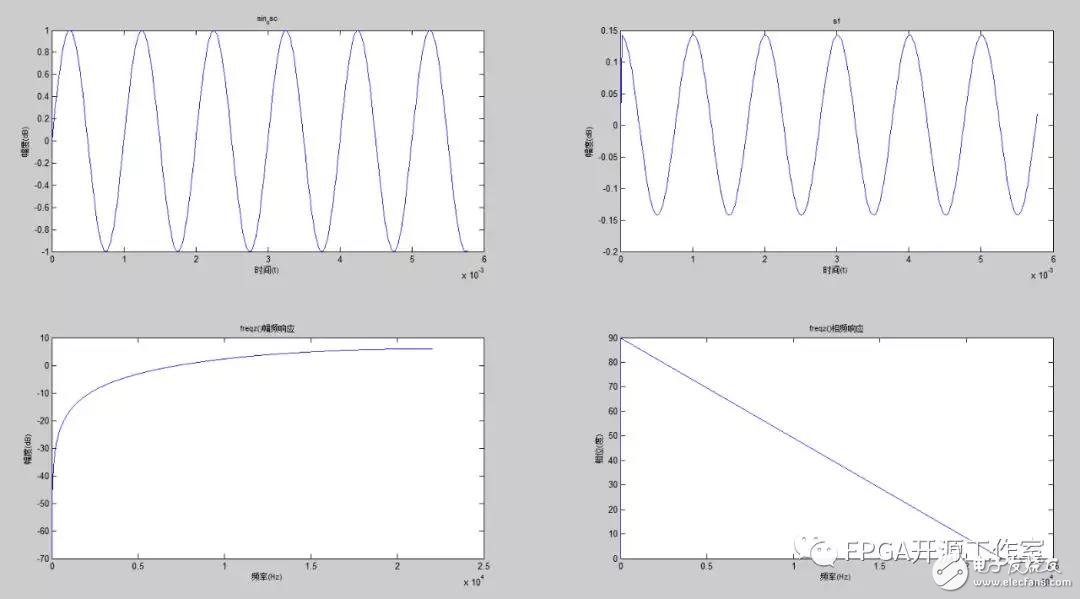

加法器、積分器和寄存器,適合于工作在高采樣率條件下,而且CIC濾波器是一種基于零點相消的FIR濾波器,已經被證明是在高速抽取或插值系統中非常有效的單元。 我們首先產生一個采樣率Fs=0.78125Mhz,頻率Fout=0.078125Mhz的樣本信號,對其進行16倍插值。這就涉及到直接頻率合成器DDS的知識。

2023-04-12 10:26:25 597

597 積分梳狀濾波器(CIC,Cascaded Integrator Comb),一般用于數字下變頻(DDC)和數字上變頻(DUC)系統。

2023-06-01 11:05:41 1166

1166

電子發燒友App

電子發燒友App

評論