靜態(tài)時序分析經(jīng)常會遇到基于鎖存器(latch)的設計從而引入了一個概念稱為“Time Borrowing”。這篇文章向大家解釋了什么是time borrowing,以及鎖存器(latch)設計和時序報告中關于time borrowing的處理方式。

下面的時鐘信號周期為10,占空比為50%:

同時我們引入一個簡單的電路,如下所示:

為了更容易理解,我們假設每個觸發(fā)器的建立時間和保持時間均為“0”。

同樣假設時鐘偏移和時鐘延遲也為“0”。

F1在時刻0得到數(shù)據(jù),F(xiàn)2在時刻10對數(shù)據(jù)進行了采樣。

因此如果數(shù)據(jù)在時刻10之后到達F2,那么F2就不能采集到正確的數(shù)據(jù)。

同理,從F2傳出的數(shù)據(jù)到達F3也需要10個時間單位,在下一個時鐘沿的時候被采樣。

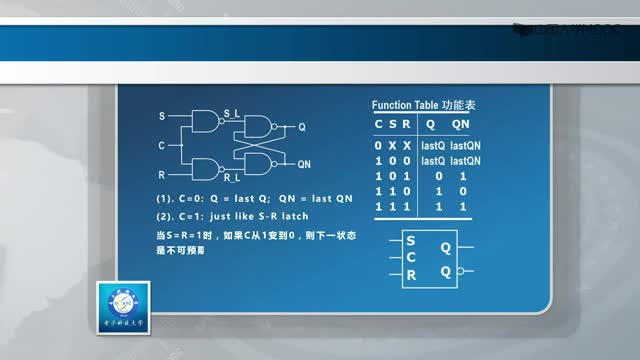

現(xiàn)在我們用一個鎖存器(latch)L2替代F2,鎖存器的Gate也由同樣的時鐘信號驅動:

F1在時刻0發(fā)出數(shù)據(jù):

數(shù)據(jù)會在時刻10之前到達鎖存器的輸入端,數(shù)據(jù)會在鎖存器的D端口等待。

這與F2的效果非常相似。

但是如果數(shù)據(jù)在時刻10之后到達會發(fā)生什么呢?

在時刻10到15之間可以說L2是透明的。

因此即使數(shù)據(jù)在時刻10之后到達L2,L2也能夠處理只要數(shù)據(jù)能夠在時刻15之前到達L2。

這意味著數(shù)據(jù)可以最多用15個時間單位到達鎖存器,而使用觸發(fā)器最多是10個時間單位。

舉個例子,如果數(shù)據(jù)在時刻12到達L2,這意味著與觸發(fā)器相比,鎖存器提供了2個時間單位的優(yōu)勢。

在這個例子中L2最多能提供5個時間單位的優(yōu)勢。

現(xiàn)在讓我們再來看一下L2到F3之間的路徑。

數(shù)據(jù)在時刻12從L2傳出,在時刻20被F3采樣。

那么從L2到F3僅花費了8個時間單位。

在都是由觸發(fā)器組成的電路中,第二段路徑則需要10個時間單位。

這樣看來這個電路少用了2個時間單位。

從本質上來說:

通往鎖存器的路徑多用了2個時間單位 因此,鎖存器后面的路徑必須在原來的基礎上(10個時間單位)少用2個時間單位。我們可以這樣來看,通往鎖存器的路徑向后面的路徑“借用”了2個時間單位。

因此,通往鎖存器的路徑可以從后續(xù)的路徑借用時間(相當于鎖存器是透明的)。

時間借用的時間不需要全部都借。

實際借用的時間只需要滿足路徑時序要求的最小值(鎖存器全部透明時為最大界限)。

以我們這個例子來說:

可以借用的時間單位為5個時間單位。 實際借用的時間為2個時間單位。 默認是10個時間單位,加上額外的2個時間單位,這段信號路徑需要12ns能夠滿足時序要求。我們要注意到F1到F3這段路徑仍然使用了20個時間單位,沒用改變。

只是時間分布改變了。

感謝Catalin Baetoniu,在實際的時序設計中驗證了這些概念。

作者:Sanjay Churiwala,賽靈思公司工具與方法學應用專家

電子發(fā)燒友App

電子發(fā)燒友App

評論