在systemverilog中,如果一個(gè)類沒(méi)有顯式地聲明構(gòu)造函數(shù)(new()),那么編譯仿真工具會(huì)自動(dòng)提供一個(gè)隱式的new()函數(shù)。這個(gè)new函數(shù)會(huì)默認(rèn)地將所有屬性變量。

2022-11-16 09:58:24 2700

2700 SystemVerilog中多態(tài)能夠工作的前提是父類中的方法被聲明為virtual的。

2022-11-28 11:12:42 466

466 SystemVerilog中可以將類屬性聲明為常量,即“只讀”。目的就是希望,別人可以讀但是不能修改它的值。

2022-11-29 10:25:42 1643

1643 在 SystemVerilog 中,聯(lián)合只是信號(hào),可通過(guò)不同名稱和縱橫比來(lái)加以引用。

2023-10-08 15:45:14 593

593

SystemVerilog 接口的開(kāi)發(fā)旨在讓設(shè)計(jì)中層級(jí)之間的連接變得更加輕松容易。 您可以把這類接口看作是多個(gè)模塊共有的引腳集合。

2024-03-04 15:25:22 387

387

SystemVerilog 的VMM 驗(yàn)證方法學(xué)教程教材包含大量經(jīng)典的VMM源代碼,可以實(shí)際操作練習(xí)的例子,更是ic從業(yè)人員的絕佳學(xué)習(xí)資料。SystemVerilog 的VMM 驗(yàn)證方法學(xué)教程教材[hide][/hide]

2012-01-11 11:21:38

本帖最后由 鼻子抽筋 于 2012-2-21 15:41 編輯

SystemVerilog給予Verilog、VHDL和C/C++優(yōu)點(diǎn)為一身的硬件描述語(yǔ)言,很值得學(xué)一學(xué)。1、8-bit up

2012-02-21 15:39:27

SystemVerilog有哪些標(biāo)準(zhǔn)?

2021-06-21 08:09:41

1、SystemVerilog編碼層面提速的若干策略介紹頻繁的函數(shù)/任務(wù)調(diào)用會(huì)增加開(kāi)銷比如:用foreach遍歷方式計(jì)數(shù)(foreach有內(nèi)置函數(shù)),不如單獨(dú)的計(jì)數(shù)器!如下代碼:這樣寫比較慢:這樣寫

2022-08-01 15:13:13

官方的一個(gè)systemverilog詳解,很詳細(xì)。推薦給打算往IC方面發(fā)展的朋友。QQ群374590107歡迎有志于FPGA開(kāi)發(fā),IC設(shè)計(jì)的朋友加入一起交流。一起為中國(guó)的IC加油!!!

2014-06-02 09:47:23

官方的一個(gè)systemverilog詳解,很詳細(xì)。推薦給打算往IC方面發(fā)展的朋友。

2014-06-02 09:30:16

systemverilog的一些基本語(yǔ)法以及和verilog語(yǔ)言之間的區(qū)別。

2015-04-01 14:24:14

將邀請(qǐng)進(jìn)入的團(tuán)隊(duì)成員角色設(shè)定為“engineers”,我是管理員,目前實(shí)測(cè)所有人都可以通過(guò)Altium電腦端對(duì)共享workspace內(nèi)的元件庫(kù)做刪除操作。如何對(duì)約束團(tuán)隊(duì)成員權(quán)限?請(qǐng)大神指點(diǎn)。

2021-09-26 14:45:01

學(xué)快速發(fā)展,這些趨勢(shì)你了解嗎?SystemVerilog + VM是目前的主流,在未來(lái)也將被大量采用,這些語(yǔ)言和方法學(xué),你熟練掌握了嗎?對(duì)SoC芯片設(shè)計(jì)驗(yàn)證感興趣的朋友,可以關(guān)注啟芯工作室推出的SoC芯片

2013-06-10 09:25:55

active read protected stm32 device detected.單片機(jī)無(wú)法下載程序,可以識(shí)別驅(qū)動(dòng)。

2024-03-07 07:20:02

:public、private和protected,默認(rèn)處理是public。2.雙冒號(hào)(::)用法(1)表示“域操作符”例:聲明了一個(gè)類A,類A里聲明了一個(gè)成員函數(shù)void f(),但沒(méi)有在類的聲明里給出f

2015-10-18 10:08:29

大家好,我對(duì)一個(gè) round robin 的 systemverilog 代碼有疑惑。https://www.edaplayground.com/x/2TzD代碼第49和54行是怎么解析呢 ?

2017-03-14 19:16:04

FPGA中接口的連接方式。 ??也許很多FPGA工程師對(duì)SystemVerilog并不是很了解,因?yàn)橐郧暗腇PGA開(kāi)發(fā)工具是不支持SystemVerilog的,導(dǎo)致大家都是用VHDL或者Verilog來(lái)

2021-01-08 17:23:22

在某大型科技公司的招聘網(wǎng)站上看到招聘邏輯硬件工程師需要掌握SystemVerilog語(yǔ)言,感覺(jué)SystemVerilog語(yǔ)言是用于ASIC驗(yàn)證的,那么做FPGA工程師有沒(méi)有必要掌握SystemVerilog語(yǔ)言呢?

2017-08-02 20:30:21

如下圖,先建一個(gè)systemverilog的cell,但是會(huì)報(bào)錯(cuò),求幫解決下。寫個(gè)最簡(jiǎn)單的也會(huì)報(bào)語(yǔ)法錯(cuò)誤。

2021-06-24 06:24:26

我們將展示如何在SystemVerilog中為狀態(tài)機(jī)的命令序列的生成建模,并且我們將看到它是如何實(shí)現(xiàn)更高效的建模,以及實(shí)現(xiàn)更好的測(cè)試生成。?

2021-01-01 06:05:05

剛接觸systemverilog,最近在采用questasim10.1版本進(jìn)行仿真時(shí),發(fā)現(xiàn)貌似questasim不支持?jǐn)U展類的操作?代碼如下:`timescale 1ns/1nsmodule

2016-04-11 09:44:08

。static成員函數(shù)在不創(chuàng)建類對(duì)象的時(shí)候直接調(diào)用。很不幸的是MATLAB不支持static成員變量,只能定義static成員函數(shù),于是很多在C++中輕而易取實(shí)現(xiàn)的功能,在MATLAB中卻成了捉襟見(jiàn)肘

2012-03-07 10:42:47

結(jié)果。AND、NAND或NOR運(yùn)算符是X-optimistic。對(duì)于歸約運(yùn)算符,如果操作數(shù)中的任何位為0,結(jié)果將為1’b0。對(duì)于歸約NAND,如果操作數(shù)中的任何位為0,結(jié)果將為1’b1。類似地,對(duì)于

2022-10-20 15:03:15

新成員報(bào)個(gè)到,學(xué)習(xí)c51,以后請(qǐng)群主多多指教

2013-01-08 15:07:54

多態(tài)(Polymorphism) ,從字面意思上看指的是多種形式,在OOP(面向?qū)ο缶幊?中指的是同一個(gè)父類的函數(shù)可以體現(xiàn)為不同的行為。在SystemVerilog中,指的是我們可以使用父類句柄來(lái)

2022-12-05 17:34:00

類成員函數(shù)中const的使用,有什么注意事項(xiàng)?

2021-04-26 06:42:30

)(或聯(lián)合(union))的數(shù)據(jù)成員,第一個(gè)數(shù)據(jù)成員放在offset為0的地方,以后每個(gè)數(shù)據(jù)成員的對(duì)齊按照#pragma pack指定的數(shù)值和這個(gè)數(shù)據(jù)成員自身長(zhǎng)度中,比較小的那個(gè)進(jìn)行...

2021-12-17 07:10:20

)[gVcapVencVdecVdis_ipcBitsCtrl.thrObj.exitBitsInThread = TRUE;gVcapVencVdecVdis_ipcBitsCtrl.thrObj.exitBitsOutThread = TRUE;]請(qǐng)教其中exitBitsInThread和exitBitsOutThread成員的含義,謝謝!

2019-02-15 08:35:30

導(dǎo)入SystemVerilog程序包意味著什么?

2020-12-11 06:53:29

Systemverilog數(shù)據(jù)類型l 合并數(shù)組和非合并數(shù)組1)合并數(shù)組:存儲(chǔ)方式是連續(xù)的,中間沒(méi)有閑置空間。例如,32bit的寄存器,可以看成是4個(gè)8bit的數(shù)據(jù),或者也可以看成是1個(gè)32bit

2015-08-27 14:50:39

2打兩拍systemverilog與VHDL編碼1 本章目錄1)FPGA簡(jiǎn)介2)SystemVerilog簡(jiǎn)介3)VHDL簡(jiǎn)介4)打兩拍verilog編碼5)打兩拍VHDL編碼6)結(jié)束語(yǔ)2 FPGA

2021-07-26 06:19:28

SystemVerilog Assertion Handbook1 ROLE OF SYSTEMVERILOG ASSERTIONSIN A VERIFICATION METHODOLOGY

2009-07-22 14:08:48 188

188 SystemVerilog Assertion Handbook1 ROLE OF SYSTEMVERILOG ASSERTIONSIN A VERIFICATION METHODOLOGY

2009-07-22 14:12:50 20

20 Section 1 Introduction to SystemVerilog ..... 1Section 2 Literal Values... 42.1 Introduction

2009-07-22 14:18:46 39

39 Chapter 1: Introduction to SystemVerilogChapter 2: SystemVerilog Declaration SpacesExample 2-1

2009-07-22 14:45:34 0

0 本文利用形式化的方法對(duì)SystemVerilog的指稱語(yǔ)義進(jìn)行研究,采用EBES(extendedbundle event structure)作為抽象模型,以便更好的描述SystemVerilog真并發(fā)的特點(diǎn)。我們的主要工作是:首先,

2009-12-22 14:01:07 12

12 如何采用SystemVerilog 來(lái)改善基于FPGA 的ASIC 原型關(guān)鍵詞:FPGA, ASIC, SystemVerilog摘要:ASIC 在解決高性能復(fù)雜設(shè)計(jì)概念方面提供了一種解決方案,但是ASIC 也是高投資風(fēng)險(xiǎn)的,如90nm ASIC/S

2010-02-08 09:53:33 10

10 ±15kV ESD-Protected, Single-/Dual-Channel, Bidirectional Low-Level Translators in Tiny Packages

2008-08-20 12:25:17 804

804 就 SystemC 和 SystemVerilog 這兩種語(yǔ)言而言, SystemC 是C++在硬件支持方面的擴(kuò)展,而 SystemVerilog 則繼承了 Verilog,并對(duì) Verilog 在面向?qū)ο蠛万?yàn)證能力方面進(jìn)行了擴(kuò)展。這兩種語(yǔ)言均支持

2010-08-16 10:52:48 5140

5140 隨著項(xiàng)目復(fù)雜程度的提高,最新的系統(tǒng)語(yǔ)言的聚合可以促進(jìn)生產(chǎn)能力的激增,并為處在電子設(shè)計(jì)自動(dòng)化(EDA)行業(yè)中的設(shè)計(jì)企業(yè)帶來(lái)益處。SystemVerilog和SystemC這兩種語(yǔ)言在設(shè)計(jì)流

2010-08-25 09:44:47 1181

1181 SystemVerilog 是過(guò)去10年來(lái)多方面技術(shù)發(fā)展和實(shí)際試驗(yàn)的結(jié)晶,包括硬件描述語(yǔ)言(HDL)、硬件驗(yàn)證語(yǔ)言(HVL)、SystemC、Superlog和屬性規(guī)范語(yǔ)言。它們都從技術(shù)和市場(chǎng)的成敗中得到了豐富的經(jīng)

2010-09-07 09:55:16 1118

1118 文章主要介紹《VMM for SystemVerilog》一書描述的如何利用SystemVerilog語(yǔ)言,采用驗(yàn)證方法學(xué)以及驗(yàn)證庫(kù)開(kāi)發(fā)出先進(jìn)驗(yàn)證環(huán)境。文章分為四部分,第一部分概述了用SystemVerilog語(yǔ)言驗(yàn)證復(fù)雜S

2011-05-09 15:22:02 52

52 在介紹SystemVerilog 斷言的概念、使用斷言的好處、斷言的分類、斷言的組成以及斷言如何被插入到被測(cè)設(shè)計(jì)(DUT)的基礎(chǔ)上,本文詳細(xì)地介紹了如何使用不同的斷言語(yǔ)句對(duì)信號(hào)之間的復(fù)

2011-05-24 16:35:19 0

0 文中分析了基于Systemverilog驗(yàn)證環(huán)境的結(jié)構(gòu),并在介紹I 2 C總線協(xié)議的基礎(chǔ)上,重點(diǎn)論述了驗(yàn)證環(huán)境中事務(wù)產(chǎn)生器及驅(qū)動(dòng)器的設(shè)計(jì)。

2011-12-22 17:20:21 27

27 在用STVP下載程序的時(shí)候提示:the device is protected!,此時(shí)的實(shí)測(cè)解決方案詳細(xì)請(qǐng)見(jiàn)附件。

2016-06-08 15:30:29 81

81 LTC7003: Fast 60V Protected High Side NMOS Static Switch Driver Data Sheet

2021-02-19 10:31:12 1

1 手冊(cè)的這一部分探討了使用SystemVerilog進(jìn)行驗(yàn)證,然后查看了使用SystemVerilog的優(yōu)點(diǎn)和缺點(diǎn)。

2021-03-29 10:32:46 23

23 作者:limanjihe ?https://blog.csdn.net/limanjihe/article/details/83005713 SystemVerilog是一種硬件描述和驗(yàn)證語(yǔ)言

2021-10-11 10:35:38 2042

2042 本文定義了通常用于描述使用SystemVerilog對(duì)硬件功能進(jìn)行建模的詳細(xì)級(jí)別的術(shù)語(yǔ)。

2022-03-30 11:42:02 1336

1336 默認(rèn)情況下,結(jié)構(gòu)體會(huì)被非壓縮的。這意味著結(jié)構(gòu)體的成員被視為獨(dú)立變量或常量,并以一個(gè)共同的名稱分組在一起。SystemVerilog沒(méi)有指定軟件工具應(yīng)該如何存儲(chǔ)非壓縮結(jié)構(gòu)體的成員。不同的軟件工具具對(duì)于結(jié)構(gòu)體的存儲(chǔ)分布也是不同的。

2022-06-30 09:54:02 725

725 利用Systemverilog+UVM搭建soc驗(yàn)證環(huán)境

2022-08-08 14:35:05 5

5 IEEE SystemVerilog標(biāo)準(zhǔn):統(tǒng)一的硬件設(shè)計(jì)規(guī)范和驗(yàn)證語(yǔ)言

2022-08-25 15:52:21 0

0 HDLBits 是一組小型電路設(shè)計(jì)習(xí)題集,使用 Verilog/SystemVerilog 硬件描述語(yǔ)言 (HDL) 練習(xí)數(shù)字硬件設(shè)計(jì)~

2022-08-31 09:06:59 1168

1168 SystemVerilog中枚舉類型雖然屬于一種“強(qiáng)類型”,但是枚舉類型還是提供了一些“不正經(jīng)”的用法可以實(shí)現(xiàn)一些很常見(jiàn)的功能,本文將示例一些在枚舉類型使用過(guò)程中的一些“不正經(jīng)”用法,并給出一些使用建議。

2022-09-01 14:20:14 1057

1057 Block,也就是語(yǔ)句塊,SystemVerilog提供了兩種類型的語(yǔ)句塊,分別是begin…end為代表的順序語(yǔ)句塊,還有以fork…join為代表的并發(fā)語(yǔ)句塊。

2022-09-14 10:27:30 866

866 event是SystemVerilog語(yǔ)言中的一個(gè)強(qiáng)大特性,可以支持多個(gè)并發(fā)進(jìn)程之間的同步。

2022-10-17 10:21:33 1024

1024 SystemVerilog casting意味著將一種數(shù)據(jù)類型轉(zhuǎn)換為另一種數(shù)據(jù)類型。在將一個(gè)變量賦值給另一個(gè)變量時(shí),SystemVerilog要求這兩個(gè)變量具有相同的數(shù)據(jù)類型。

2022-10-17 14:35:40 1960

1960 學(xué)習(xí)Systemverilog必備的手冊(cè),很全且介紹詳細(xì)

2022-10-19 16:04:06 2

2 SystemVerilog提供了幾個(gè)內(nèi)置方法來(lái)支持?jǐn)?shù)組搜索、排序等功能。

2022-10-31 10:10:37 1760

1760 SystemVerilog中除了數(shù)組、隊(duì)列和關(guān)聯(lián)數(shù)組等數(shù)據(jù)結(jié)構(gòu),這些數(shù)據(jù)結(jié)構(gòu)還可以嵌套。

2022-11-03 09:59:08 1176

1176 SystemVerilog packages提供了對(duì)于許多不同數(shù)據(jù)類型的封裝,包括變量、task、function、assertion等等,以至于可以在多個(gè)module中共享。

2022-11-07 09:44:45 862

862 SystemVerilog“struct”表示相同或不同數(shù)據(jù)類型的集合。

2022-11-07 10:18:20 1852

1852 SystemVerilog union允許單個(gè)存儲(chǔ)空間以不同的數(shù)據(jù)類型存在,所以u(píng)nion雖然看起來(lái)和struct一樣包含了很多個(gè)成員,實(shí)際上物理上共享相同的存儲(chǔ)區(qū)域。

2022-11-09 09:41:28 575

575 tagged union包含一個(gè)隱式成員,該成員存儲(chǔ)tag,也就是標(biāo)記,它表示這個(gè)union最終存儲(chǔ)的到底是哪一個(gè)成員。

2022-11-10 10:02:06 1088

1088 unpacked union中各個(gè)成員的大小可以是不同的。

2022-11-11 09:33:19 408

408 在systemverilog中方法也可以聲明為“static”。靜態(tài)方法意味著對(duì)類的所有對(duì)象實(shí)例共享。在內(nèi)存中,靜態(tài)方法的聲明存儲(chǔ)在一個(gè)同一個(gè)地方,所有對(duì)象實(shí)例都可以訪問(wèn)。

2022-11-18 09:31:44 572

572 SystemVerilog中的句柄賦值和對(duì)象復(fù)制的概念是有區(qū)別的。

2022-11-21 10:32:59 523

523 要想理解清楚SystemVerilog語(yǔ)言中的Upcasting和Downcasting概念,最好的方式從內(nèi)存分配的角度理解。

2022-11-24 09:58:15 925

925 SystemVerilog是一種硬件描述和驗(yàn)證語(yǔ)言(HDVL),它基于IEEE1364-2001 Verilog硬件描述語(yǔ)言(HDL),并對(duì)其進(jìn)行了擴(kuò)展,包括擴(kuò)充了 C語(yǔ)言 數(shù)據(jù)類型、結(jié)構(gòu)、壓縮

2022-12-08 10:35:05 1262

1262 SystemVerilog中Semaphore(旗語(yǔ))是一個(gè)多個(gè)進(jìn)程之間同步的機(jī)制之一,這里需要同步的原因是這多個(gè)進(jìn)程共享某些資源。

2022-12-12 09:50:58 2344

2344 上一篇文章介紹了SystemVerilog的各種隨機(jī)化方法,本文將在其基礎(chǔ)上引入SystemVerilog的隨機(jī)約束方法(constraints)。通過(guò)使用隨機(jī)約束,我們可以將隨機(jī)限制在一定的空間內(nèi),有針對(duì)性地提高功能覆蓋率。

2023-01-21 17:03:00 1519

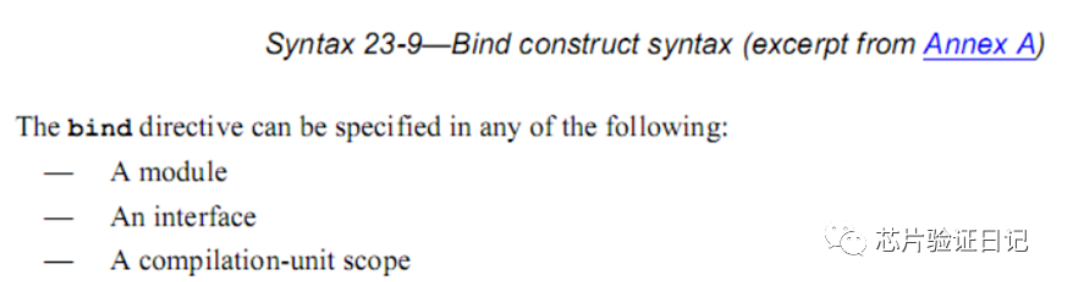

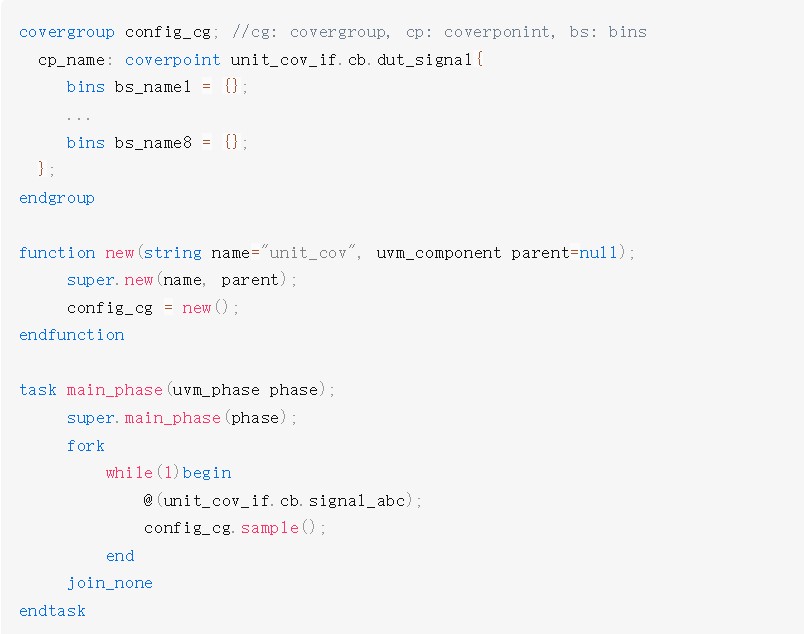

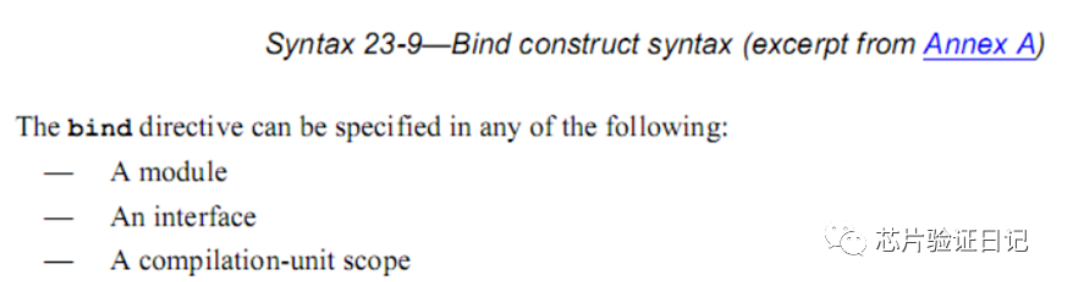

1519 bind是systemverilog中一個(gè)重要的知識(shí)點(diǎn),很多時(shí)候能夠在驗(yàn)證中發(fā)揮重要的作用,今天就針對(duì)這個(gè)知識(shí)點(diǎn)做一個(gè)梳理,希望能幫助到大家。

2023-01-11 08:59:03 6173

6173

數(shù)獨(dú)是一種非常流行的游戲,數(shù)獨(dú)本質(zhì)上也是一個(gè)約束問(wèn)題,所以我們可以讓SystemVerilog的約束求解器來(lái)幫助我們解決。 約束求解器的精妙之處就是,我們只描述約束限制,繁重的數(shù)值生成工作由工具來(lái)幫我們完成。 你只需“既要...又要...”,其他的讓下人干吧。

2023-03-08 14:06:00 943

943 我們?cè)诠ぷ髦谐3?huì)針對(duì)數(shù)組施加各式的約束,下面列舉一下有趣的Systemverilog數(shù)組約束示例。

2023-03-08 13:12:00 591

591 SystemVerilog Interface是modport的一種,但比簡(jiǎn)單的輸入、輸出或輸入輸出端口的功能更多。

2023-04-28 14:10:06 1233

1233

SystemVerilog Interface是modport的一種,但比簡(jiǎn)單的輸入、輸出或輸入輸出端口的功能更多。

2023-04-28 14:12:22 1924

1924

寫過(guò)Verilog和systemverilog的人肯定都用過(guò)系統(tǒng)自定義的函數(shù)$display,這是預(yù)定好的,可以直接調(diào)用的功能。

2023-05-16 09:27:02 581

581

我們?cè)诠ぷ髦谐3?huì)針對(duì)數(shù)組施加各式的約束,下面列舉一下有趣的**Systemverilog數(shù)組約束**示例

2023-05-30 11:13:21 402

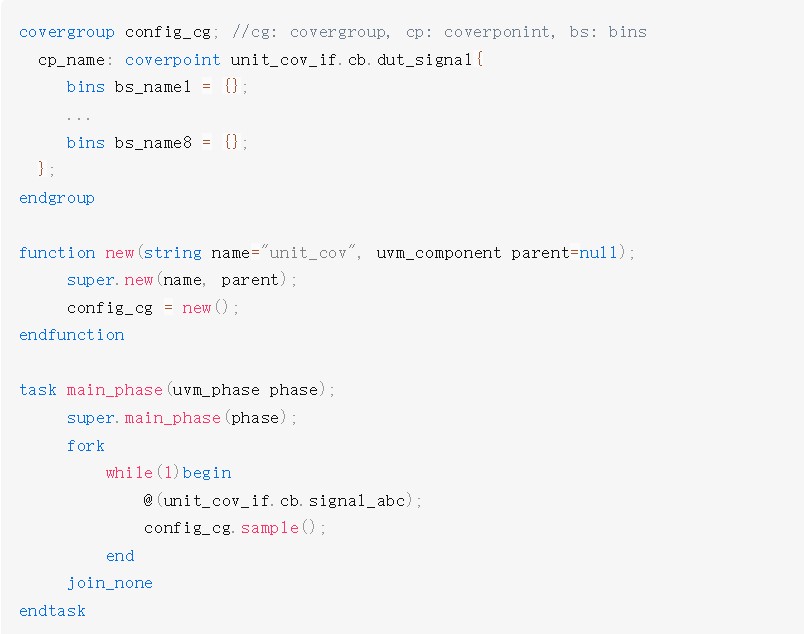

402 SystemVerilog是一名芯片驗(yàn)證工程師,必須掌握的一門語(yǔ)言,其中Function Coverage是必須要懂的知識(shí)點(diǎn)之一;

2023-06-04 16:30:24 3702

3702

在SystemVerilog中,我們知道可以使用動(dòng)態(tài)數(shù)組實(shí)現(xiàn)數(shù)組元素個(gè)數(shù)的動(dòng)態(tài)分配,即隨用隨分

2023-06-09 09:46:24 3977

3977

在systemverilog中,net用于對(duì)電路中連線進(jìn)行建模,driving strength(驅(qū)動(dòng)強(qiáng)度)可以讓net變量值的建模更加精確。

2023-06-14 15:50:16 751

751

為了確保驗(yàn)證的完備性,我們需要量化驗(yàn)證目標(biāo)。SystemVerilog提供了一套豐富的覆蓋率建模方式。

2023-06-25 10:44:16 520

520 SystemVeirlog的全面支持是開(kāi)發(fā)商用仿真器的第一道門檻。市面上可以找到不少基于純Verilog的仿真器,但是真正能完整支持SystemVerilog 的仍然屈指可數(shù)。如何全面地支持SystemVerilog語(yǔ)言,是開(kāi)發(fā)仿真器的一個(gè)重要任務(wù)。

2023-07-14 15:15:25 354

354

本文講一下SystemVerilog的time slot里的regions以及events的調(diào)度。SystemVerilog語(yǔ)言是根據(jù)離散事件執(zhí)行模型定義的,由events驅(qū)動(dòng)。

2023-07-12 11:20:32 775

775

在SystemVerilog中,輸出信息顯示時(shí)間時(shí),經(jīng)常會(huì)在輸出信息格式中指定“%t”格式符,一般情況下“%t”輸出的格式都是固定的,但是這樣固定的輸出顯示的時(shí)間可能有時(shí)會(huì)讓用戶看起來(lái)感覺(jué)比較詫異,例如下面的示例。

2023-08-16 09:41:58 630

630

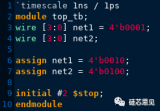

在Verilog和SystemVerilog中經(jīng)常需要在使用變量或者線網(wǎng)之前,期望變量和線網(wǎng)有對(duì)應(yīng)的初始值

2023-08-25 09:47:56 546

546

上一篇文章《暗藏玄機(jī)的SV隨機(jī)化》介紹了SystemVerilog的各種隨機(jī)化方法,本文將在其基礎(chǔ)上引入SystemVerilog的隨機(jī)約束方法(constraints)。通過(guò)使用隨機(jī)約束,我們可以將隨機(jī)限制在一定的空間內(nèi),有針對(duì)性地提高功能覆蓋率。

2023-09-24 12:15:30 396

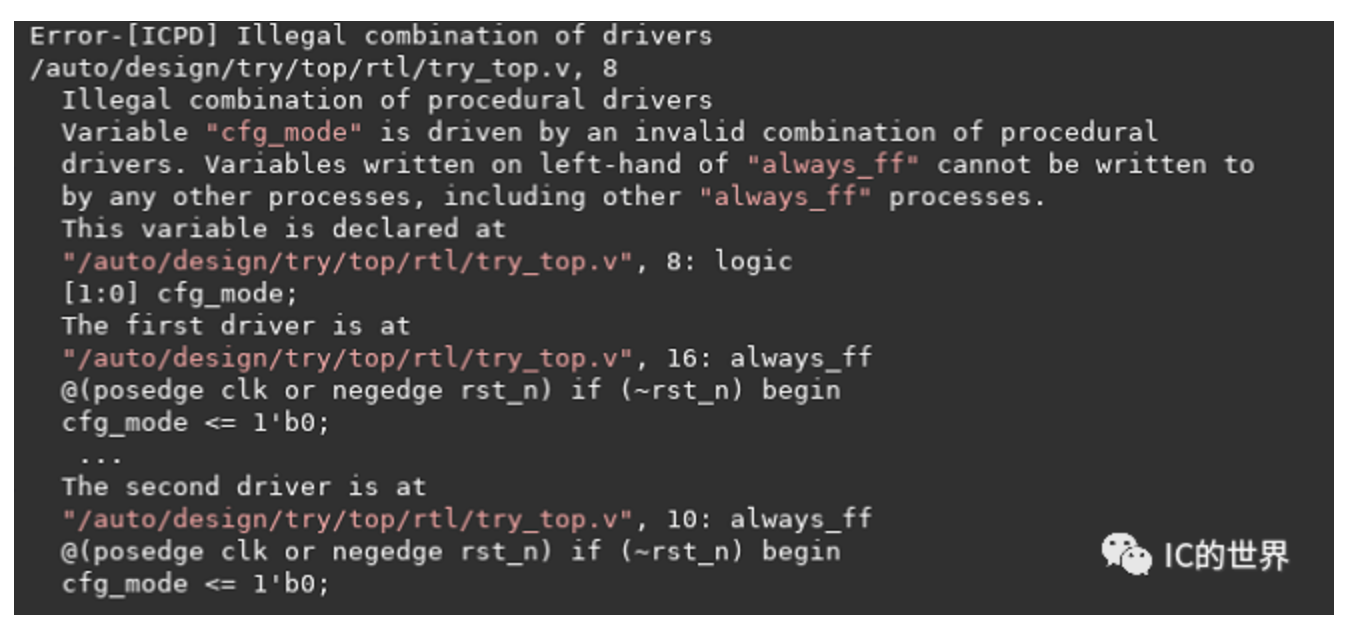

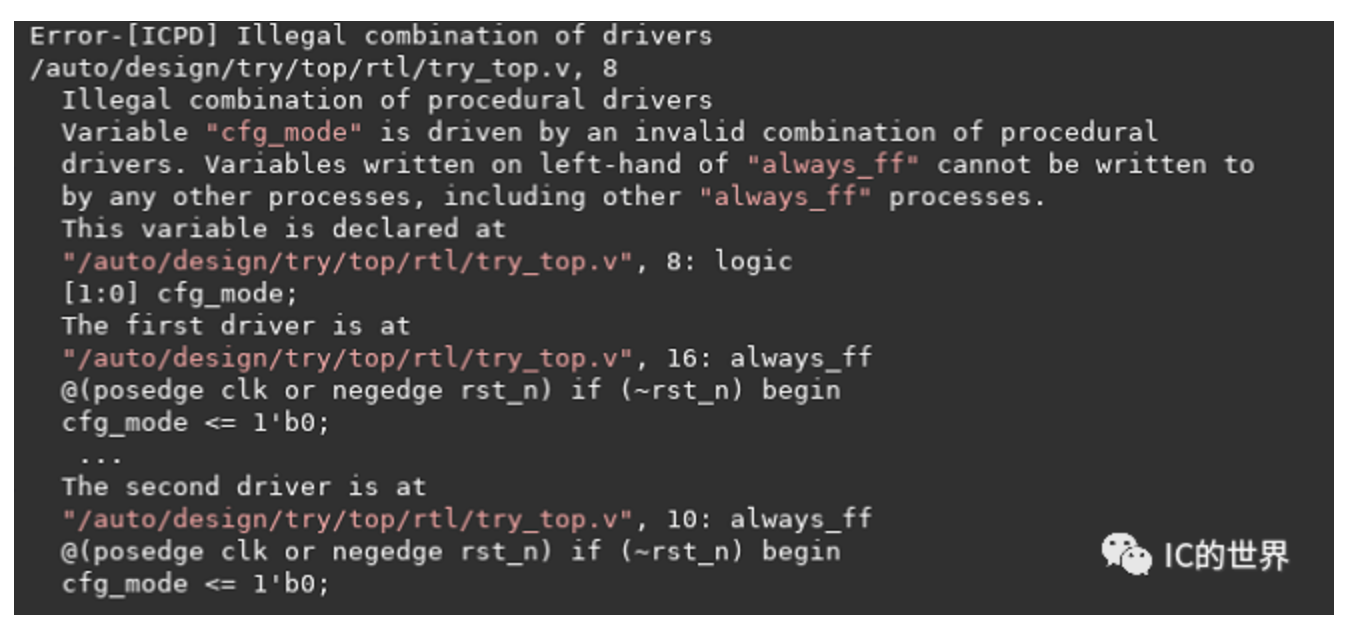

396 在systemverilog協(xié)議中,logic定義四態(tài)值,即向量(vector)的每個(gè)位(bit)可以是邏輯0, 1, Z或X,與verilog協(xié)議中的reg很接近。但是logic有個(gè)很明顯的優(yōu)勢(shì),不允許多驅(qū)動(dòng)。

2023-09-28 17:34:37 1928

1928

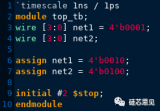

在SystemVerilog中,類型可以分為線網(wǎng)(net)和變量(variable)。線網(wǎng)的賦值設(shè)定與Verilog的要求相同,即線網(wǎng)賦值需要使用連續(xù)賦值語(yǔ)句(assign),而不應(yīng)該出現(xiàn)在過(guò)程塊(initial/always)中。

2023-10-13 14:53:19 667

667

談到SystemVerilog,很多工程師都認(rèn)為SystemVerilog僅僅是一門驗(yàn)證語(yǔ)言,事實(shí)上不只如此。傳統(tǒng)的Verilog和VHDL被稱為HDL(Hardware Description

2023-10-19 11:19:19 342

342

在systemverilog協(xié)議中,logic定義四態(tài)值,即向量(vector)的每個(gè)位(bit)可以是邏輯0, 1, Z或X,與verilog協(xié)議中的reg很接近。但是logic有個(gè)很明顯的優(yōu)勢(shì),不允許多驅(qū)動(dòng)。

2023-10-26 09:32:24 324

324

我們?cè)購(gòu)膶?duì)可綜合代碼的支持角度看看SystemVerilog相比于Verilog的優(yōu)勢(shì)。針對(duì)硬件設(shè)計(jì),SystemVerilog引入了三種進(jìn)程always_ff,always_comb

2023-10-26 10:05:09 289

289

本文分享一些SystemVerilog的coding guideline。

2023-11-22 09:17:30 272

272

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論