1.1 嵌入式網(wǎng)絡(luò)簡(jiǎn)介

提起網(wǎng)絡(luò),我們一般想到的硬件就是“網(wǎng)卡”,現(xiàn)在網(wǎng)卡已經(jīng)是通過(guò)一個(gè)芯片來(lái)完成了,嵌入式網(wǎng)絡(luò)硬件分為兩部分:MAC和PHY,大家都是通過(guò)看數(shù)據(jù)手冊(cè)來(lái)判斷一款SOC是否支持網(wǎng)絡(luò),如果一款芯片數(shù)據(jù)手冊(cè)說(shuō)自己支持網(wǎng)絡(luò),一般都是說(shuō)的這款SOC內(nèi)置MAC,MAC類(lèi)似I2C控制器、SPI控制器一樣的外設(shè)。

但是光有MAC還不能直接驅(qū)動(dòng)網(wǎng)絡(luò),還需要另外一個(gè)芯片:PHY,因此對(duì)于內(nèi)置MAC的SOC,其外部必須搭配一個(gè)PHY芯片。內(nèi)部沒(méi)有MAC的SOC芯片,就需要使用外置的MAC+PHY一體芯片了,這里就要牽扯出常見(jiàn)的兩個(gè)嵌入式網(wǎng)絡(luò)硬件方案了。

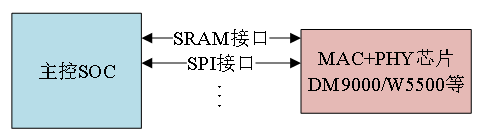

1.SOC內(nèi)部沒(méi)有網(wǎng)絡(luò)MAC外設(shè)

對(duì)于內(nèi)部沒(méi)有MAC的SOC芯片,可以使用外置 MAC+PHY一體的網(wǎng)絡(luò)芯片來(lái)實(shí)現(xiàn)網(wǎng)絡(luò)功能。比如三星linux開(kāi)發(fā)板里面用的最多的DM9000,DM9000對(duì)SOC提供了一個(gè)SRAM接口,SOC會(huì)以SRAM的方式操作DM9000。

有些外置的網(wǎng)絡(luò)芯片更強(qiáng)大,內(nèi)部甚至集成了硬件TCP/IP協(xié)議棧,對(duì)外提供一個(gè)SPI接口,比如W5500。這個(gè)一般用于單片機(jī)領(lǐng)域,單片機(jī)通過(guò)SPI接口與W5500進(jìn)行通信,由于W5500內(nèi)置了硬件TCP/IP協(xié)議棧,因此單片機(jī)就不需要移植軟件協(xié)議棧,直接通過(guò)SPI來(lái)操作W5500,簡(jiǎn)化了單片機(jī)聯(lián)網(wǎng)方案。

這種方案的優(yōu)點(diǎn)就是讓不支持網(wǎng)絡(luò)的SOC能夠另辟蹊徑,實(shí)現(xiàn)網(wǎng)絡(luò)功能,但是缺點(diǎn)就是網(wǎng)絡(luò)效率不高,因?yàn)橐话阈酒瑑?nèi)置的MAC會(huì)有網(wǎng)絡(luò)加速引擎,比如網(wǎng)絡(luò)專(zhuān)用DMA,網(wǎng)絡(luò)處理效率會(huì)很高。而且此類(lèi)芯片網(wǎng)速都不快,基本就是10/100M。另外,相比PHY芯片而言,此類(lèi)芯片的成本也比較高,可選擇比較少。

SOC與外部MAC+PHY芯片的連接如圖1-1所示:

圖1-1 主控SOC與外置MAC+PHY芯片連接

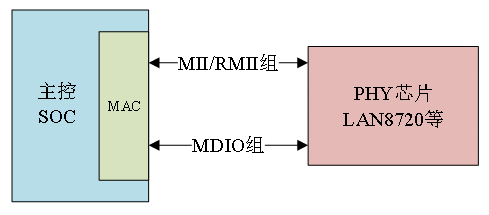

2.SOC內(nèi)部集成網(wǎng)絡(luò)MAC外設(shè)

我們一般說(shuō)某個(gè)SOC支持網(wǎng)絡(luò),說(shuō)的就是他內(nèi)部集成網(wǎng)絡(luò)MAC外設(shè),此時(shí)我們還需要外接一個(gè)網(wǎng)絡(luò)PHY芯片。。

目前幾乎所有支持網(wǎng)絡(luò)的SOC都是內(nèi)置MAC外設(shè),比如STM32F4/F7/H7系列、NXP的I.MX系列,內(nèi)部集成網(wǎng)絡(luò)MAC的優(yōu)點(diǎn)如下:

1)內(nèi)部MAC外設(shè)會(huì)有專(zhuān)用的加速模塊,比如專(zhuān)用的DMA,加速網(wǎng)速數(shù)據(jù)的處理。

2)網(wǎng)速快,可以支持10/100/1000M網(wǎng)速。

3)外接PHY可選擇性多,成本低。

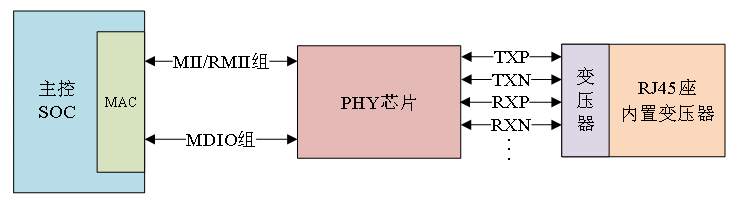

內(nèi)部的MAC外設(shè)會(huì)通過(guò)MII或者RMII接口來(lái)連接外部的PHY芯片,MII/RMII接口用來(lái)傳輸網(wǎng)絡(luò)數(shù)據(jù)。另外主控需要配置或讀取PHY芯片,也就是讀寫(xiě)PHY的內(nèi)部寄存器,所以還需要一個(gè)控制接口,叫做MIDO,MDIO很類(lèi)似IIC,也是兩根線,一根數(shù)據(jù)線叫做MDIO,一根時(shí)鐘線叫做MDC。

SOC內(nèi)部MAC外設(shè)與外部PHY芯片的連接如圖1-2所示:

圖1-2 內(nèi)部MAC與外部PHY之間的連接

大家在做項(xiàng)目的時(shí)候,如果要用到網(wǎng)絡(luò)功能,強(qiáng)烈建議大家選擇內(nèi)部帶有網(wǎng)絡(luò)MAC外設(shè)的主控SOC!I.MX6ULL就有兩個(gè)10M/100M的網(wǎng)絡(luò)MAC外設(shè),正點(diǎn)原子ALPHA開(kāi)發(fā)板板載了兩顆PHY芯片,型號(hào)為L(zhǎng)AN8720。因此,本章節(jié)只講解SOC內(nèi)部MAC+外置PHY芯片這種方案。

1.1.2 MII/RMII接口

前面我們說(shuō)了,內(nèi)部MAC通過(guò)MII/RMII接口來(lái)與外部的PHY芯片連接,完成網(wǎng)絡(luò)數(shù)據(jù)傳輸,本節(jié)我們就來(lái)學(xué)習(xí)一下什么是MII和RMII接口。

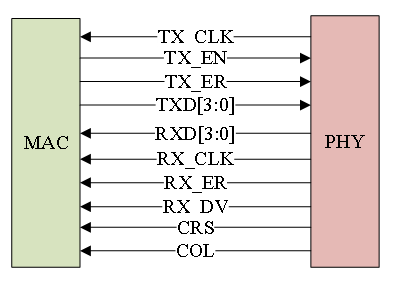

1.MII接口

MII全稱(chēng)是Media Independent Interface,直譯過(guò)來(lái)就是介質(zhì)獨(dú)立接口,它是IEEE-802.3定義的以太網(wǎng)標(biāo)準(zhǔn)接口,MII接口用于以太網(wǎng)MAC連接PHY芯片,連接示意圖如圖1-3所示:

圖1-3 MII接口

MII接口一共有16根信號(hào)線,含義如下:

TX_CLK:發(fā)送時(shí)鐘,如果網(wǎng)速為100M的話時(shí)鐘頻率為25MHz,10M網(wǎng)速的話時(shí)鐘頻率為2.5MHz,此時(shí)鐘由PHY產(chǎn)生并發(fā)送給MAC。

TX_EN:發(fā)送使能信號(hào)。

TX_ER:發(fā)送錯(cuò)誤信號(hào),高電平有效,表示TX_ER有效期內(nèi)傳輸?shù)臄?shù)據(jù)無(wú)效。10Mpbs網(wǎng)速下TX_ER不起作用。

TXD[3:0]:發(fā)送數(shù)據(jù)信號(hào)線,一共4根。

RXD[3:0]:接收數(shù)據(jù)信號(hào)線,一共4根。

RX_CLK:接收時(shí)鐘信號(hào),如果網(wǎng)速為100M的話時(shí)鐘頻率為25MHz,10M網(wǎng)速的話時(shí)鐘頻率為2.5MHz,RX_CLK也是由PHY產(chǎn)生的。

RX_ER:接收錯(cuò)誤信號(hào),高電平有效,表示RX_ER有效期內(nèi)傳輸?shù)臄?shù)據(jù)無(wú)效。10Mpbs網(wǎng)速下RX_ER不起作用。

RX_DV:接收數(shù)據(jù)有效,作用類(lèi)似TX_EN。

CRS:載波偵聽(tīng)信號(hào)。

COL:沖突檢測(cè)信號(hào)。

MII接口的缺點(diǎn)就是所需信號(hào)線太多,這還沒(méi)有算MDIO和MDC這兩根管理接口的數(shù)據(jù)線,因此MII接口使用已經(jīng)越來(lái)越少了。

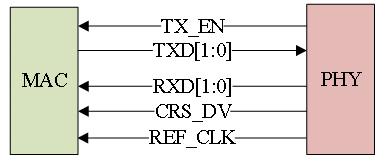

2.RMII接口

RMII全稱(chēng)是Reduced Media Independent Interface,翻譯過(guò)來(lái)就是精簡(jiǎn)的介質(zhì)獨(dú)立接口,也就是MII接口的精簡(jiǎn)版本。RMII接口只需要7根數(shù)據(jù)線,相比MII直接減少了9根,極大的方便了板子布線,RMII接口連接PHY芯片的示意圖如圖1-4所示:

圖1-4 RMII接口

TX_EN:發(fā)送使能信號(hào)。

TXD[1:0]:發(fā)送數(shù)據(jù)信號(hào)線,一共2根。

RXD[1:0]:接收數(shù)據(jù)信號(hào)線,一共2根。

CRS_DV:相當(dāng)于MII接口中的RX_DV和CRS這兩個(gè)信號(hào)的混合。

REF_CLK:參考時(shí)鐘,由外部時(shí)鐘源提供, 頻率為50MHz。這里與MII不同,MII的接收和發(fā)送時(shí)鐘是獨(dú)立分開(kāi)的,而且都是由PHY芯片提供的。

除了MII和RMII以外,還有其他接口,比如GMII、RGMII、SMII、SMII等,關(guān)于其他接口基本都是大同小異的,這里就不做講解了。正點(diǎn)原子ALPAH開(kāi)發(fā)板上的兩個(gè)網(wǎng)口都是采用RMII接口來(lái)連接MAC與外部PHY芯片。

1.1.3 MDIO接口

MDIO全稱(chēng)是Management Data Input/Output,直譯過(guò)來(lái)就是管理數(shù)據(jù)輸入輸出接口,是一個(gè)簡(jiǎn)單的兩線串行接口,一根MDIO數(shù)據(jù)線,一根MDC時(shí)鐘線。驅(qū)動(dòng)程序可以通過(guò)MDIO和MDC這兩根線訪問(wèn)PHY芯片的任意一個(gè)寄存器。MDIO接口支持多達(dá)32個(gè)PHY。同一時(shí)刻內(nèi)只能對(duì)一個(gè)PHY進(jìn)行操作,那么如何區(qū)分這32個(gè)PHY芯片呢?和IIC一樣,使用

器件地址即可。同一MDIO接口下的所有PHY芯片,其器件地址不能沖突,必須保證唯一,具體器件地址值要查閱相應(yīng)的PHY數(shù)據(jù)手冊(cè)。

因此,MAC和外部PHY芯片進(jìn)行連接的時(shí)候主要是MII/RMII和MDIO接口,另外可能還需要復(fù)位、中斷等其他引腳。

1.1.4 RJ45接口

網(wǎng)絡(luò)設(shè)備是通過(guò)網(wǎng)線連接起來(lái)的,插入網(wǎng)線的叫做RJ45座,

RJ45座要與PHY芯片連接在一起,但是中間需要一個(gè)網(wǎng)絡(luò)變壓器,網(wǎng)絡(luò)變壓器用于隔離以及濾波等,網(wǎng)絡(luò)變壓器也是一個(gè)芯片,

但是現(xiàn)在很多RJ45座子內(nèi)部已經(jīng)集成了網(wǎng)絡(luò)變壓器,比如最常用的HR911105A就是內(nèi)置網(wǎng)絡(luò)變壓器的RJ45座。內(nèi)置網(wǎng)絡(luò)變壓器的RJ45座和不內(nèi)置的引腳一樣,但是一般不內(nèi)置的RJ45座會(huì)短一點(diǎn)。

因此,大家在畫(huà)板的時(shí)候一定要考慮你所使用的RJ45座是否內(nèi)置網(wǎng)絡(luò)變壓器,如果不內(nèi)置的話就要自行添加網(wǎng)絡(luò)變壓器部分電路!同理,如果你所設(shè)計(jì)的硬件是需要內(nèi)置網(wǎng)絡(luò)變壓器的RJ45座,肯定不能隨便焊接一個(gè)不內(nèi)置變壓器的RJ45座,否則網(wǎng)絡(luò)工作不正常!

RJ45座子上一般有兩個(gè)燈,一個(gè)黃色(橙色),一個(gè)綠色,綠色亮的話表示網(wǎng)絡(luò)連接正常,黃色閃爍的話說(shuō)明當(dāng)前正在進(jìn)行網(wǎng)絡(luò)通信。這兩個(gè)燈由PHY芯片控制,PHY芯片會(huì)有兩個(gè)引腳來(lái)連接RJ45座上的這兩個(gè)燈。內(nèi)部MAC+外部PHY+RJ45座(內(nèi)置網(wǎng)絡(luò)變壓器)就組成了一個(gè)完整的嵌入式網(wǎng)絡(luò)接口硬件,如圖1-7所示:

圖1-7 嵌入式網(wǎng)絡(luò)硬件接口示意圖

1.1.5 PHY芯片基礎(chǔ)知識(shí)

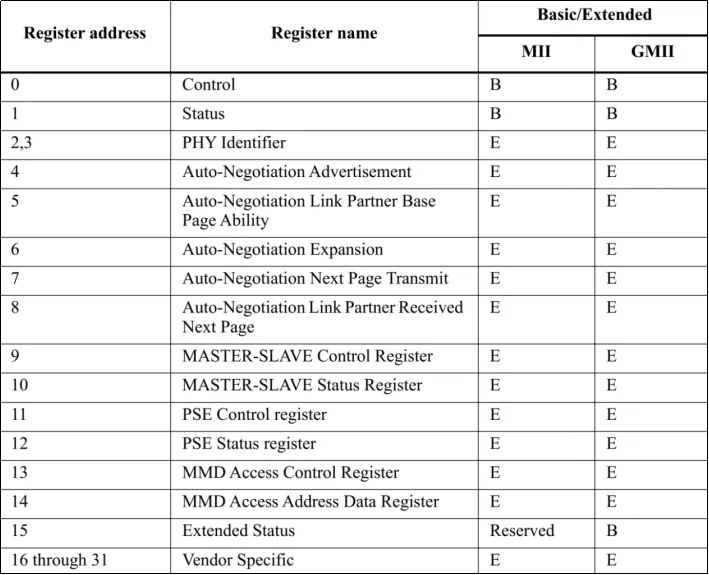

PHY是IEEE 802.3規(guī)定的一個(gè)標(biāo)準(zhǔn)模塊,前面說(shuō)了,SOC可以對(duì)PHY進(jìn)行配置或者讀取PHY相關(guān)狀態(tài),這個(gè)就需要PHY內(nèi)部寄存器去實(shí)現(xiàn)。PHY芯片寄存器地址空間為5位,地址 0~31共32個(gè)寄存器,IEEE定義了0~15這16個(gè)寄存器的功能,16~31這16個(gè)寄存器由廠商自行實(shí)現(xiàn)。

也就是說(shuō)不管你用的哪個(gè)廠家的PHY芯片,其中0~15這16個(gè)寄存器是一模一樣的。僅靠這16個(gè)寄存器是完全可以驅(qū)動(dòng)起PHY芯片的,至少能保證基本的網(wǎng)絡(luò)數(shù)據(jù)通信,因此Linux內(nèi)核有通用PHY驅(qū)動(dòng),按道理來(lái)講,不管你使用的哪個(gè)廠家的PHY芯片,都可以使用Linux的這個(gè)通用PHY驅(qū)動(dòng)來(lái)驗(yàn)證網(wǎng)絡(luò)工作是否正常。

事實(shí)上在實(shí)際開(kāi)發(fā)中可能會(huì)遇到一些其他的問(wèn)題導(dǎo)致Linux內(nèi)核的通用PHY驅(qū)動(dòng)工作不正常,這個(gè)時(shí)候就需要驅(qū)動(dòng)開(kāi)發(fā)人員去調(diào)試了。但是,隨著現(xiàn)在的PHY芯片性能越來(lái)越強(qiáng)大,32個(gè)寄存器可能滿足不了廠商的需求,因此很多廠商采用分頁(yè)技術(shù)來(lái)擴(kuò)展寄存器地址空間,以求定義更多的寄存器。

這些多出來(lái)的寄存器可以用于實(shí)現(xiàn)廠商特有的一些技術(shù),因此Linux內(nèi)核的通用PHY驅(qū)動(dòng)就無(wú)法驅(qū)動(dòng)這些特色功能了,這個(gè)時(shí)候就需要PHY廠商提供相應(yīng)的驅(qū)動(dòng)源碼了,所以大家也會(huì)在Linux內(nèi)核里面看到很多具體的PHY芯片驅(qū)動(dòng)源碼。

不管你的PHY芯片有多少特色功能,按道理來(lái)講,Linux內(nèi)核的通用PHY驅(qū)動(dòng)是絕對(duì)可以讓你這PHY芯片實(shí)現(xiàn)基本的網(wǎng)絡(luò)通信,因此大家也不用擔(dān)心更換PHY芯片以后網(wǎng)絡(luò)驅(qū)動(dòng)編寫(xiě)是不是會(huì)很復(fù)雜。

IEEE802.3協(xié)議英文原版中的 “22.2.4 Management functions”章節(jié),此章節(jié)對(duì)PHY的前16個(gè)寄存器功能進(jìn)行了規(guī)定,如圖1-8所示:

圖1-8 IEEE規(guī)定的前16個(gè)寄存器

關(guān)于這16個(gè)寄存器的內(nèi)容協(xié)議里面也進(jìn)行了詳細(xì)的講解,這里就不分析了。大家可以找個(gè)具體的PHY芯片數(shù)據(jù)手冊(cè)對(duì)比看一下,比如百M(fèi)網(wǎng)絡(luò)最常用的LAN8720A這個(gè)PHY,大家可以看一下LAN8720前面幾個(gè)寄存器結(jié)構(gòu)是否和圖1-8中的一樣。

審核編輯:劉清

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論