作為賽靈思的現場工程師,我常常問這樣的問題:我們是否能夠提供一款其功能可滿足客戶所有獨特設計要求的DSP內核。有時候內核會太大,太小或者不夠快。有時,我們會開發一款能確切滿足客戶需求的內核,并迅速以COREGeneratorTM商標推出。不過即便在這種情況下,客戶仍然想要一套特定的DSP功能,而且刻不容緩。在這些情況下,我常常建議他們使用我們器件中的插值查找表來定制他們的DSP功能。

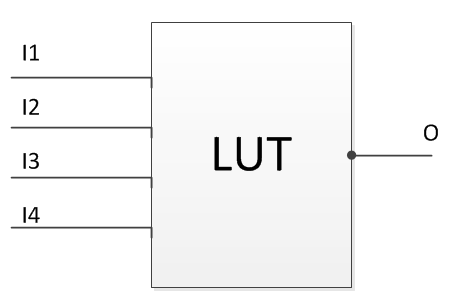

查找表 (LUT) 實質上是一個存儲元件,能夠根據任何給定的輸入狀態組合,“查找”輸出,以確保每個輸入都有確切的輸出。采用LUT來實現 DSP功能具有一些重大優勢:

?您可用諸如MATLAB?或Simulink?等高抽象層編程語言改變LUT內容。

?您可以設計一項DSP功能來運行那些采用離散邏輯運算將極度困難的數學函數,比如 y=log(x)、y=exp(x)、y=1/x、y=sin(x) 等。

?LUT還可輕松執行在可配置邏輯塊 (CLB) 芯片,以及嵌入式乘法單元或DSP48可編程乘法累加 (MAC) 單元方面可能要求過多FPGA資源的復雜數學函數。

不過,以這種方式使用LUT當然也會存在一些弊端。當您使用LUT來實現DSP功能時,您必須使用塊RAM (BRAM) 元件。若執行函數y=sqrt(x)(其中x 表示16位輸入,y 表示18位輸出),每個變量則需要約64個18KBBRAM單元。如果,比如說,您的目標是實現小型化Spartan?器件,或者您有太多的運算需要執行,無法為每個變量省出64個BRAM單元,建議您放棄這種需要如此大量BRAM單元的方法,從系統架構的角度來看,這種方法代價太大。

插值LUT方法不僅具有LUT方法在實現DSP功能時所帶來的各種優勢,而且無需使用太多BRAM單元。采用這種方法,您可以使用來自容量較小的LUT (比如,1000字 LUT)的連續輸出,線性地對其內插,以模擬更大容量的LUT。這樣,您就可以實現比1000 字 LUT更高的數值分辨率。此外,通過這種方法,僅需 1 個 BRAM、1個嵌入式乘法器(或DSP48),以及少數幾個CLB芯片便可實施控制邏輯,因此LUT的使用成本變得更加合理化。而且,從信噪比的角度來看,其數值精度也是非常讓人滿意。

當然,應用插值LUT (ILUT) 方法需要一定的技巧。舉例來說,采用該方法執行y=sqrt(x)函數時,可以清楚地顯示ILUT在面積占用、時序和數值精度方面的性能。我們先大致看一下這個示例,然后我再講解部分實例,說明如何使用這種方法來滿足客戶截然不同的需求,比如讓傳遞函數呈非線性的傳感器實現線性化,以及實施自適應有限脈沖響應(FIR) 濾波器以消除合成孔徑雷達 (SAR)圖像上的斑點噪聲。

使用System Generator for DSP進行設計

為在賽靈思FPGA上實施DPS算法,我借助了采用MathWorks Simulink基于模型設計方法的System Generatorfor DSP設計與綜合工具。System Generator得益于賽靈思在Simulink 環境中的DSP模塊組,可自動調用COREGenerator為DSP構建塊生成高度優化的網表。Simulink是一種雙精度浮點設計工具,而SystemGenerator則是一款定點運算工具。不管怎樣,您只要將這兩種工具協同使用,就可以定義每個信號的總位數以及每個信號的二進制位置,從而在定點運算中巧妙處理分數。仿真結果周期精確、位真,因此您可以方便地將它們與MATLAB腳本或Simulink模塊生成的浮點參考值相比較,以檢查量化誤差。

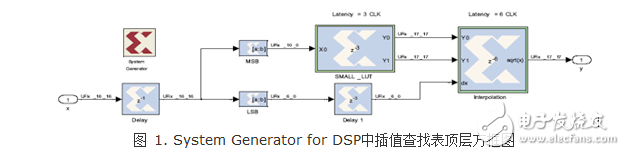

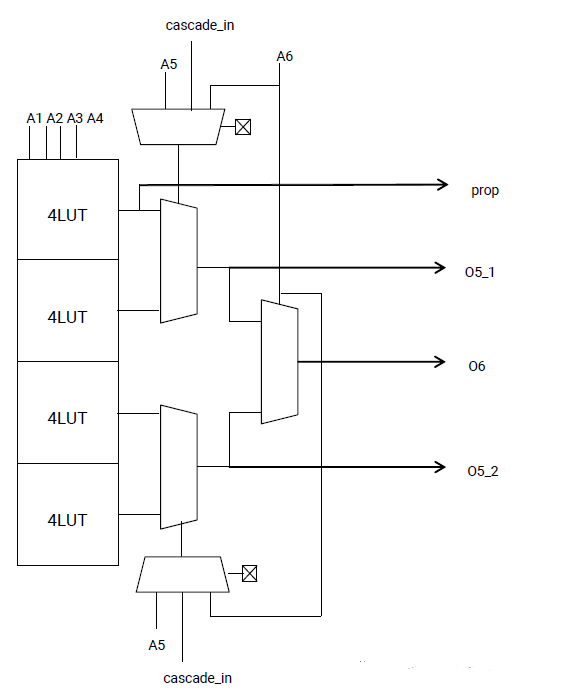

圖1顯示了System Generator中ILUT方案的頂層結構圖。為讓這個方法盡可能一般化,假設nx=16位中的輸入變量 x的取值范圍為0≤x<1,因此其格式為“無符號16位加上二進制點右邊的16 位”,也稱為Ufix_16_16格式。最高有效位 (MSB)和最低有效位 (LSB) 模塊分別對應輸入數據nb=10的最高位和nx-nb=6的最低位。這些信號被命名為x0和dx。y=sqrt(x)輸出則以ny=17位二進制數表示,格式為:Ufix_17_17。

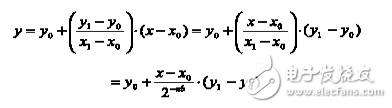

圖2顯示了1000字小容量LUT通過雙端口RAM模塊的部署步驟。由于該模塊系只讀存儲器,布爾常數模塊We_const強制將寫入歸零。信號X0和X0+1則用作ROM表上后續的兩個地址。Data_const模塊的零常數定義了任何ROM字的大小(即本例中的ny)。

下面的公式顯示了以x0為x的最高有效位的情況下,如何在兩個已知點(x0,y0)和(x1,y1)之間插入坐標為(x,y)的點:

注意X1和X0是這個小容量LUT的相鄰地址,它們之間只隔了一個最低有效位。由于這個小容量LUT的地址空間為nb 位,那么該LSB的值為2-nb。

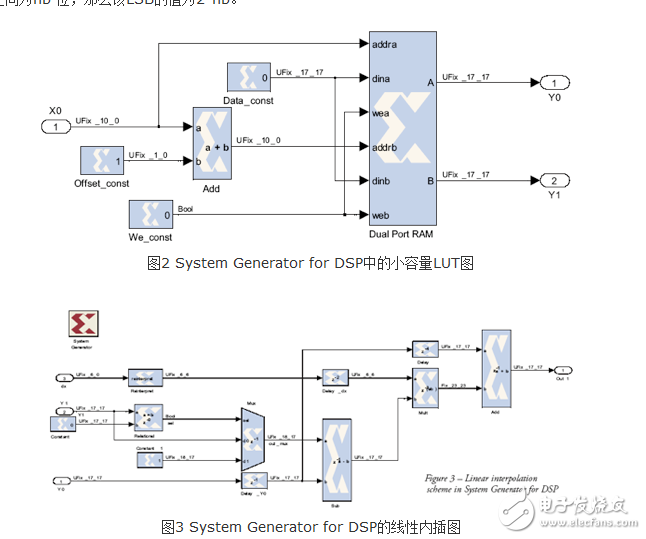

內插步驟見圖3。“Reinterpret”模塊在不改變二進制表示法的情況下,可改變dx=x-x0信號。其重置了二進制小數點(從UFix_6_0到UFix_6_6格式),并輸出nx-nb位二進制數的一個分數,從而計算出 (x-x0)/2-nb 的值。

從硬件角度來看,這些模塊什么都不占用。總的來說(且根據我們通過ILUT方法應用的函數類型),如果y1=0且y0=0,我們可以強制y1-y0=1,這樣我們就可以得到1/2-nb而不是0。我們采用Mux、Rational、Constant和Constant1模塊來執行這項工作。剩下的Mult、Add和Sub模塊則執行線性內插公式。在本例中,我強制Mult模塊的輸出信號為17位分辨率,而非理論上要求的23位,因為總體數值精度對本試驗來說已經足夠。此外,由于y-sqrt(x)函數呈單調遞增,因此所有結果都無符號。換句話說,不同的函數需要對數據類型進行不同的精心調整,但不會與圖3所示的原理相去甚遠。

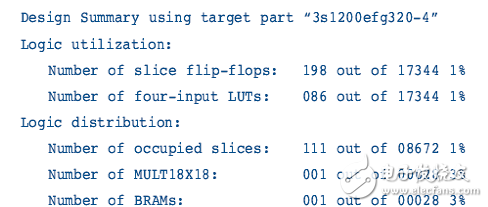

假定我們以Spartan-3E 1200(fg320-4)為目標器件,現使用ISE設計套件和System Generator for DSP 10.1 SP3版工具對其進行布局和布線,結果其所占用的FPGA資源的總體情況如下:

?

該設計完全流水線作業,可以在任何一個時鐘周期提供新的輸出。時延為10個時鐘周期,最大數據速率達194.70MSPS(每秒百萬采樣數)。從數值精度來說,對1000或2000字ILUT而言,參考浮點結果與System Generator forDSP定點輸出的量化誤差之間的比值,即信噪比分別為 71.94dB或77.95dB。

除ILUT外,我們還可應用賽靈思System Generator for DSP提供的Reference MathBlockset(參考數學模塊組)中的CORDIC SQRT模塊。在本例中,總時延為37個時鐘周期,最大數據速率達115.18MSPS,區域資源占用為940片觸發器,總共有885個四輸入LUT,560個占用的芯片以及兩個MULT18x18嵌入式乘法器。信噪比為40.64dB。這些結果顯示CORDIC是實施定點數學運算的理想方法,但ILUT在許多方面更加出色。

線性化非線性傳感器

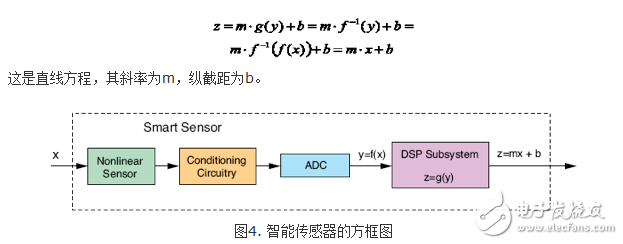

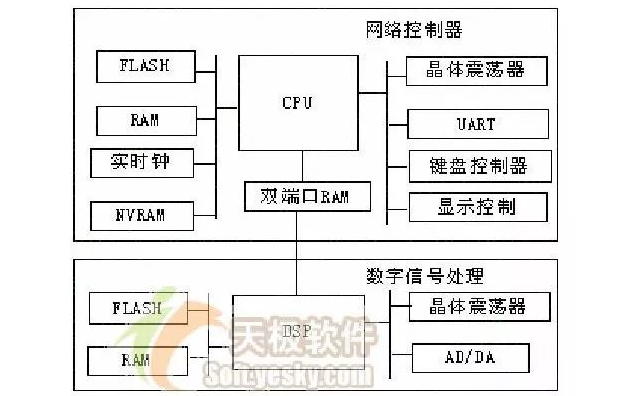

目前許多企業在工業控制系統中使用“智能傳感器”,以滿足低占用面積、低功耗、高性能、最低成本以及最短開發時間等要求。通用智能傳感器可視為一個由傳感器及其信號控制線路、模數轉換器 (ADC)、帶或不帶嵌入式處理器的相關DSP子系統組成的功能組件,所有這些功能塊都集成在的同一器件上,如圖4所示。

智能傳感器的目的是將物理量(如電機中的電流)轉化為數字電路能夠處理的數字信號。構建這類傳感器所采用的技術及組件的某些特性通常會導致諸如失調、增益和非線性等誤差,進而導致總體傳遞函數呈非線性。

一般來說,客戶會校正他們產品中運行的DSP子系統所出現的上述誤差。如果 y=f(x) 是來自傳感器和ADC級聯的數字輸出信號,那么DSP必須執行其反函數g(y)=f-1(y) 來補償非線性函數,這樣總體輸出z即為:

最簡單的線性化方法是LUT法,采用存儲在ROM中的傳感器校準點。不過,對16位的ADC來說,ROM顯得過大了,且需要64個BRAM單元。而內插LUT則不然,是一個良好的解決方案。

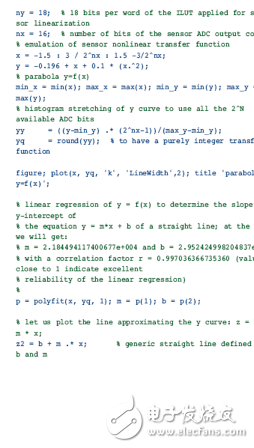

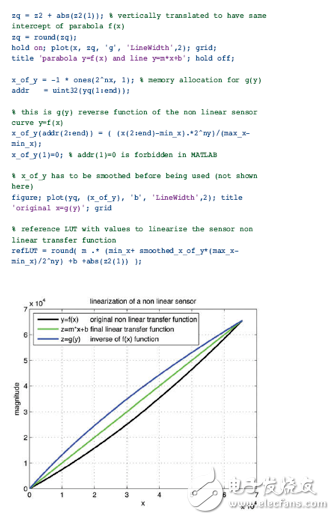

舉例來說,我們假定非線性傳遞函數是一條拋物線。下一 MATLAB分段碼說明了如何生成最終直線的m和b參數,以及如何計算 g(y)(即f(x) 的反函數)。圖5用三種顏色顯示了三條不同曲線。請注意在計算 f(x) 的反函數 g(y)過程中會丟失一些值。這是因為有幾個y值相同的點對應著不同的x點。因此,需要對 g(y)進行平滑化,填補所有缺失的點。(為精確起見,我沒有把這部分運算包括在MATLAB分段碼中)

?

圖5.黑色拋物線表示非線性傳感器傳遞函數f(x) 的曲線;綠色直線表示線性化DSP子系統獲得的最終線性傳感器傳遞函數曲線;藍色拋物線則表示反函數g(y) 的曲線。

我采用非常類似于圖1-3的設計,在System Generator for DSP中運行基于定點周期的仿真,在非線性傳感器的總體輸出范圍內得到了92.48dB的信噪比。

斑點噪聲消除

跟蹤高速運動系統的目標物體(比如導彈)是一項極富挑戰性的工作,需要非常復雜的DSP算法以及諸如合成孔徑雷達 (SAR)等各種不同類型的探測介質。作為典型的相干電磁源(如激光),SAR成像器件也受斑點噪聲的影響。因此,任何基于SAR的DSP鏈的第一級都是二維(2D)自適應FIR濾波器,用以降低這種噪聲(但不可能完全消除)。圖6顯示了斑點噪聲的MATLAB仿真。該噪音對左邊圖像的畫質造成了綜合性的不良影響。右邊的圖像是2D FIR濾波器黃金模型的輸出結果。

?

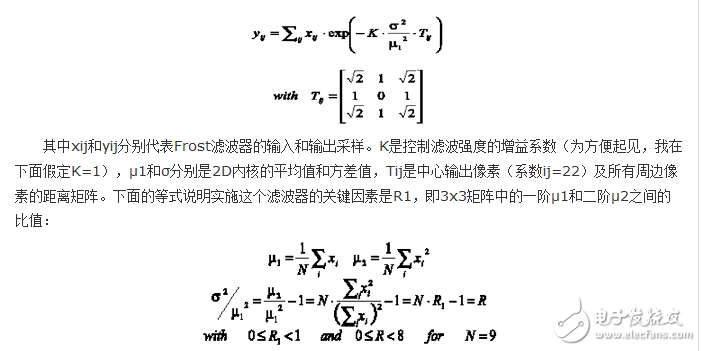

斑點噪聲是一種倍增噪聲,呈指數分布,完全由其方差值σ決定。因此,廣泛使用的抗斑點噪聲的方法就是Frost濾波器(由發明者V.S.Frost的名字命名而來)。V.S.Frost在1981年發表的論文對這個現象進行了探討。在一個3x3的矩陣中,可以用下列公式進行建模:

?

?

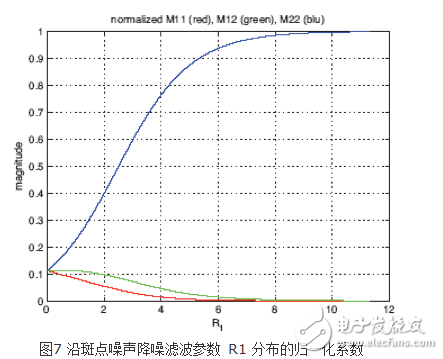

R1的取值范圍在0和1之間。根據實驗發現要取得良好的數值精度,R1可以使用16位至20位二進制數來表示。

我在system Generator for DSP中設計R1計算步驟后,我決定通過內插LUT來實施濾波系數的歸一化。LUT的內容以下列MATLAB代碼表示:

圖7顯示的是歸一化后的系數沿R1輸入信號分布的曲線。這里只有三條曲線,因為 Tij矩陣在系數ij=22的中心像素周圍呈對稱分布。根據曲線,與純浮點參考模型相比,數值結果顯示信噪比介于81.28至83.38dB之間。對有興趣的讀者,下面的MATLAB分段碼說明了2D濾波器的處理過程(為簡便起見,沒有包括ILUT函數)。

?

簡言之,這些例子說明插值查找表是實施賽靈思FPGA的DSP功能的簡便而強大的方法。插值查找表可幫助您在保持面積占用相對較低的情況下實現極高數值精度 (SNR) 和高數據速率。

?

電子發燒友App

電子發燒友App

評論