引言

從20世紀80年代初到90年代初的10年里,微電子領域的很多研究工作都集中到了數字系統速度的提高上,現如今的技術擁有的計算能力能夠使強大的個人工作站、復雜實時語音和圖像識別的多媒體計算機的實現成為可能。高速的計算能力對于百姓大眾來說是觸指可及的,不像早些年代那樣只為少數人服務。另外,用戶希望在任何地方都能訪問到這種計算能力,而不是被一個有線的物理網絡所束縛。便攜能力對產品的尺寸、重量和功耗加上嚴格的要求。由于傳統的鎳鉻電池每磅僅能提供20W.h的能量,因而功耗就變得尤為重要。電池技術正在改進,每5年最大能將電池的性能提高30%,然而其不可能在短期內顯著地解決現在正遇到的功耗問題。

雖然傳統可便攜數字應用的支柱技術已經成功地用于低功耗、低性能的產品上,諸如電子手表、袖珍計算器等等,但是有很多低功耗、高性能可便攜的應用一直在增長。例如,筆記本計算機就代表了計算機工業里增長最快的部分。它們要求與桌上計算機一樣具有同樣的計算能力。同樣的要求在個人通信領域也正在迅速地發展,如采用了復雜語音編解碼算法和無線電調制解調器的帶袖珍通信終端的新一代數字蜂窩網。已提出的未來個人通信服務PCS(Personal Communication Services)應用對這些要求尤其明顯,通用可便攜多媒體服務是要支持完整的數字語音和圖像辨別處理的。在這些應用中,不僅語音,而且數據也要能在無線鏈路上傳輸。這就為實現任何人在任何地方的任何時間開展任何想要的業務提供了可能。但是,花在對語音、圖像的壓縮和解壓上的功耗就必須附加在這些可便攜的終端上。確實,可便攜能力已經不再明顯地和低性能聯系在一起了;相反,高性能且可便攜的應用正在逐步得到實現。

當功率可以在非便攜環境中獲得時,低功耗設計的***也變得十分關鍵。直到現在,由于大的封裝、散熱片和風扇能夠輕而易舉地散掉芯片和系統所產生的熱,其功耗還未引起多大的重視。然而,隨著芯片和系統尺寸持續地增加,要提供充分的散熱能力就必須付出重要代價,或使所提供的總體功能達到極限時,設計高性能、低功耗數字系統方法的需求就會變得更為顯著。幸好,現在已經發展了許多技術來克服這些矛盾。

由于可以高度集成,并具有低功耗、輸入電流小、連接方便和具有比例性等性質,CMOS邏輯電路被認為是現今最通用的大規模集成電路技術。下面研究CMOS集成電路的功耗組成,概述實現集成電路——SoC(System on Chip)系統的低功耗設計的諸多方法。目的在于揭示當今電子系統結構復雜度、速度和其功耗的內在聯系,在及在數字電子系統設計方向上潛在的啟示。

1 CMOS集成電路功耗的物理源

要研究SoC的低功耗設計,首先要物理層次上弄清該集成電路的功耗組成,其次,才能從物理實現到系統實現上采用各種方法來節省功耗,達到低功耗設計的目的。圖1為典型CMOS數字電路的功耗物理組成。

(1)動態功耗

![]()

動態功耗是由電路中的電容引起的。設C為CMOS電路的電容,電容值為PMOS管從0狀態到H狀態所需的電壓與電量的比值。以一個反相器為例,當該電壓為Vdd時,從0到H狀態變化(輸入端)所需要的能量是CVdd2。其中一半的能量存儲在電容之中,另一半的能量擴展在PMOS之中。對于輸出端來說,它從H到0過程中,不需要Vdd的充電,但是在NMOS下拉的過程中,會把電容存儲的另一半能量消耗掉。如果CMOS在每次時鐘變化時都變化一次,則所耗的功率就是CBdd2f,但并不是在每個時鐘跳變過程之中,所有的CMOS電容都會進行一次轉換(除了時鐘緩沖器),所以最后要再加上一個概率因子a。電路活動因子a代表的是,在平均時間內,一個節點之中,每個時鐘周期之內,這個節點所變化的幾率。最終得到的功耗表達式為:Psw=aCVdd2f。

(2)內部短路功耗

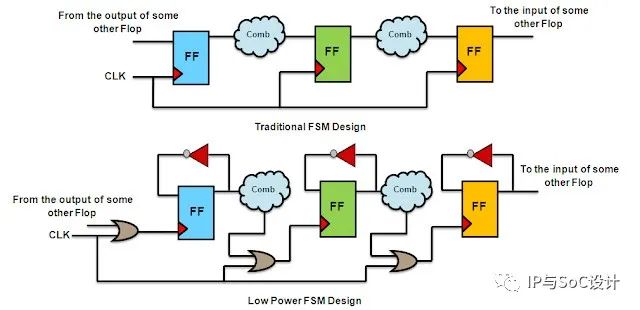

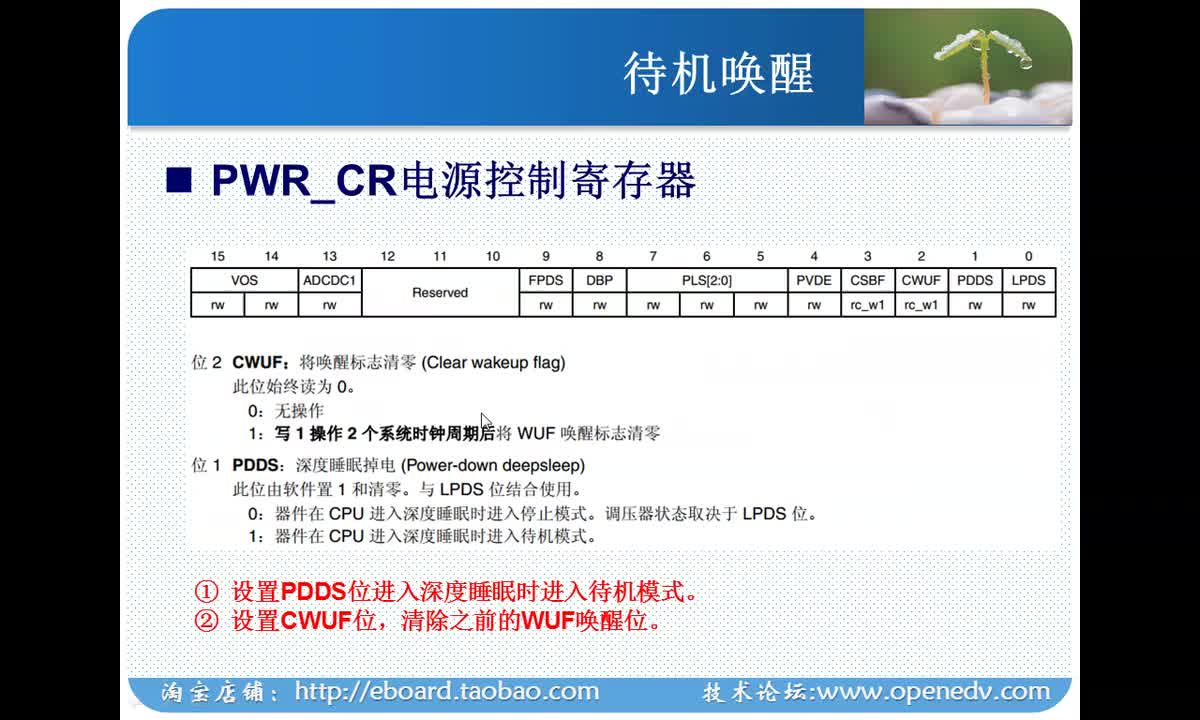

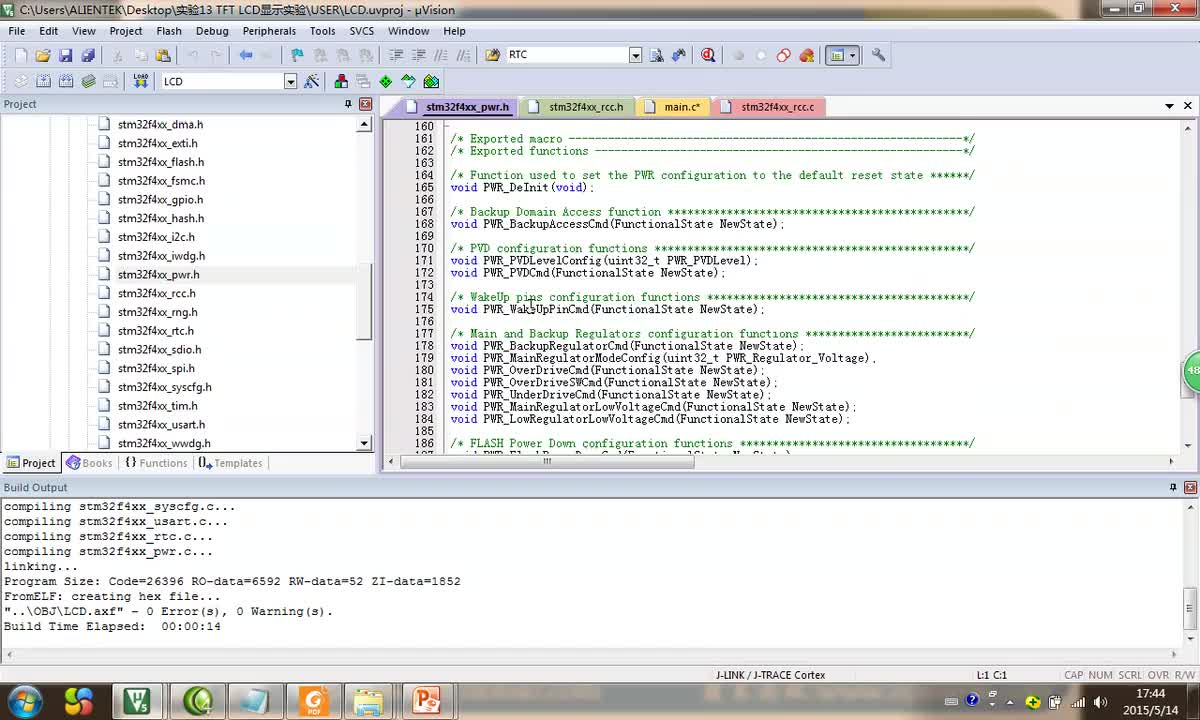

CMOS電路中,如果條件Vtn 一般來說,內部短路電流功耗不會超過動態功耗的10%。而且,如果在一個節點上,Vdd (3)靜態漏電功耗 靜態漏電掉的是二極管在反向加電時,晶體管內出現的漏電現象。在MOS管中,主要指的是從襯底的注入效應和亞門限效應。這些與工藝有關,而且漏電所造成的功耗很小,不是考慮的重點。 表1為CMOS集成電路中主要的耗電類型。 (4)小結 通過設計工藝技術的改善,Pint和Pleak能被減小到可以忽略的程度,因而Psw也就成為功耗的主要因素。后面所做的功耗優化大部分是圍繞這一個公式來進行的。對于SoC來說,所有的方法都是圍繞著動態功耗來做文章的,因為在電路信號變化時,功耗消耗主要在電路中電容的充放電過程。如果從各個層次、各個方面盡量減少電路的充放電,將是我們關心的主題。 2 降低集成電路SoC功耗的方法 功耗對于一個便攜式SoC數字系統來說尤為重要。事實上,很多便攜式SoC系統的設計,是先進行功耗分析,由功耗分析的結果再來劃分設計結構。可以說,功耗將可能決定一切。現在要做的是,根據功耗分析的結果,評判SoC結構,改進設計,優化方案。 SoC系統的功耗所涉及的內容十分廣泛,從物理實現到系統實現都可以采用各種方法來節省和優化功耗。通過對國外大量文獻的查閱,我們得到了常用的實現低功耗設計的各種較為有效的方法,如表2所列。 (1)系統級功耗管理 這一部分實際上是動態功耗管理。主要做法是在沒有操作的時候(也就是在SoC處于空閑狀態的時候),使SoC運作于睡眠狀態(只有部分設備處于工作之中);在預設時間來臨的時候,會產生一個中斷。由這個中斷喚醒其它設備。實際上,這一部分需要硬件的支持,如判斷,周期性的開、關門控時鐘(gate clock)等。 (2)軟件代碼優化 軟件代碼優化是針對ARM嵌入式處理器而言的。對于編譯器來說,所起的使用不到1%,而對于代碼的優化則可以產生高達90%的功耗節省。Simunic等人曾分別做過用各種針對ARM處理器的編譯器進行的試驗。比此的實驗結果發展,風格比較好的代碼產生的效果遠比用ARM編譯器優化的效果好。 (3)Clock控制 這是在ASIC設計中行之有效的方法之一。如果SoC芯片在正常工作,有很大一部分模塊(它們可能是用于一些特殊用途中,如調試Debug、程序下載等)是乖于空閑狀態的,這些器件的空運作會產生相當大的功耗。這一部分應使用時鐘控制,即clock enable & disable。 (4)RTL級代碼優化 與軟件相似,不同的RTL(Register Transfer Level,寄存器傳輸級)代碼,也會產生不同的功耗,而且RTL代碼的影響比軟件代碼產生的影響可能還要大。因為,RTL代碼最終會實現為電路。電路的風格和結構會對功耗產生相當重要的影響。 RTL級代碼優化主要包括: ①對于CPU來說,有效的標準功耗管理有睡眠模式和部分未工作模塊掉電。 ②硬件結構的優化包括能降低工作電壓Vdd的并行處理、流水線處理以及二者的混合處理。 ③降低寄存電容C的片內存儲器memory模塊劃分。 ④降低活動因子a的信號門控、減少glitch(毛刺)的傳播長度、Glitch活動最小化、FSM(有限狀態機)狀態譯碼的優化等。 ⑤由硬件實現的算法級的功耗優化有:流水線和并行處理、Retiming(時序重定)、Unfolding(程序或算法的展開)、Folding(程序或算法的折疊)等等基本方法以及其組合。 (5)后端綜合與布線優化 既然SoC的功耗與寄生電容的充放電有很大的關系,作為后端綜合與布線,同樣也可采取一些措施來減少寄存器電容。可以優化電路,減少操作(電路的操作),選擇節能的單元庫,修改信號的相關關系,再次綜合減少毛刺的產生概率。 (6)功耗的精確計算 后端綜合與布線工具不但可以根據基本單元提供的功耗參數進行優化,還可以根據這些參數估算出整個SoC的功耗。正因為有這樣一些工具,使我們可以精確地知道我們所設計的是否達到設計要求。萬一設計功耗不符合總體要求,則可能要求從系統級到物理綜合布線都要做出檢查與分析,做出可能的改進,盡可能地減少功耗以達到設計要求。 (7)小結 從上面的各種降低以及估算功耗的方法可以看出,SoC系統的拉耗優化涉及到從物理實現到系統實現的方方面面,是芯片設計中一個十足的系統工程。可以說,功耗可以決定一切。 結語 本文首先分析了CMOS集成電路的功耗物理組成,得到了其主要功耗成分。其次,以該主要功耗成分數學表達式為指導,突出了SoC低功耗設計的各種級別層次的不同方法。不管是現在還是將來,該領域的重要性將會日益顯著。在下面的一些發展方向還將會有較大的發展: ①實現SoC系統設計的變換以及映射技術的進一步探索。 ②將各種低功耗設計手段按照各性質最佳綜合起來,以便使用基于人工智能的技術(如遺傳算法和啟發式算法等等)來研究。 ③發展以實現低功耗為目的CPU指令程序的改寫技術,以將其擴展到復雜SoC系統的設計中。 ④進一步研究應用于SoC低功耗設計的編碼和信號表示技術。 ⑤擴展功耗估算模型的數量以覆蓋所有的SoC系統模式,等等。 隨著便攜式和移動計算要求的進一步增長,集成電路—SoC的低功耗設計將變成一個越來越重要且必須面臨的問題。它對開發新型電子產品,其意義重大。 相關推薦

表1 CMOS集成電路中主要的耗電類型類 型 公 式 比 率 動態功耗(switching power) Psw=aCVdd2f 70%~90% 內部短路功耗(internal short-circuit power) Pint=IintVdd 10%~30% 靜態漏電功耗(static leakage power) Pleak=IleakVdd <1% 總功耗(total power) Ptotal=Psw+Pint+Pleak 100%

表2 常用實現低功耗的各種方法類 型 采用方法 效 果 行為級(系統級) Concurrency memor 幾倍 軟件代碼 軟件優化 32.3% 功率管理 Clock控制 10%~90% RTL級 結構變換 10%~15% 綜合技術 合成與分解邏輯 15% 綜合技術 映射

門級優化20%

20%布局 布局優化 20%

實際上,這一部分與使用的工具有關。與軟件部分有相同之處,后端綜合與布線同軟件的編譯差不多。軟件編譯的結果是產生可執行的機器代碼;而RTL的綜合與布線是把RTL代碼編譯成真實的電路。但是,后端綜合與布線優化比較編譯優化有更好的效果。這是因為一段RTL代碼所對應的電路是可以有多種形式的;同時現有些編譯器會根據設計者提供的波形,智能地修改電路(前提是最終電路的效果還是一樣的),編譯器就會進行相關的優化。但是后端綜合的優化與RTL級代碼優化和時鐘控制相比,同樣的RTL級與時鐘優化所產生的影響要遠大于用編譯工具所產生的影響。

藍牙低功耗市場戰火熱 眾大廠爭推SoC方案

1084

1084Arm SoC芯片低功耗設計分享會在深圳成功舉辦

1369

1369SOC芯片供電系統簡介

SoC設計中的功耗管理問題

低功耗嵌入式系統該怎么設計?

低功耗電路設計方法

低功耗藍牙怎么低功耗?如何界定

低功耗藍牙的應用領域

系統進入低功耗模式的系統時鐘是什么?

AD,低功耗

ARM超低功耗實體IP對MCU發展有什么影響

Clouder:基于超低功耗SOC芯片的智能手表Turn Key解決方案

NORDIC最新推出ARM內核低功耗藍牙SOC芯片及ARM內核ANT+SOC芯片

PAN1020藍牙低功耗SoC收發器

SI3262—高度集成的低功耗SOC芯片

TI推出最新藍牙低功耗片上系統CC2541,可將功耗銳降33%

nRF52832 SoC低功耗藍牙芯片

《SoC底層軟件低功耗系統設計與實現》基于Linux專門講解軟件低功耗框架和設計的書籍

《SoC底層軟件低功耗系統設計與實現》閱讀筆記

【書籍評測活動NO.19】 SoC底層軟件低功耗系統設計與實現

【啟芯】低功耗視頻解析

什么是nRF52840低功耗藍牙技術?

什么是嵌入式系統面向低功耗的協同設計系統?

便攜式設備低功耗MCU系統設計方法

動態時鐘配置下的SoC低功耗管理 電子資料

單片機低功耗如何減低整個系統功耗?

在低功耗Bluetooth? PEPS系統中添加CAN節點

在低功耗時產生線程調度能喚醒低功耗嗎?

基于FPGA實現低功耗系統設計

基于Foundation IP的低功耗IoT SoC實現

基于Kemet PL-N823-01和OnSemi RSL10藍牙低功耗SoC

處理器在低功耗物聯網應用面臨什么挑戰?

如何使具備藍牙低功耗技術功能的設備真正的具備低功耗?

如何在低功耗Bluetooth? PEPS系統中添加CAN節點

如何設計超低功耗的嵌入式應用?

如何選擇超低功耗MCU

對功耗、散熱和電池壽命敏感的片上系統 (SoC) 設計

嵌入式系統中的低功耗設計

無線數據傳輸系統的低功耗怎么實現?

最新SOC低功耗帶學習碼接收方案

設計超低功耗的嵌入式應用

超低功耗LoRa集成的LPWAN應用的單芯片SoC - ASR6501

超低功耗的嵌入式應用的實現:降低系統中電池功耗

低功耗藍牙4.2 SoC

嵌入式系統面向低功耗的協同設計

12

12SoC 系統的低功耗設計

14

14高性能低功耗的SOC平臺體系結構

14

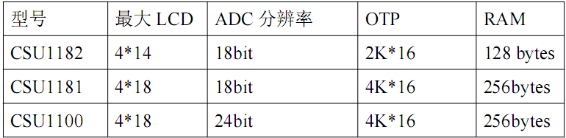

14芯海科技最新推出CSU11xx系列超低功耗衡器SoC芯片

1000

1000

芯海科技開發出低功耗SoC衡器計量芯片

1059

1059德州儀器(TI)推出CC2541藍牙低功耗片上系統(SoC)

2173

2173nRF51822:藍牙低功耗和2.4GHz專利SoC簡介

9173

9173

SoC中的低功耗RF設計

232

232 SoC中的低功耗RF設計

191

191SoC中的低功耗RF設計解析

1403

1403SoC低功耗管理

1

1SoC的低功耗設計

1

1高通推低功耗藍牙SoC 帶給藍牙耳機超長續航

1602

1602BlueNRG-1藍牙低功耗系統級芯片(SoC)

11234

11234

C1110FX和C1111FX低功耗片上系統(SOC)設計的低功耗無線應用概述

5

5CC2541藍牙低功耗芯片片上系統(SOC)解決方案數據手冊免費下載

15

15Nordic Semiconductor獲得授權許可,在低功耗蜂窩物聯網SoC中部署使用CEVA DSP IP

304

304使用低功耗SoC實現微型圖像采集系統設計的詳細資料說明

0

0如何選擇低功耗藍牙SoC

4358

4358

SOC低功耗電路設計方法

1

1低功耗設計

18

18EB5REB1國產低功耗BLE5.0藍牙SOC芯片

610

610FSMs低功耗設計

309

309

瑞薩電子推出新款低功耗藍牙SoC DA14592

322

322瑞薩推出其首款集成閃存的雙核低功耗藍牙SoC

586

586

電子發燒友App

電子發燒友App

評論