采用FPGA實現(xiàn)四階IIR數(shù)字濾波器,通過兩個二階節(jié)級聯(lián)構(gòu)成數(shù)字橢圓低通濾波器。通帶內(nèi)波紋小于0.1dB,阻帶衰減大于32dB。

2014-12-23 10:27:57 1673

1673

Molex 宣布收購 BittWare, Inc.,后者是一家全球領(lǐng)先的計算系統(tǒng)的提供商,專業(yè)提供現(xiàn)場可編程門陣列 (FPGA),產(chǎn)品可部署在數(shù)據(jù)中心的計算應(yīng)用以及網(wǎng)絡(luò)數(shù)據(jù)包的處理應(yīng)用中。

2018-05-29 10:29:03 6949

6949 嗨,我使用的是virtex 5 FPGA。我正在運行外部10Mhz時鐘信號來運行二進制計數(shù)器。當我嘗試使用DCM時,它表示最低頻率為32MHz。可以將此信號運行到FPGA的i / o輸入并通過全局

2019-02-21 10:32:51

自行設(shè)計,所以對于后續(xù)開發(fā) 本店也會可與大力的支持與幫助。 目前小店只有6排針 (4i/o口) 不過馬上即將 4排針(2i/o口)支持I2C 通信的OLED 就會在本店上架,價格和之前是一樣

2013-11-04 19:37:36

的方法是擴展一片8251 或 8250 通用同步/異步接收發(fā)送芯片(USART),需額外占用單片機I/O 資源。本文介紹一種用單片機普通I/O 口實現(xiàn)串行通信的方法,可在單片機的最小應(yīng)用系統(tǒng)中實現(xiàn)與兩個

2012-06-07 15:17:42

萊迪思半導(dǎo)體公司CPU 、ASIC和存儲器的設(shè)計者為了使器件擁有盡可能高的通信帶寬,他們在設(shè)計過程中充分利用I/O單元中的每一個晶體管來達到這個目標。這些器件常與FPGA相連接。因此,FPGA

2018-11-26 11:17:24

本帖最后由 eehome 于 2013-1-5 09:57 編輯

FPGA實現(xiàn)I2C總線的通信接口的基本原理介紹采用ALTERA公司的可編程器件,實現(xiàn)I2C總線的通信接口的基本原理;給出部分

2012-08-11 17:57:48

新人求助,FPGA如何采用I2S與ARM通信?

2016-06-13 11:24:12

并行處理的方式被普遍采用,它們共享總線以互相映射存儲空間,如果再與FPGA通過總線連接,勢必導(dǎo)致FPGA與DSP的總線競爭。同時采用總線方式與FPGA通信,DSP的地址、數(shù)據(jù)線引腳很多,占用FPGA的I

2018-12-04 10:39:29

并行處理的方式被普遍采用,它們共享總線以互相映射存儲空間,如果再與FPGA通過總線連接,勢必導(dǎo)致FPGA與DSP的總線競爭。同時采用總線方式與FPGA通信,DSP的地址、數(shù)據(jù)線引腳很多,占用FPGA的I

2019-06-19 05:00:08

他CPU系統(tǒng)之間的數(shù)據(jù)通信提到日程上,得到人們的急切關(guān)注。本文介紹利用VHDL語言實現(xiàn) FPGA與單片機的串口異步通信電路。整個設(shè)計采用模塊化的設(shè)計思想,可分為四個模塊:FPGA數(shù)據(jù)發(fā)送模塊,FPGA

2011-11-24 16:10:01

FPGA中的I_O時序優(yōu)化設(shè)計在數(shù)字系統(tǒng)的同步接口設(shè)計中, 可編程邏輯器件的輸入輸出往往需要和周圍新片對接,此時IPO接口的時序問題顯得尤為重要。介紹了幾種FPGA中的IPO時序優(yōu)化設(shè)計的方案, 切實有效的解決了IPO接口中的時序同步問題。

2012-08-12 11:57:59

更快、更大,每比特的功耗也更低,但是如何實現(xiàn)FPGA和DDR3 SDRAM DIMM條的接口設(shè)計呢? 關(guān)鍵字:均衡(leveling)如果FPGA I/O結(jié)構(gòu)中沒有包含均衡功能,那么它與DDR3

2019-04-22 07:00:08

。(4)從串模式理解了從并模式,從串模式就不用很多解釋了,它的特點就是節(jié)約FPGA管腳I/O。(5)多片級聯(lián)多片模式有兩種,一種是采用菊花鏈的思想,多片FPGA共享一個存儲器,另外一個是可以使用其他存儲器

2017-11-22 09:35:19

,輸入和輸出。它實現(xiàn)了用戶邏輯。互連提供邏輯塊之間的方向以實現(xiàn)用戶邏輯。根據(jù)邏輯,開關(guān)矩陣提供互連之間的切換。用于外部世界的I / O墊與不同的應(yīng)用程序通信。邏輯塊包含 MUX(多路復(fù)用器),D觸發(fā)器

2018-12-14 17:39:44

外設(shè)電路(I/O應(yīng)用)本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計實戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCttFPGA器件擁有著豐富的I/O資源,它

2019-04-12 06:35:33

FPGA的I/O結(jié)構(gòu)的發(fā)展的怎么樣了?

2021-04-29 06:12:52

行,速度快。Xilinx Spartan-7 FPGA器件適用于那些成本敏感型應(yīng)用。它采用小型封裝卻擁有高比例的I/O數(shù)量,單位功耗性價比相較前代產(chǎn)品提升多達四倍,可提供靈活的連接能力、接口橋接和輔助芯片

2018-08-02 09:37:08

這里寫目錄標題I/O端口原理單片機知識點補充實戰(zhàn)1——閃爍LED指示燈I/O端口原理I/O英文全稱是 Input/Output,即輸入/輸出。單片機端口是標準雙向口,就是說,單片機的端口既可以

2022-01-20 07:55:51

` 本帖最后由 eehome 于 2013-1-5 09:57 編輯

概述:C2000 MD88為8路干接點數(shù)字量輸入和8路數(shù)字量輸出設(shè)備.可以通過RS485實現(xiàn)對遠程開關(guān)量數(shù)據(jù)的采集.通信

2012-06-13 16:17:09

如下優(yōu)越性:(1)高性能ACEX 1K器件采用查找表(LUT)和EAB(嵌入式陣列塊)相結(jié)合的結(jié)構(gòu)形式,可實現(xiàn)復(fù)雜邏輯功能和存儲器功能,如通信應(yīng)用中的DSP、多通道數(shù)據(jù)處理、數(shù)據(jù)傳遞和微控制等。(2

2019-06-18 06:05:34

1. 為什么要使用FPGA實現(xiàn)在全控型電力電子開關(guān)器件出現(xiàn)以后,為了改善交流電動機變壓變頻調(diào)速系統(tǒng)的性能,科技工作者在20世紀80年代開發(fā)出了應(yīng)用脈寬調(diào)制(PWM)技術(shù)的變壓變頻器,由于它的優(yōu)良

2022-01-20 09:34:26

CAS。我們的設(shè)計(圖1)采用Altera公司Cyclone III系列型號為EP3C16F484C6N的FPGA作為控制器,以Micron公司生產(chǎn)的型號為MT47H16M16BG-5E(16M

2019-05-31 05:00:05

USB數(shù)據(jù)與并行I/O口數(shù)據(jù)的交換緩沖區(qū)。FIFO實現(xiàn)與外界(微控制器、FPGA或其它器件)的接口,主要通過8根數(shù)據(jù)線D0~D7、讀寫控制線RD#和WR#以及FIFO發(fā)送緩沖區(qū)空標志TXE#和FIFO接收

2019-04-22 07:00:07

USB數(shù)據(jù)與并行I/O口數(shù)據(jù)的交換緩沖區(qū)。FIFO實現(xiàn)與外界(微控制器、FPGA或其它器件)的接口,主要通過8根數(shù)據(jù)線D0~D7、讀寫控制線RD#和WR#以及FIFO發(fā)送緩沖區(qū)空標志TXE#和FIFO接收

2019-04-26 07:00:12

使用LabVIEW FPGA 模塊和可重新配置I/O 設(shè)備開發(fā)測量與控制應(yīng)用通過使用LabVIEW FPGA 模塊和可重新配置I/O(RIO)硬件,NI 為您提供了一種直觀可用的解決方案,它可以將

2009-07-23 08:15:57

效地減小磁性輻射。數(shù)據(jù)傳送解決方案LpLVDS和CTL只提供針對LCD、相機成像器以及基帶處理器之間接口的I/O解決方案。只有在采用某些并行至串行數(shù)據(jù)傳送方案時,兩者才能發(fā)揮其強大功能。借著鎖相環(huán)路

2019-05-27 05:00:06

使用增強FEC(EFEC),必須采用專用算法進行設(shè)計才能確保最大限度的發(fā)揮光帶寬優(yōu)勢。由于其優(yōu)異的架構(gòu)性能,StratixIVFPGA能夠處理EFEC功能,是OTN系統(tǒng)算法實現(xiàn)和測試的理想平臺。圖6顯示了

2011-07-13 14:36:03

MSP連接到同一存儲區(qū)的用戶I / O引腳。由于某種原因,與ADC的數(shù)字化數(shù)據(jù)引腳接口的FPGA的一些用戶I / O引腳被損壞。我們已經(jīng)生產(chǎn)了6塊FPGA板,所有這些板都在相同的引腳上出現(xiàn)問題。我已經(jīng)

2020-04-07 12:26:15

嗨, 我想把晶體振蕩器的CLK帶到FPGA里面的數(shù)字設(shè)計。該CLK連接到FPGA的I / O引腳。如果我在映射中運行Impliment設(shè)計,我將得到錯誤。所以我將在UCF文件中將網(wǎng)名命名如下。NET

2019-01-29 10:05:43

大家好,我現(xiàn)在在畫一塊28335的板子,想實現(xiàn)與FPGA之間的通信,但是不知道該怎樣設(shè)計,包括FPGA與DSP連接的引腳、通過內(nèi)部什么模塊實現(xiàn)數(shù)據(jù)通信,現(xiàn)在一頭霧水,請大家?guī)兔ΑVx謝。

2018-12-03 15:55:34

I/O接口的功能是負責實現(xiàn)CPU通過系統(tǒng)總線把I/O電路和外圍設(shè)備聯(lián)系在一起,按照電路和設(shè)備的復(fù)雜程度,I/O接口的硬件主要分為兩大類: (1)I/O接口芯片 這些芯片大都是集成電路,通過CPU輸入

2015-11-04 11:39:47

測溫度用符號擴展的16位數(shù)字量方式串行輸出。一線式(1-WIRE)串行總線是利用1條信號線就可以與總線上若干器件進行通信。具體應(yīng)用中可以利用微處理器的I/O端口對DS18B20直接進行通信,也可以通過

2020-04-28 07:37:31

范圍- 45℃~+85℃。功能簡介YL95 遠程I/O模塊,可以用來測量五路開關(guān)量信號,并有五路繼電器輸出。1、 開關(guān)量信號輸入與輸出5路開關(guān)量信號輸入,可接干接點和濕接點,詳細請參考接線圖部分;五路

2022-04-19 09:32:31

與FPGA的接口電路設(shè)計2.1 硬件設(shè)計系統(tǒng)中的FPGA輸入時鐘由外部晶振提供,為20MHz。FPGA的復(fù)位信號通過SEP3203的I/O口實現(xiàn)。本系統(tǒng)有2個觸發(fā)信號:硬件觸發(fā)信號和軟件觸發(fā)信號。硬件觸發(fā)

2019-04-26 07:00:06

labview怎么實現(xiàn)像plc一樣的通過輸入輸出I/O量,控制開關(guān)量,比如通過I/O點控制繼電器的吸合。怎么給I/O量分配地址,怎么在程序里使用這些變量實現(xiàn)一系列有序的動作。希望能附上一份樣例程序,讓小弟學(xué)習(xí)領(lǐng)會,請多指教,謝謝。

2016-04-25 00:51:33

i2c_master_bit_ctrl.v 完成位傳輸?shù)墓δ堋N粋鬏數(shù)墓δ馨〝?shù)據(jù)按位傳輸?shù)?b class="flag-6" style="color: red">實現(xiàn)和I2C協(xié)議各個命令的實現(xiàn)兩部分。如圖 4-5 所示開始和重復(fù)開始命令的產(chǎn)生包括 5 個階段:idle

2018-10-09 11:43:44

本帖最后由 eehome 于 2013-1-5 10:10 編輯

本節(jié)將重點講解,用FPGA實現(xiàn)按鍵去抖的方法,在以往的按鍵去抖中,大部分采用的是單片機去抖方法。這里我們將介紹FPGA的實現(xiàn)

2012-03-19 14:48:40

- 2.5VVCCO_35 - 2.5V連接到I / O bank的一些外部電路在2.5V FPGA電源軌之前上電(這超出了我的控制范圍)。這會以奇怪的方式導(dǎo)致2.5V FPGA電源軌斜坡,請參考附圖。基本上2.5VFPGA

2020-07-30 09:51:29

前言此實驗是通過STM32CubeMX來配置stm32實現(xiàn)按鍵輸入,以此來了解stm32I/O的輸入操作及如何使用HAL庫來實現(xiàn)I/O輸入。本實驗中的按鍵操作使用的是軟件中斷,并未用到stm32

2022-03-01 06:58:08

電平 ,輸出高低電平。就是通過這簡單的控制電平來實現(xiàn)大多數(shù)的應(yīng)用控制。1. 什么是 I/O 口?I 表示 IN(輸入),O 表示 OUT(輸出),所以 I/O = 輸入/輸出2. I/O 具體能做什么呢?如果你是剛剛步入電子的新手,那你最好要知道一下I/O口具體能做什么。感性的認識對你的..

2021-11-24 06:47:23

美國國家儀器有限公司(National Instruments,簡稱NI)近日針對PXI平臺,推出了一個全新的、開放式的、基于FPGA的產(chǎn)品系列。NI FlexRIO系列產(chǎn)品是工業(yè)領(lǐng)域首款成熟商用現(xiàn)成產(chǎn)品,它為工程師們提供了同時結(jié)合高速、工業(yè)級I/O和NI LabVIEW FPGA技術(shù)的解決方案。

2019-10-29 07:03:11

UEFI學(xué)習(xí)(四)-SuperIo的訪問一、什么是Super I/O?二、我們要用SuperIo實現(xiàn)什么三、NCT5581D的訪問機制一、什么是Super I/O?Super I/O 芯片也叫 I

2022-01-24 08:12:27

要使用FPGA實現(xiàn)150M的光纖通訊,使用XILINX XAPP244的串行數(shù)據(jù)恢復(fù)功能感覺有些麻煩。使用XILINX的ROCKET I/O 實現(xiàn)150M的光纖通信合適/可行嗎?

2013-03-26 16:06:30

芯片中,因為背板機箱中的可重配置FPGA芯片是在RT系統(tǒng)的控制下提供大量的I/O口用于與可熱插拔的I/O模塊進行通信等功能的,通過這些I/O實現(xiàn)對熱插拔I/O模塊功能的操作控制,如圖1。即

2017-09-23 16:55:58

的功能,而且還可以大大縮短設(shè)計時間,減少PCB的面積,提高信號的傳輸質(zhì)量,提高系統(tǒng)的可靠性,增加設(shè)計的靈活性和可維護性。本文采用FPGA技術(shù)實現(xiàn)一個MCU與串行通信外設(shè)進行簡易通信的平臺,一方面了解了計算機的一些控制原理和工作流程;另一方面可以了解利用FPGA進行電子設(shè)計的優(yōu)越性。

2019-07-08 06:28:38

單片機應(yīng)用系統(tǒng)中,常有用單片機的I/O口來實現(xiàn)自關(guān)機(徹底關(guān)機)的功能。一般用單片機的一個I/O口控制一個電子開關(guān)來實現(xiàn),因單片機關(guān)電后,失去電源,所以在關(guān)機時,實現(xiàn)關(guān)機的IO口的電平必須用低電平

2017-12-14 20:15:53

您好,我在fpga中采用spi通信讀ad9173寄存器時,發(fā)現(xiàn)ad9173沒有響應(yīng)。其中spi通信速率為10M完全滿足datasheet不大于80M的要求。其中通信方式采用四線制。讀取寄存器為

2023-12-01 06:10:50

圖2所示。2.2 總線接口設(shè)計本設(shè)計中采用32bit/33 MHz CPCI總線接口,其傳輸率可達133MB/s,實現(xiàn)了設(shè)備之間的高速通信。通過CPCI連接器,CPCI總線信號與FPGA的I/O口互連

2016-01-14 10:59:18

基于FPGA的光纖通信系統(tǒng)的設(shè)計與實現(xiàn){:soso_e129:}文章下載鏈接:http://www.xsypw.cn/soft/5/2012/20120518272336.html

2012-05-22 22:33:59

于機器視覺、軟件無線電、雷達/聲吶、醫(yī)用儀器、光纜普查儀等。下面進入正題:DSP與FPGA通信需要把開發(fā)板的撥碼開關(guān)第5位撥到1,按照IBL NOR模式啟動開發(fā)板。測試說明:DSP端通過TFTP服務(wù)器加載

2018-10-31 14:27:30

的區(qū)別。每輪選出的第一層簇頭成為第二層簇頭的普通節(jié)點,在LEACH中這些節(jié)點直接與基站通信。由式(1)可以看出,放大器能耗遠大于電路能耗,且放大器能耗中與通信距離d有直接關(guān)系,因此在產(chǎn)生第二層簇頭

2018-11-02 15:19:38

如何采用FPGA實現(xiàn)圖像采集卡的設(shè)計?

2021-04-29 06:45:55

如何采用FPGA實現(xiàn)視頻監(jiān)視?

2021-04-29 06:24:06

。ECP5 FPGA支持與ASIC、ASSP和應(yīng)用處理器實現(xiàn)互連,并具備優(yōu)化的I/O和體系架構(gòu)。增強的嵌入式DSP塊和高度并行的FPGA邏輯架構(gòu)為計算密集型協(xié)處理功能提供了所需的高性能支持。ECP5 FPGA

2020-10-21 11:53:02

如何克服FPGA I/O引腳分配挑戰(zhàn)?

2021-05-06 08:57:22

嵌入式測試是什么?如何用FPGA技術(shù)去實現(xiàn)嵌入式設(shè)計?如何測試FPGA中的高速串行I/O?

2021-04-13 07:03:58

嗨專家,我正在使用Spartan3AN(XC3S50AN)FPGA板和平臺線USB II。你能告訴我如何通過JTAG監(jiān)控PC中FPGA I / O的狀態(tài)嗎?謝謝,V。Prakash以上來自于谷歌翻譯

2019-06-18 09:05:14

趨勢,而 NI FlexRIO 正是重要的下一步。透過可互換的轉(zhuǎn)接器模組,工程師可確實針對 I/O 需求建立解決方案。再整合 LabVIEW FPGA 與 Virtex-5 FPGA 系統(tǒng)的強大架構(gòu),即便是為復(fù)雜的設(shè)計與測試應(yīng)用,NI FlexRIO 亦可提供圖形化系統(tǒng)設(shè)計 (GSD) 的彈性。

2019-04-28 10:04:14

隨著現(xiàn)代技術(shù)的發(fā)展,SPI接口總線已經(jīng)成為了一種標準的接口,由于協(xié)議實現(xiàn)簡單,并且I/O資源占用少,為此SPI總線的應(yīng)用十分廣泛。目前,SPI接口的軟件擴展方法雖然簡單方便,但若用來通信,則速度

2019-08-09 08:14:34

在我的項目中,有兩個Straan3A-DSP FPGA,而這兩個FPGA需要相互通信。由于Spartan3A-DSP沒有Rocket I / O,我使用64位(32位發(fā)送和32位接收)并行數(shù)據(jù)通信

2019-05-24 10:21:47

你好我試圖將1PPS從GPS接收器連接到FPGA I / O引腳之一。我希望FPGA在I / O引腳上看到1pps的上升沿時執(zhí)行一些任務(wù)。我正在使用verilog進行hdl。我沒有在代碼中指出這一點

2019-05-24 08:02:28

數(shù)組,將實數(shù)數(shù)組中大于3的數(shù)刪除,產(chǎn)生一個新的實數(shù)數(shù)組;將復(fù)數(shù)數(shù)組的元素都加1+1i,產(chǎn)生一個新的復(fù)數(shù)數(shù)組;5. 將兩個新的數(shù)組組成一個新的簇。

2016-08-03 11:25:32

of LEACH,多跳LEACH)算法,簇內(nèi)的節(jié)點不是以單跳的方式傳輸數(shù)據(jù)到簇首,而是通過簇內(nèi)其他節(jié)點轉(zhuǎn)發(fā)。參考文獻提出了一個多跳簇首模型,采用從下到上的策略,逐層生成每一層的簇首,最終得到一個多層結(jié)構(gòu)

2018-11-01 15:05:46

大家好,我想檢查FPGA功能和I / O引腳功能在我的主板上使用“Selftest application”。在我的Selftest應(yīng)用程序中,我可以使用哪些方法來檢查這些?請?zhí)峁┮恍┫敕āVx謝

2019-04-01 12:33:26

VIRTEX-6 FPGA的I / O支持的最大數(shù)據(jù)速率是多少?我想在Virtex-6的I / O接收625MSPS的數(shù)據(jù)。這可以實現(xiàn)嗎?

2020-07-13 09:45:20

使用XC7Z020CLG484 FPGA。我使用I / O作為輸入。要在i / o上接收任何消息,該i / o所需的最小灌電流是多少?

2020-05-08 08:48:11

輕松實現(xiàn)高速串行I/OFPGA應(yīng)用設(shè)計者指南輸入/輸出(I/O)在計算機和工業(yè)應(yīng)用中一直扮演著關(guān)鍵角色。但是,隨著信號處理越來越復(fù)雜,I/O通信會變得不可靠。在早期的并行I/O總線中,接口的數(shù)據(jù)對齊

2020-01-02 12:12:28

是整個溫控系統(tǒng)的硬件基礎(chǔ),其中涉及到溫度采集,與微處理器通信,串口輸出,控制數(shù)模轉(zhuǎn)換芯片等多個組成部分。本文提出一種高效實用的FPGA接口設(shè)計,它能夠完成協(xié)調(diào)各個組成部分有序工作,準確、快速實現(xiàn)數(shù)據(jù)傳輸

2020-08-19 09:29:48

FPGA怎么選擇?針對功耗和I/O而優(yōu)化的FPGA介紹

2021-05-06 09:20:34

數(shù)784邏輯元件/單元數(shù)1862總 RAM 位數(shù)25088I/O 數(shù)192柵極數(shù)40000電壓 - 電源3V ~ 3.6V安裝類型表面貼裝型工作溫度0°C ~ 8

2022-04-19 09:45:33

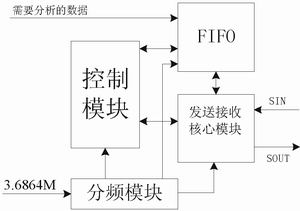

摘 要:本文主要介紹了基于FPGA技術(shù)實現(xiàn)與PC串行通信的過程,給出了各個模塊的具體實現(xiàn)方法,分析了實現(xiàn)結(jié)果,驗證了串行通信的正確性。引言串行通信即

2006-03-24 13:31:51 4660

4660

什么是通信量控制/管理器

通信量控制器CC(Communication Controller):CC是用以對數(shù)據(jù)信息各個階段進行控制的設(shè)備。

2010-03-26 15:52:15 847

847 隨著云計算技術(shù)的發(fā)展,采用FPGA 作為協(xié)同加速成為其發(fā)展的一個趨勢,如何設(shè)計與實現(xiàn)FPGA 片間的高速通信是該研究方向的一個熱點。研究了FPGA 萬兆通信的物理層、MAC 層的實現(xiàn)機制,在通信

2017-11-18 08:13:01 15054

15054

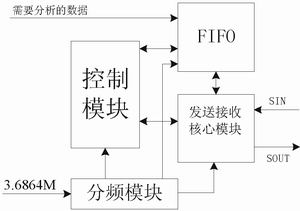

在基于FPGA芯片的工程實踐中,經(jīng)常需要FPGA與上位機或其他處理器進行通信,為此設(shè)計了用于短距離通信的UART接口模塊。該模塊的程序采用VHDL語言編寫,模塊的核心發(fā)送和接收子模塊均采用有限狀態(tài)機

2017-11-18 11:33:01 5152

5152 FPGA diy實現(xiàn)八位撥碼開關(guān)控制8位LED輸出

2018-06-20 14:15:00 8400

8400 FPGA diy作業(yè)實現(xiàn)8位LED花樣燈加撥碼開關(guān)控制

2018-06-20 14:08:00 3965

3965

近日,基于現(xiàn)場可編程門陣列(FPGA)的數(shù)據(jù)加速器件和高性能嵌入式FPGA(eFPGA)半導(dǎo)體知識產(chǎn)權(quán)(IP)領(lǐng)導(dǎo)性企業(yè)Achronix半導(dǎo)體公司,與Molex旗下的一家領(lǐng)先企業(yè)級FPGA加速器產(chǎn)品供應(yīng)商BittWare今日聯(lián)合宣布:推出一類全新的、面向高性能計算和數(shù)據(jù)加速應(yīng)用的FPGA加速卡。

2019-10-31 15:11:33 737

737 Achronix半導(dǎo)體公司與Mo-lex旗下FPGA加速器產(chǎn)品供應(yīng)商BittWare聯(lián)合推出全新的、面向高性能計算和數(shù)據(jù)加速應(yīng)用的FPGA加速卡,可實現(xiàn)云計算與邊緣計算加速,助力高帶寬應(yīng)用。

2019-11-08 15:07:23 562

562 Molex旗下的 BittWare 公司是一家領(lǐng)先的企業(yè)級 FPGA 加速卡產(chǎn)品的供應(yīng)商,產(chǎn)品適合各種高要求的計算、網(wǎng)絡(luò)及存儲應(yīng)用使用,公司宣布已經(jīng)與 Achronix 半導(dǎo)體公司達成戰(zhàn)略協(xié)作關(guān)系

2019-11-19 15:03:11 657

657 4月19日消息,NEC開發(fā)了一種裝置“NEC AI加速器”,可以減少物連網(wǎng)(IoT)中的通信量。7月開始提供使用。

2020-04-20 17:35:47 3251

3251 Molex旗下BittWare 公司是企業(yè)級 FPGA 加速器產(chǎn)品領(lǐng)域一家領(lǐng)先的供應(yīng)商,現(xiàn)推出全新的TeraBox? 200DE邊緣服務(wù)器。TeraBox 服務(wù)器產(chǎn)品系列是專為數(shù)據(jù)中心提供的領(lǐng)先產(chǎn)品

2020-04-21 15:17:32 3471

3471 貿(mào)澤將開售采用英特爾?和Xilinx? FPGA技術(shù)的BittWare高端板卡級解決方案。

2020-10-14 14:44:00 2709

2709 基于FPGA的光纖通信系統(tǒng)的設(shè)計與實現(xiàn)的講解。

2021-05-25 16:26:19 26

26 基于FPGA的無線通信系統(tǒng)設(shè)計與實現(xiàn)

2021-06-16 09:59:29 44

44 Molex莫仕公司旗下的BittWare是致力于邊緣計算和云計算應(yīng)用企業(yè)級加速器的領(lǐng)先供應(yīng)商,宣布擴展其采用IntelAgilex FPGA的IA-系列FPGA加速器。BittWare的IA系列

2021-06-25 17:58:50 3163

3163 BittWare 在之前發(fā)布的 IA-840F 企業(yè)級 FPGA 加速器中添加了兩款基于英特爾 Agilex FPGA 和 SoC FPGA 的新加速器產(chǎn)品(詳見此前報道)。 全新的 IA-420F

2021-06-30 10:48:07 2089

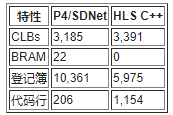

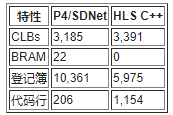

2089 BittWare的SmartNIC Shell和BittWare的Loopback Example的功能之一是一個數(shù)據(jù)包解析器/分類器,它可以從數(shù)據(jù)包中提取協(xié)議字段。通過這篇白皮書,我們不僅要描述我們的Parser,還要解釋如何使用HLS來構(gòu)建和配置它,從而獲得比使用P4語言更好的實現(xiàn)。

2022-08-02 08:03:33 681

681

電子發(fā)燒友App

電子發(fā)燒友App

硬聲App

硬聲App

1673

1673

6949

6949 4660

4660

847

847 15054

15054

5152

5152 8400

8400 3965

3965

737

737 562

562 657

657 3251

3251 3471

3471 2709

2709 26

26 3163

3163 2089

2089 681

681

評論