Quartus II與ModelSim、Synplify Pro等常用EDA工具的開發流程。ALTERA CPLD FPGA設計高級篇:結合作者多年工作經驗,深入地討論了altera fpga

2020-05-14 14:50:30

ALTERA器件選型手冊目錄 1、 MAX7000系列器件 ………………………………………………………………………………………….1 2、 MAX3000A系列器件

2012-08-10 18:24:17

Altera FPGA/CPLD設計與Verilog數字系統設計教程從網上找到了一些Altera FPGA/CPLD經典教材,包含夏宇聞老師的Verilog數字系統設計教程(第2版)Altera FPGA/CPLD設計與Verilog數字系統設計教程

2014-02-17 09:22:18

Altera FPGA/CPLD設計(高級篇)》

2012-12-06 15:51:36

《Altera FPGA_CPLD設計 基礎篇》是Altera官方指定培訓中文教材,說的較為詳細,值得一看。

2013-02-25 17:42:17

Altera FPGA_CPLD設計 高級篇

2023-08-05 18:38:20

可編程邏輯器件相關專輯 Altera-FPGA/CPLD設計,從基礎篇到高級篇由淺入深幫助大家學習

2018-10-08 15:43:55

`` 本帖最后由 yuxuandl 于 2013-5-3 22:10 編輯

Altera FPGA CPLD設計_基礎篇&高級篇兩本書,講解比較精細,適合初學和進階人士學習參考。ttach]``

2013-05-03 22:05:30

、MAX7000 系列、Mercury、FELX10KE、APEX20KE、APEX20KC、ACEX1K、APEX II和 Stratix 等。 其開發工具 MAX+PLUS II 是較成功

2019-03-04 14:10:13

Max+plusⅡ是Altera公司提供的FPGA/CPLD開發集成環境,Altera是世界上最大可編程邏輯器件的供應商之一。Max+plusⅡ界面友好,使用便捷,被譽為業界最易用易學的EDA軟件

2009-10-09 17:14:29

我最近在用MAX II系列下的芯片EPM240T100C5N,由于是新手就選擇了MAX+Plus ii 這個軟件,請問大家一下,這個軟件支持選擇MAX II系列的芯片嗎?或者如何升級器件選擇列表

2013-11-19 21:33:04

核心部件。”Altera這款新FPGA以本來為CPLD系列“頭銜”的“MAX”來命名,也是想突出其延續了Altera可編程產品物美價廉的傳統,而低成本的MAX 10所擁有的一些性能通常只有高端FPGA才具備。

2019-07-01 08:14:44

想用它來***好用途。問候,沚以上來自于谷歌翻譯以下為原文I'm unable to generate an license key for the MAX+PLUS II Baseline

2018-10-24 15:17:11

MAX PLUS II軟件的學習1 初步了解大規模可編程器件(FPGA)設計的全

2009-10-24 19:17:08

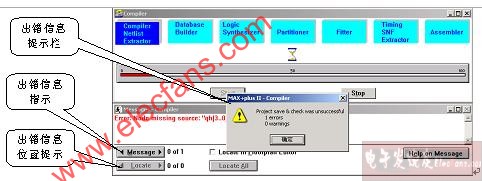

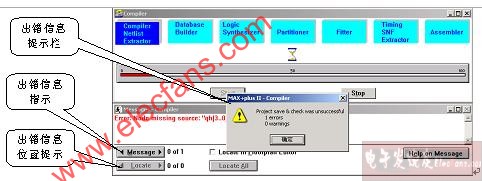

;5、自動錯誤定位在編譯源文件的過程中,若源文件有錯誤,Max+Plus2軟件可以自動指出錯誤類型和錯誤所在的位置。6、邏輯綜合與適配該軟件在編譯過程中,通過邏輯綜合 (Logic

2009-10-09 17:21:44

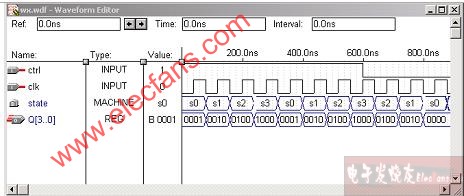

;Max+plusⅡ/Text Editor;Max+plusⅡ/Waveform Editor)3)指定CPLD型號(Assign/Device)4)設置管腳、下載方式和邏輯綜合的方式(Assign

2009-10-09 17:28:51

max+plus問題:max+plus是不是不支持vhdl的否則,為設么每次把vhdl轉換成圖形文件時總會提示library ieee; 哪行錯誤

2012-08-18 14:19:23

、Altera的MAX7000S系列和Lattice(原Vantis)的Mach系列等。將以查表法結構方式構成邏輯行為的器件稱為FPGA,如Xilinx的SPARTAN系列、Altera的FLEX10K

2019-07-01 07:36:55

EPF10K200S, FLEX 6000, MAX? II, MAX 3000A, MAX 7000B, MAX 7000S, MAX 7000AE MAX+PLUS? II 查看和體驗 是 是 RTL查看器和工藝

2012-08-15 12:30:03

USB -CPLD開發板使用攻略一、開發板簡介 簡介:板載大容量 ALTERA MAXII 系列CPLD 芯片EPM1270,和 USB2.0 高速 CY7C68013A芯片,構成完美的邏輯和數

2012-08-15 14:44:47

`現在我有一個atmel的cpld芯片,用了個如下圖所示的下載線一直不能發現設備,如圖.不知道哪位大哥告訴一下該怎么玩,另買一個altera的byteblaster嗎我只有一個積分。。`

2015-12-18 21:07:50

和相應的開發軟件為目標載體進行闡述,本教程闡述了ALTERA主要系列芯片PLD芯片的結構和特點以及相應的開發軟件MAX和Plusa和Quartus的使用。” 希望對各位有用。

2014-05-11 20:44:00

各位大俠,小弟CPLD/FPGA新手,遇到燒錄不保存問題,詳細描述如下:芯片型號:Altera MAX V 5M160ZE64Quartus版本:Quartus II 14.1問題描述:1

2015-07-21 10:40:23

學會CPLD的系統設計技術。本書以ALTERA公司的系列芯片為目標載體,簡要分析了可編程邏輯器件的結構和特點,以及相應開發軟件的使用方法,同時,還用大量篇幅介紹了初學者最容易掌握的Verilog

2018-03-30 15:07:50

用Altera_Cpld作了一個186(主CPU)控制sdram的控制接口, 發現問題:要使得sdram讀寫正確, 必須把186(主CPU)的clk送給sdram, 而不能把clk經cpld的延時

2019-09-18 05:02:19

本公司供應ALTERA、XILINX(FPGA、CPLD)芯片,有需求可聯系深圳市恒兆贏科技有限公司/銷售部:楊綠風phone: 0755-83266848Fax: 0755-83998200QQ

2011-03-02 14:11:22

MAX+ plus Ⅱ簡介 MAX + plus Ⅱ是一種與結構無關的全集成化設計環境,使設計者能對Altera 的各種CPLD 系列方便地進行設計輸入、快速處理和器件編程

2008-06-24 13:48:14

MAX + plus Ⅱ是一種與結構無關的全集成化設計環境,使設計者能對Altera 的各種CPLD 系列方便地進行設計輸入、快速處理和器件編程。MAX+ plus Ⅱ開發系統具有強大的處理

2008-06-16 08:47:47

的專用集成電路(ASIC)的設計。2 Max+PlusⅡ開發工具Max+PlusⅡ開發工具是美國Altera公司自行設計的一種CAE軟件工具。它具有全面的邏輯設計能力,設計者可以自由組合文本、圖形和波形輸入法

2008-10-15 09:00:22

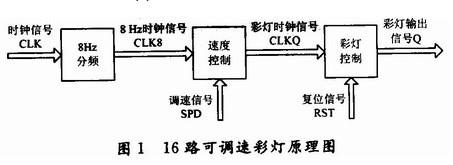

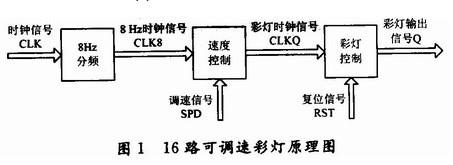

本文介紹應用美國ALTERA公司的MAX+PLUSⅡ平臺,使用VHDL硬件描述語言實現的十六路彩燈控制系統。

2021-04-19 07:43:57

如何利用CPLD去實現接口電路?怎樣去設計MAX+PLUSⅡ程序?

2021-04-28 06:45:34

如何采用Altera的CPLD器件實現時間統一系統的B碼源設計?

2021-05-07 06:21:24

,其中包含VHDL語言、CPLD介紹、AHDL語言和Max+plusⅡ軟件四部分,教材中有大量的有關VHDL、AHDL語言使用的例題,特別是一步一步學習軟件、使用VHDL、AHDL語言的例題可以幫助

2009-10-22 15:44:59

求altera cpld epm2210的PROTEL 99SE的原理圖及PCB圖

2015-05-03 08:54:51

現在altera的CPLD芯片用的最多是哪幾款啊

2013-10-16 18:51:55

推薦一款CPLD芯片大概二三十個引腳四十到六十個邏輯宏單元,最好可以在max plus 2下仿真。

2012-11-23 10:15:51

我現在想用gps的秒脈沖做同步鐘,控制A/D數據同步采集,用哪個系列的cpld功耗最低?以前用過XILINX的95144和ALTERA MAXII系列的epm570,聽說現在都出MAXV了,是不是5M570Z功耗更低?

2019-09-03 14:26:17

為什么要設計電子密碼鎖?基于Max+Plus II和VHDL的電子密碼鎖如何去設計?

2021-04-28 06:12:38

` 本帖最后由 sheniquhong 于 2017-7-6 15:41 編輯

開發板正面圖Altera Strati***板上竟然還有MAX系列的CPLD芯片NIOS II 6.0的flash rom背面圖2006年官方開發板`

2017-07-06 15:41:46

誰有max+plus的軟件的急急!!!!!!謝謝

2012-03-09 23:09:19

我們是AGM的長期授權代理商,可以為用戶提供最具競爭力的價格與技術支持服務。

PIN to PIN Altera-CPLD:

AG576SL144--->

2021-11-23 10:12:42

Max+Plus II簡易用戶使用入門指南

nMAX+PLUS II 為實現不同的邏輯功能提供了許多符號,如:圖元符

2008-09-11 15:09:05 3

3 Third Party EDA Tools Interface with Altera Max+Plus II

What Altera SupportAltera

2008-09-12 09:57:11 0

0 《Altera FPGA/CPLD設計(高級篇)》結合作者多年工作經驗,深入地討論了Altera FPGA/CPLD的設計、優化技巧。在討論FPGA/CPLD設計指導原則的基礎上,介紹了Altera器件的高級應用;引領讀者

2009-02-12 09:19:12 4799

4799 altera fpga/cpld設計 基礎篇結合作者多年工作經驗,系統地介紹了FPGA/CPLD的基本設計方法。在介紹FPGA/CPLD概念的基礎上,介紹了Altera主流FPGA/CPLD的結構與特點,并通過豐富的實例講解

2009-07-10 17:35:45 57

57 FPGA/VHDL技術是近年來計算機與電子技術領域的又一場革命。本書以AAltera公司的FPGA/CPLD為主詳細介紹了FPGA、CPLD為主詳細介紹了FPGA的相關知識,MAX+PLUSⅡ開發環境和VHDL語言基礎,并

2009-07-11 15:06:42 58

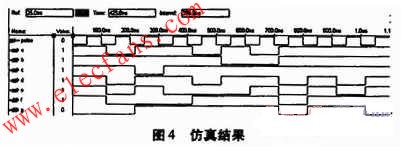

58 本文以MAX+PLUSⅡ軟件為開發平臺,利用CPLD器件設計了一種新型彩燈控制器。該控制器具有控制路數多、功能可擴展、圖案可控制等特點。近年來,出現了一系列生命力強、應用廣

2009-08-17 10:50:41 33

33 EPM1270F256C4N,ALTERA/阿爾特拉,介紹MAX?II系列即時開啟非易失性CPLD基于0.18-μ,6層金屬閃存工藝,密度從240到2210個邏輯元件(LE)(128至22

2023-10-24 15:38:16

探討電梯控制技術的發展歷史和技術現狀,仔細研究CPLD器件的工作原理,開發流程以及VHDL語言的編程方法;采用單片CPLD器件,在MAX+plusⅡ軟件環境下,運用VHDL語言設計一個16樓層單

2010-12-27 15:27:35 56

56 摘??? 要:本文介紹了一個采用PLD,利用MAX+PLUSⅡ和 EWB等開發工具,完成了功率因數精確測量的設計。其核心芯片是Altera公司ACEX 1K系列的EP1K10TC144-3。引言在電力

2006-03-11 12:55:52 3437

3437

摘要:以Altera公司MAX700舊系列為代表,介紹了CPLD在DSP系統中的應用實例。該方案具有一定的普遍適用性DSP的速度較快,要求譯碼的速度也必

2006-03-11 17:39:49 1464

1464

摘要:簡要介紹了CPLD/FPGA器件的特點和應用范圍,并以分頻比為2.5的半整數分頻器的設計為例,介紹了在MAX+plus II開發軟件下,利用VHDL硬件描述語言以及原理圖的輸

2006-03-13 19:36:44 869

869

Altera MAX+plus II 介紹

一、軟件功能簡介MAX+plusⅡ(Multiple Array and Programming Logic User System)開發工具是美國Altera 公司推出的一種EDA

2008-09-24 10:15:36 6852

6852

實驗一、MAX+PLUSⅡ的基本應用一 實驗目的1掌握MAX+PLUSⅡ的安裝及基本使用。2掌握MAX+PLUSⅡ基本輸入法—圖形輸入工具按鈕的使用。二 實驗設備

2009-03-13 19:15:01 3816

3816

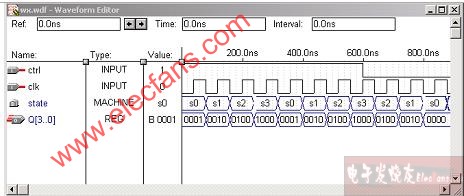

MAX+PLUSⅡ的基本應用-波形輸入練習一 實驗目的1掌握MAX+PLUSⅡ的基本使用。2掌握MAX+PLUSⅡ基本輸入法—波形輸入法的使用。二 實驗設備與儀器

2009-03-13 19:16:05 2215

2215

實驗三 MAX+PLUSⅡ的設計處理

一 實驗目的1掌握MAX+PLUSⅡ的基本使用。2掌握MAX+PLUSⅡ的設計處理過程中的編譯和仿真。3 掌

2009-03-13 19:19:02 1020

1020

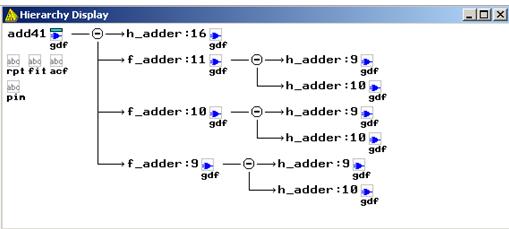

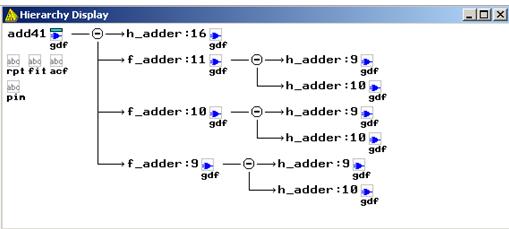

實驗四、MAX+PLUSⅡ的層次設計一 實驗目的1進一步掌握MAX+PLUSⅡ的基本使用,包括設計的輸入、編譯和仿真。2掌握MAX+PLUSⅡ的層次化設計方法。二

2009-03-13 19:20:48 1500

1500

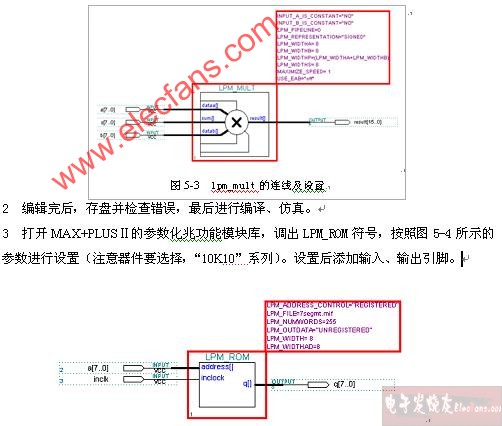

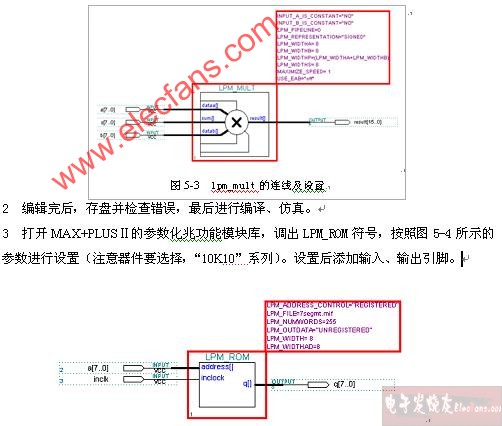

實驗五、MAX+PLUSⅡ的參數化兆功能模塊庫的使用一 實驗目的1進一步掌握MAX+PLUSⅡ參數化兆功能模塊庫的使用。2了解參數化兆功能模塊庫LP

2009-03-13 19:23:18 1446

1446

一、 配置方式

ALTERA CPLD器件的配置方式主要分為兩大類:主動配置方式和被動方式。主動配置方式由CPLD器件引導配置操作過程,它控制著外部存儲器和

2009-06-20 10:58:14 1928

1928 ?摘 要: 介紹了一種利用工具軟件MATLAB強大的數學功能來增強ALTERA公司的可編程邏輯器件設計軟件MAX+PLUSII的仿真功能、提高設計品質的方法,有較強的針對性。

???

2009-06-20 11:45:15 843

843

摘要:簡要介紹了CPLD/FPGA器件的特點和應用范圍,并以分頻比為2.5的半整數分頻器的設計為例,介紹了在MAX+plus II開發軟件下,利用VHDL硬件描述語言以及原理圖的輸

2009-06-20 12:45:00 627

627

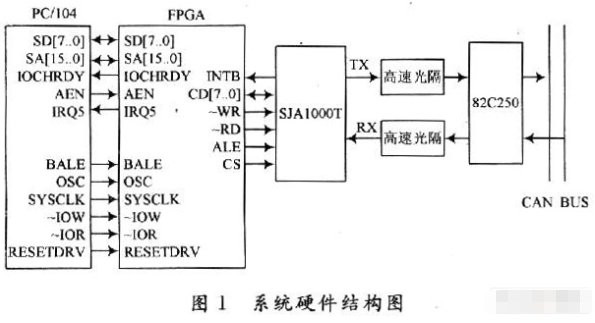

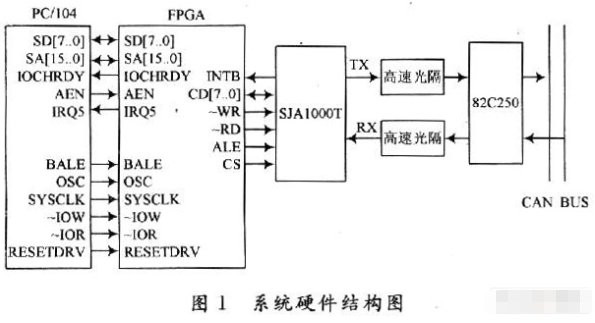

摘 要:本文介紹了一種利用可編程器件CPLD實現CAN總線與微機之間接口的設計,說明了設計思想和設計方案,并給出了使用MAX+PLUS Ⅱ軟件圖形輸入法的邏輯設計和

2009-06-20 14:56:08 571

571

Altera增強MAX II系列,進一步拓展其CPLD應用

Altera公司宣布,提供工業級溫度范圍以及功耗更低的MAX IIZ器件,從而進一步增強了MAX II CPLD系列。MAX IIZ CPLD完美的結合了邏輯

2009-11-05 09:53:58 1283

1283 MAX+PLUSⅡ符號庫提供了很多基本圖元(Primitive, 又稱原語)供圖形設計文件調用, 這些圖元大體上可分為緩沖器、 寄存器、 輸入輸出端口、 邏輯門圖元等幾類。其中寄存器和組合

2010-06-07 10:26:59 3942

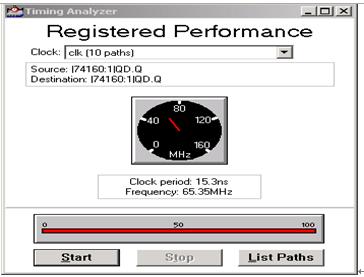

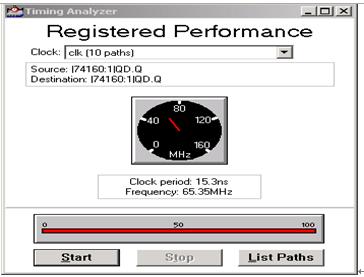

3942 1 引言 Altera的 MAX+PLUSⅡ可編程邏輯開發軟件,提供了一種與工作平臺、器件結構無關的設計環境,深受廣大電子設計人員的喜愛。但設計人員都會遇到Altera器件設計中的時間匹配

2010-07-05 10:31:05 1092

1092

O 引言

MAX+PLUSⅡ開發系統是易學易用的完全集成化的設計開發環境。目前已發行10.0版本。該軟

2010-12-23 11:33:45 3252

3252

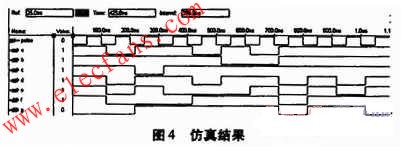

本文利用Max+ Plus 軟件對PCM30/ 32 路系統的發送端時序與幀結構進行了仿真,由仿真結果可以清楚地發現該系統發端時序的規律

2011-03-28 10:55:27 2507

2507

本文介紹了Altera器件和MAX+PLUS II的開發流程,然后將變電所進行抽象,得到了設計對象。將系統定義為命令輸入、外部條件輸入、開關控制邏輯電路、開關控制時序電路等幾個模塊

2011-04-15 15:47:13 41

41 本文選用CPLD 是ALTERA 公司的EPM240T100,結合MAX232 接口芯片進行串口通信設計

2011-04-25 11:44:28 12054

12054

什么是.scf?答:SCF文件是MAXPLUSII的仿真文件, 可以在MP2中新建. 用Altera_Cpld作了一個186(主CPU)控制sdram的控制接口, 發現問題:要使得sdram讀寫正確, 必須把186(主CPU)的clk送給sdram, 而不能

2011-05-25 17:35:22 36

36 Altera提供全面的定制邏輯器件系列產品FPGA、ASIC和CPLD。 學會以下術語有助于你加速實現Altera器件的開發。 自適應邏輯模塊(ALM) 協議實現配置(CvP) 嵌入式HardCopy模塊......

2012-06-04 14:02:43 20

20 本資料是關于Altera FPGA的選型及開發,內容大綱是:Altera的 FPGA體系結構簡介;Altera的 FPGA選型策略;嵌入式邏輯分析工具SignalTAPII的使用;基于CPLD的FPGA配制方法。

2012-08-15 14:48:34 103

103 MAX+PLUS II軟件下載入口

2012-09-14 14:27:47 447

447 altera FPGA/CPLD高級篇(VHDL源代碼)

2012-11-13 14:40:38 134

134 Altera FPGA_CPLD設計(實例源代碼)

2013-09-09 16:09:23 442

442 Third Party EDA Tools Interface with Altera Max+Plus II

2022-08-01 11:11:45 5

5 Max+plusⅡ是Altera公司提供的FPGA/CPLD開發集成環境,Altera是世界上最大可編程邏輯器件的供應商之一。Max+plusⅡ界面友好,使用便捷,被譽為業界最易用易學的EDA軟件

2022-07-13 10:09:01 0

0 幫助讀者學會設計數字系統的硬件描述語言VHDL、并熟悉Altera公司產品和軟件Max+PlusⅡ。

2022-07-10 14:34:02 0

0 在第一章我們詳細介紹了VHDL語言,世界各大半導體公司開發的設計軟件都支持該語言,MAX+PLUS II軟件也支持該語言,下面介紹VHDL語言是如何在MAX+PLUS II軟件中使用的。

2022-08-01 14:30:45 0

0 Max+plusⅡ功能簡介 1 、原理圖輸入(Graphic Editor) MAX+PLUSII軟件具有圖形輸入能力,用戶可以方便的使用圖形編輯器輸入電路圖,圖中的元器件可以調用元件庫中元

2017-12-05 10:27:33 5

5 VHDL語言 在第一章我們詳細介紹了VHDL語言,世界各大半導體公司開發的設計軟件都支持該語言,MAX+PLUS II軟件也支持該語言,下面介紹VHDL語言是如何在MAX+PLUS II軟件中使

2017-12-05 10:37:54 11

11 Max+PlusⅡ是Altera公司提供的FPGA/CPLD開發集成環境,它可獨立完成簡單VHDL程序的編譯。然而,自動電梯控制程序是一個復雜的狀態機描述,Max+PlusⅡ無法獨立完成該程序的綜合編譯。

2018-05-27 11:38:00 4195

4195

QuartusⅡ是Altera公司在21世紀初推出的FPGA/CPLD集成開發環境,是Altera公司前一代FPGA/CPLD集成開發環境Max+PlusⅡ的更新換代產品,其界面友好,使用便捷,功能強大,為設計者提供了一種與結構無關的設計環境,使設計者能方便的進行設計輸入、快速處理和器件編程。

2019-05-03 07:35:00 6242

6242

用VHDL語言設計交通燈控制系統,并在MAX+PLUS II系統對FPGA/CPLD芯片進行下載,由于生成的是集成化的數字電路,沒有傳統設計中的接線問題,所以故障率低、可靠性高,而且體積小。體現了EDA技術在數字電路設計中的優越性。

2018-11-05 17:36:05 23

23 本文檔的主要內容詳細介紹的是FPGA教程之ALTERA的CPLD與FPGA器件的詳細資料說明主要內容包括了:一、Altera器件一般介紹,二、MAX 7000 系列器件,三、FLEX10K系列器件,四、邊界掃描測試

2019-02-27 17:27:31 15

15 QuartusⅡ是Altera公司在21世紀初推出的FP-GA/CPLD開發環境,是Altera前一代FPGA/CPLD集成開發環境MAx+PlusⅡ的更新換代產品,其功能強大,界面友好,使用便捷

2021-06-08 15:43:08 2972

2972

Altera FPGA CPLD學習筆記(肇慶理士電源技術有限)-Altera FPGA CPLD學習筆記? ? ? ? ? ? ? ? ?

2021-09-18 10:54:41 79

79 CPLD的MAX系列器件庫max-13.0.1.232

2022-12-21 17:26:11 4

4

電子發燒友App

電子發燒友App

評論