無線基礎設施、寬帶和儀器儀表應用通常需要高性能的時鐘電路,它們主要需要時鐘的器件是高速數據轉換器。這些系統的時鐘電路所需的幾個關鍵性能指標包括低相位噪聲和抖動、精確的頻率轉換和去抖動能力。高性能轉換器時鐘解決方案所體現的許多屬性可被有線網絡所用的時鐘解決方案延用。整個有線網絡對互操作性和可靠同步的需求也衍生出某些獨特的時鐘系統需求。希望這篇文章有助于對這兩個應用領域的時鐘技術需求進行對比和分析。

轉換器時鐘

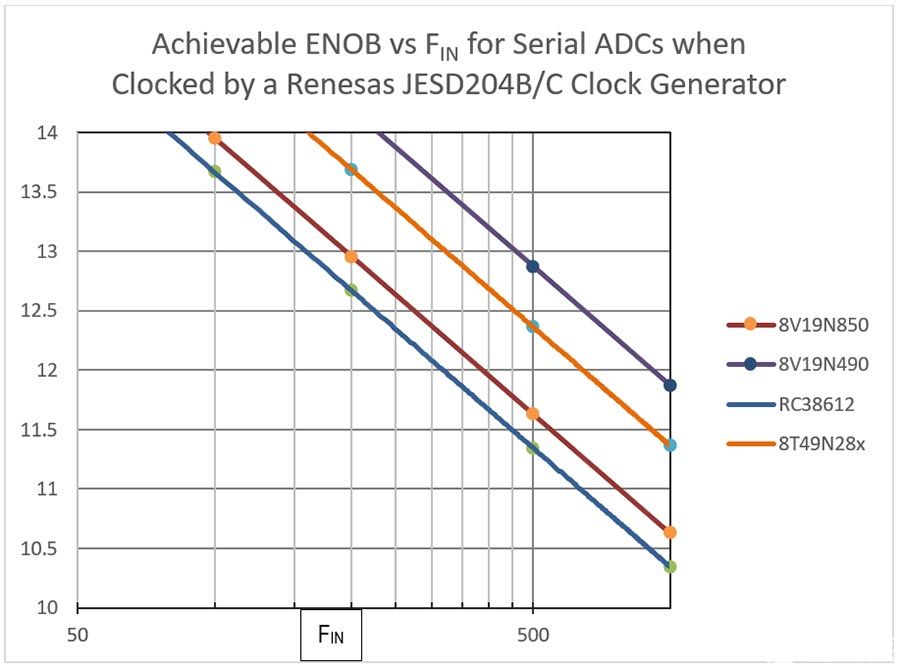

基站收發器、寬帶調制解調器和高端儀器儀表通常需要具有高動態范圍和高采樣率的ADC和/或DAC。高動態范圍是為了將信號解析到所需的精度。高采樣率則是處理高帶寬信號所必需的。無論是無線電系統、調制解調器或者是測量儀器,對轉換器的要求將取決于整個系統的規格參數和架構。該轉換器的采樣時鐘的頻譜純度往往會對實際達到的性能產生重大影響。

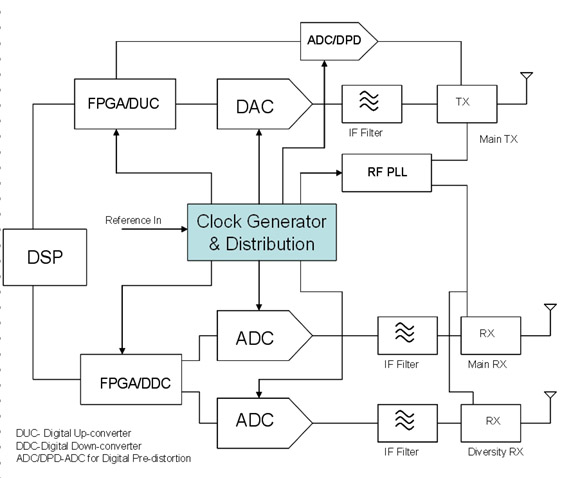

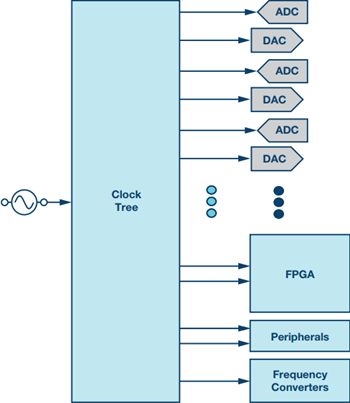

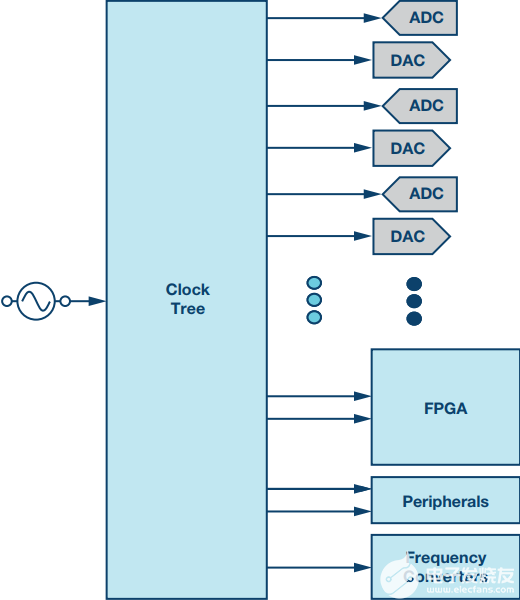

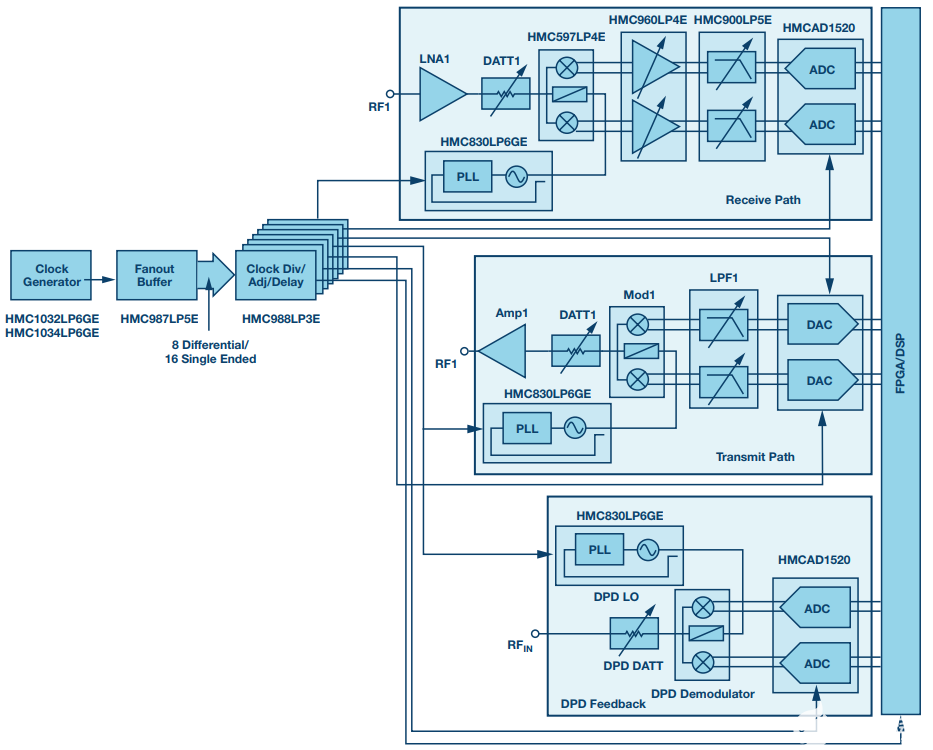

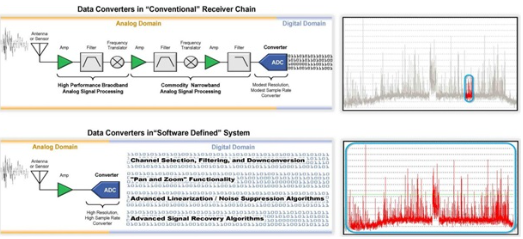

一個無線收發器電路的例子如圖1所示。除了為ADC和DAC提供時鐘,時鐘發生器還負責將時鐘信號分配到收發器卡上的其他幾個電路模塊。接下來我們將集中討論時鐘抖動和相位噪聲對ADC性能的影響。

圖1:收發器系統框圖。

無線電接收器中ADC的一個關鍵指標是信噪比(SNR),它將影響到ADC在給定幅度范圍內能夠達到的信號采樣精度。理想情況下,ADC應該能夠以很高的分辨率將非常小的模擬輸入信號轉換成精確的數字信號。按照無線電術語,ADC的SNR將決定最小可檢測信號(MDS)。

N位轉換器基于量化噪聲的理論SNR等于:

SNR = 6.02(N) + 1.8 db

因此,對于一個14位轉換器,其可以實現的最佳SNR大約為86db。

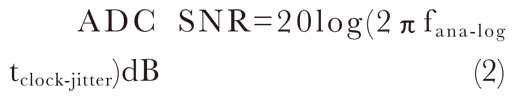

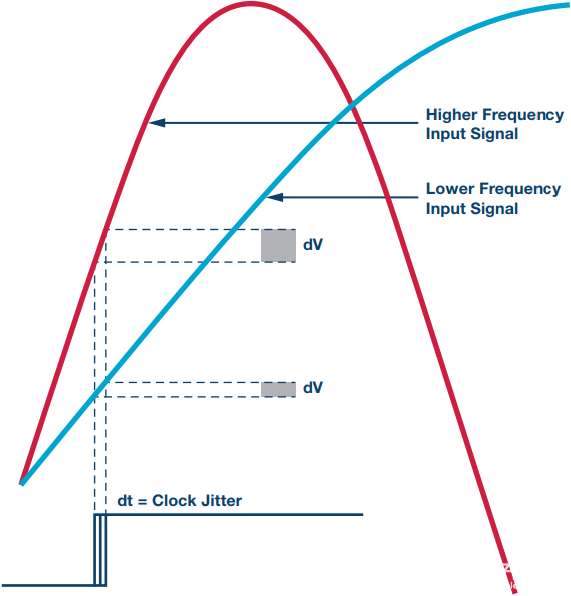

在IF采樣架構中,如圖1所示框圖,對時鐘抖動的要求可以說非常嚴格。事實上,提供給ADC的時鐘的質量常常是系統SNR性能的一個限制因素。這可以通過以下公式來理解。

這個公式定義了采樣時鐘的寬帶抖動與ADC在某一給定模擬輸入頻率抖動情況下可以達到的最大SNR之間的關系。舉例來說,如果采樣時鐘的寬帶抖動為275fs ,對170MHz的中頻信號采樣時,SNR基本上不會高于70.65db。

實際上,ADC內的其他噪聲機制通常會將SNR值限制在低于理論水平或量化噪聲(公式1) 。這一內部噪聲是由于模擬信號路徑和采樣時鐘路徑中的器件熱噪聲而引起的。采樣時鐘路徑中的器件噪聲有效地轉換為相位調制噪聲,又稱為孔徑抖動。這種行為就像外部時鐘上的抖動,遵循公式2 ,孔徑抖動(taperture-jitter)代替時鐘抖動(tclock-jitter)。由公式2可以看出,隨著采樣的IF頻率(fanalog)增加,SNR下降。

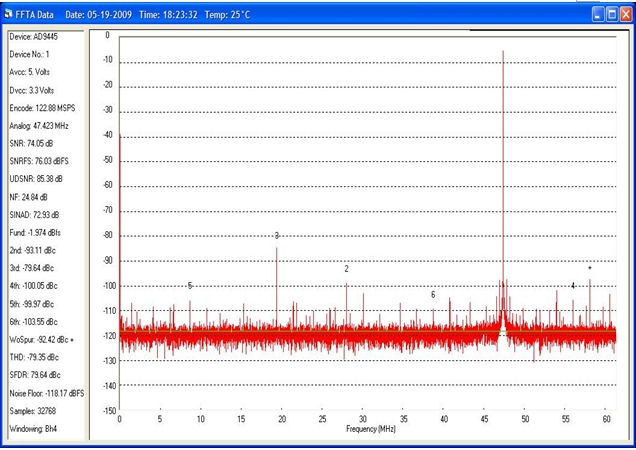

外部時鐘的頻譜純度與ADC可實現的SNR之間的關系,可以通過以下一組實驗室測量數據進行表述。圖2顯示了14位ADC采樣170MHz中頻信號的FFT波形。在這種情況下所用的外部時鐘是源自頻譜純凈的Wenzel實驗室參考振蕩器,驅動著帶高壓擺率輸出信號的低抖動矩形波整形電路。測量的意圖是盡量減少時鐘的影響,并確定由于ADC效應所達到的SNR。由此產生的相對滿量程輸入信號的SNR測量數據,在圖中標示為SNRFS,是76db。這與ADC數據手冊1是一致的。Wenzel實驗室參考振蕩器的確會對SNR有一定影響,但所測的SNR主要是受ADC量化噪聲和內部ADC孔徑抖動的共同影響。

圖2:14位ADC的FFT波形。模擬輸入頻率= 170MHZ,時鐘頻率= 122.88MHz。SNRFS =76db。

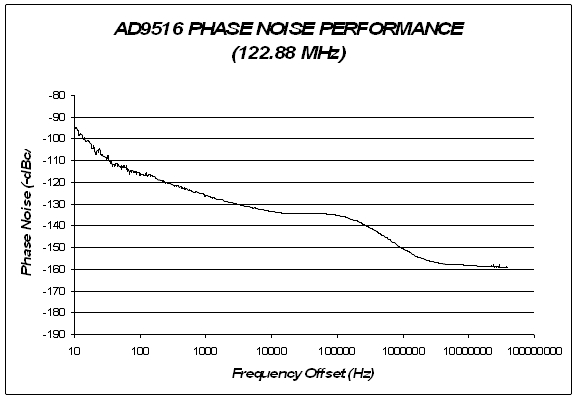

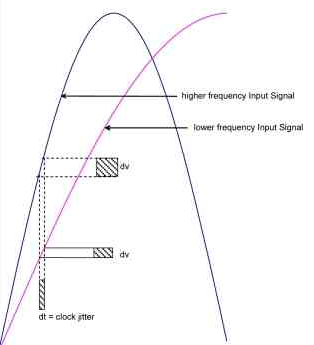

現在,我們將使用一個適合實際收發卡時鐘應用的內置VCO的時鐘IC。為了估算這一時鐘信號對ADC性能產生的影響,我們可以先測量時鐘電路的相位噪聲。其相位噪聲曲線如圖3所示。

圖3 :時鐘IC在122.88MHz下的相位噪聲

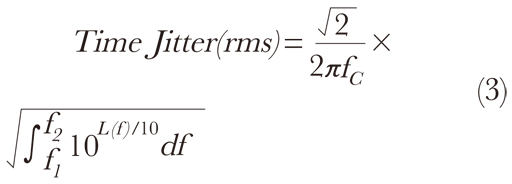

在給定的頻率范圍內,我們可以使用下列公式來將相位噪聲轉換成時間抖動。

該公式本質上是對相位誤差在目標頻率范圍內進行積分并從一個相對2π的積分弧度誤差轉換成均方根時間誤差。

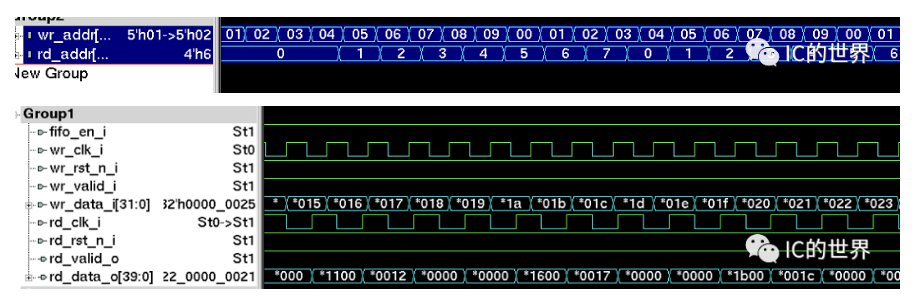

將圖3的相位噪聲數據代入公式3,在50kHz至61MHz的頻率范圍內,會得出230fs的抖動值。50kHz至61MHz頻率范圍是用來對應有效的FFT測量范圍,后者將用于檢驗抖動對所測SNR的影響的估算是否準確。低至50kHz是源于FFT的有效二進制間距,高至61MHz是奈奎斯特頻率。將得出的230fs抖動代入公式1則得出72.2db的SNR值。

然而,實際達到的SNR將受到該抖動和固有ADC噪聲的共同影響。圖2 FFT波形的SNR(76db)與根據時鐘抖動得出的估算值(72.2db)的和平方根將得出70.68db的復合SNR。

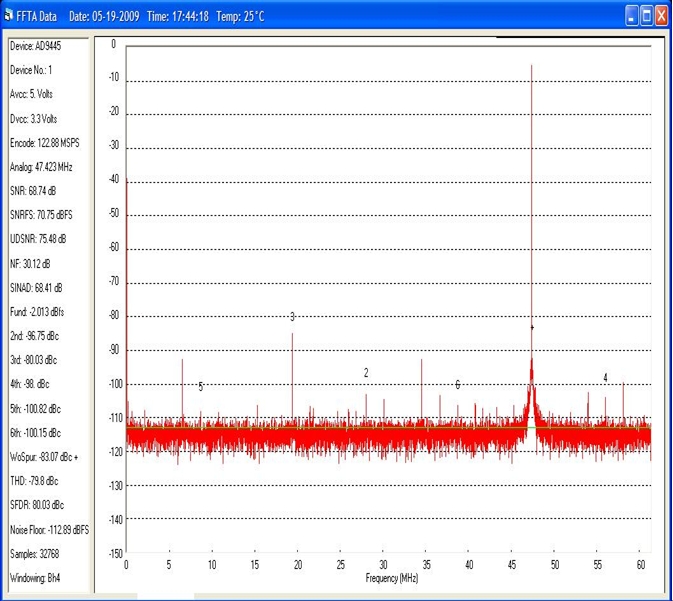

為了檢驗這一估算值,圖4顯示了采用此時鐘IC作為采樣時鐘的相應ADC FFT波形。所達到的SNR接近基于時鐘抖動的估算值,體現了時鐘抖動對ADC性能的影響至關重要。

圖4:采用時鐘IC的14位ADC的FFT波形。模擬輸入頻率= 170MHZ,時鐘頻率= 122.88MHz。SNRFS =70.75db。

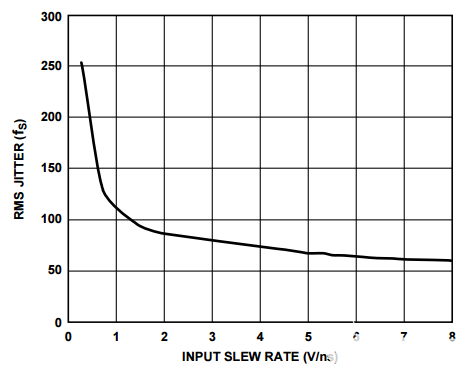

應該強調的是,公式2中的抖動是寬帶均方根抖動。抖動帶寬有時被認為是ADC編碼輸入的有效帶寬。由于該ADC是個采樣系統,編碼輸入的寬帶噪聲在奈奎斯特頻帶內可能被混疊多次。被混疊的抖動帶寬的有效數字等于將奈奎斯特帶寬除以編碼輸入的帶寬。(見參考文獻3提供的詳細方案)。但如果時鐘邊沿的壓擺率很快速,在編碼輸入處噪聲電壓到時間誤差(抖動)的轉換將被衰減。通過在編碼輸入之前改善時鐘邊沿和保持很高的壓擺率可獲得最佳的性能。在這些條件下,將抖動進行高達奈奎斯特頻率的積分就可提供一個合理的估算,因為上述相關性表明了該時鐘抖動對ADC SNR的影響。

盡管上述討論的重點是ADC,本底噪聲和DAC的SNR由于高抖動采樣時鐘會以類似方式下降。

采樣時鐘的寬帶抖動并不是采樣時鐘頻譜純度的唯一需要考慮的方面。“近載波”(close-in)相位噪聲3也會影響系統性能。

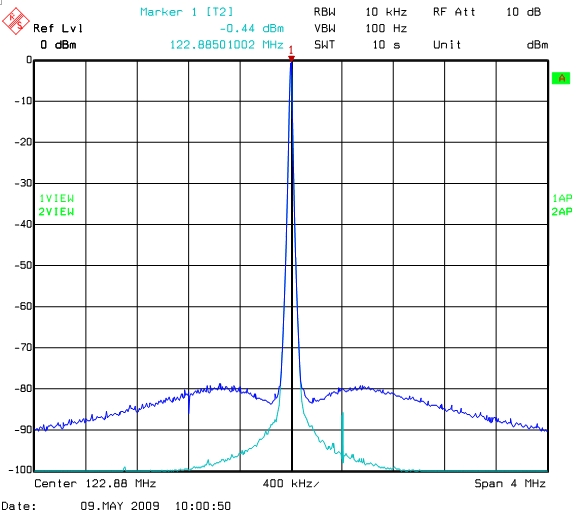

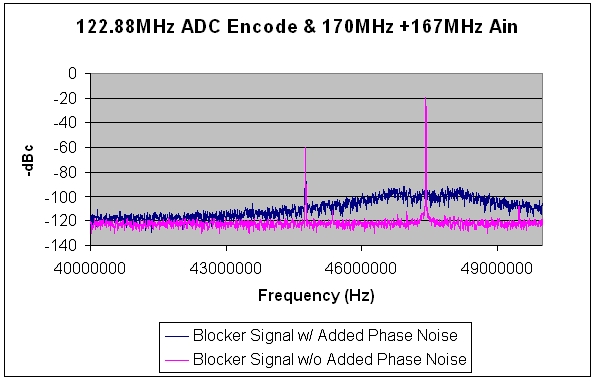

不過近載波相位噪聲對SNR的影響甚微,更重要的影響來自相鄰信道信號產生的相位噪聲,可以使一個“有用”信號失真。這種效應類似于模擬混頻過程中的相位噪聲相互混頻。轉換器的編碼過程本質上是復制混頻過程。編碼時鐘和模擬輸入信號在時域中相乘。這相當于在頻域中進行大家熟知的卷積。如圖5所示,其結果是造成在編碼時鐘上的任何相位噪聲裙緣將被復制在采樣輸入信號上。基于編碼率和采樣信號之間的頻率比例,關于每個載波幅度的相對相位噪聲將被修改。一個強相鄰信道信號的相位噪聲裙緣擴展到一個有用弱信道時,并有效地使后者失真,問題就出現了。圖6的FFT波形體現了這種效應。在此圖中,一個ADC采樣一個小的有用信號,但存在很強的相鄰干擾,干凈時鐘條件和高相位噪聲條件相重疊。可以看出,時鐘的相位噪聲裙緣在強干擾上被復制,并擴展到有用信號的頻帶中。取決于所采用的調制標準,相位噪聲頻率偏移可從數十kHz擴展至數MHz。

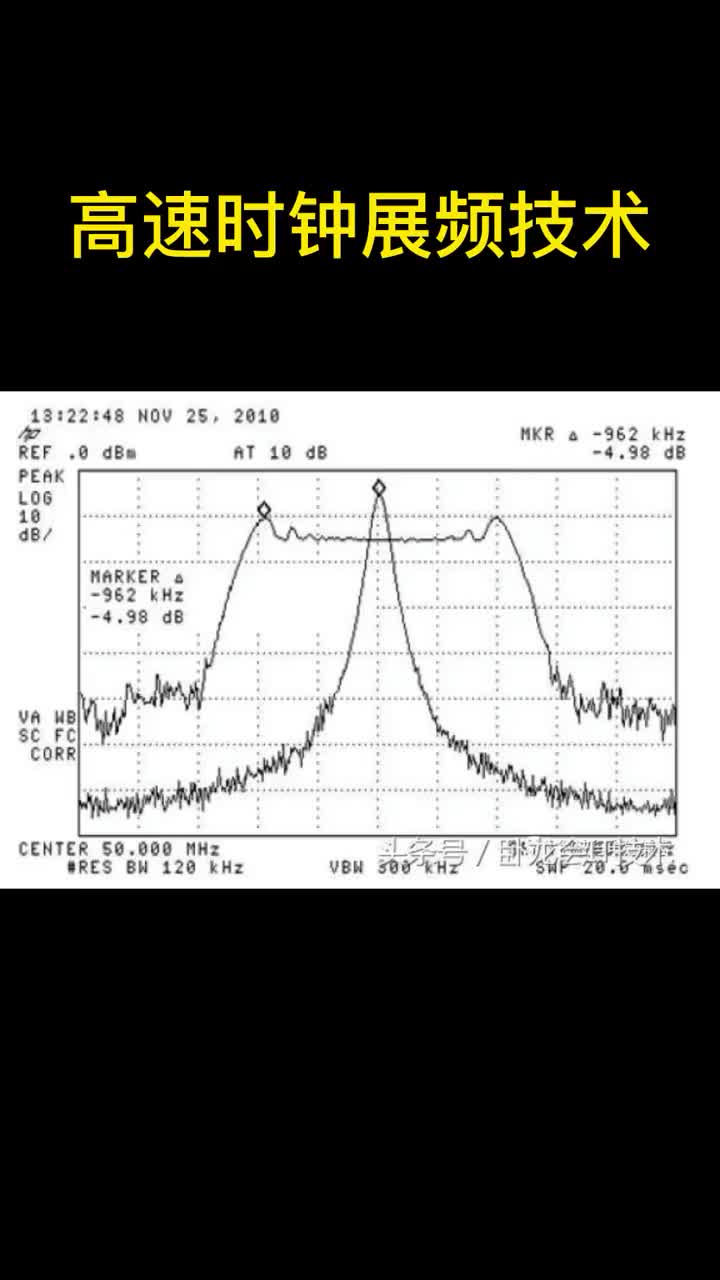

圖5 :頻譜分析儀波形圖:層疊在干凈時鐘上的帶高相位噪聲的編碼。

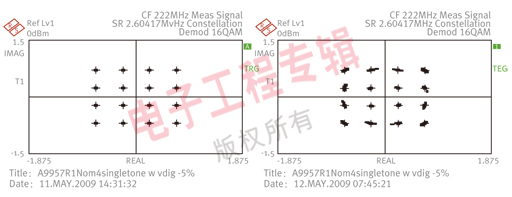

采樣時鐘相位噪聲對DAC的影響通常表現為調制信號的誤差向量幅度(EVM)有所降低。對于給定的調制方案,高相位噪聲有效地影響星座點使EVM下降并潛在地提高了誤碼率。圖7所示的16 QAM星座圖中體現了這一點。圖7(a)展示了干凈時鐘條件下的星座圖。圖7(b)展示了高相位噪聲時鐘對星座圖的影響。相位噪聲事實上旋轉了降低相鄰點噪聲容限的星座點有效相位。應當注意的是,寬帶相位噪聲和抖動也會降低EVM。在帶通濾波用于DAC輸出的應用中,主要的考慮事項就是近載波相位噪聲。

圖7:(a)干凈時鐘的16QAM星座圖。(b) 帶高相位噪聲的時鐘對星座圖的影響。

顯然,時鐘的頻譜純度是收發器時鐘解決方案的一個關鍵方面,但人們還期望時鐘系統能提供其他一些功能。

回到圖1可看到,該收發器具有多個接收通道,每個都需要單獨的ADC。在某些情況下,也會使用多個DAC通道。可能需要額外的時鐘通道來為用于數字預失真、FPGA或基帶ASIC芯片的ADC提供時鐘。

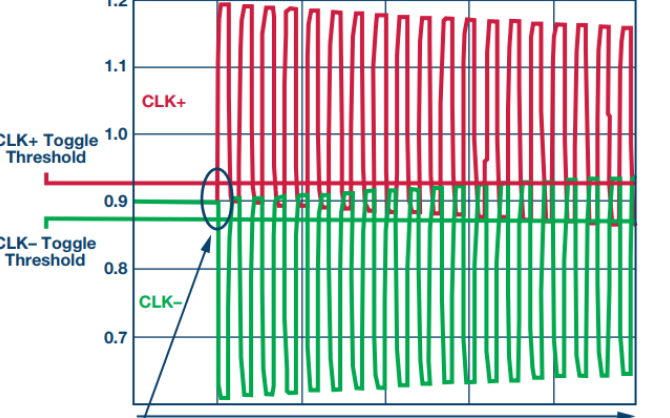

DAC和ADC編碼率通常各不相同。FPGA和基帶元器件也可能需要不同的頻率。頻譜干凈的主時鐘信號需要單獨分配給每個通道,為該通道分頻為所需的頻率,然后轉換成適當的輸出信號格式。單一收發卡的輸出信號通常混合了LVPECL、LVDS和CMOS格式。兩個通道之間往往要求偏斜很緊密,以限制PCB布線的延遲變化。在某些情況下,在兩個時鐘之間設置延遲或相位偏移是必要的。在轉換器采樣時鐘和用于將ADC輸出數據鎖存到基帶芯片的時鐘之間可能需要這樣做。

在這些系統中,通道與通道之間的耦合是一個需要考慮的因素。如前所述,DAC和ADC時鐘通常運行于不同的頻率。通道之間的耦合,或時鐘從一個通道向另一個饋送可能會在采樣時鐘上導致不想要的雜散音。有用的時鐘信號和無用的噪聲可能會導致產生乘積混頻,這可能在有問題的地方產生毛刺。如果混頻發生在編碼輸入處,這些問題有時可通過在主時鐘和輸入時鐘邊沿及時進行偏置而得到緩解。具備調節每個低抖動時鐘延遲的能力可以成為時鐘系統的一項優勢。

為了盡量減少系統宕機時間,在輸入參考出現故障的情況下,時鐘系統應提供“備份”功能。這可通過增加第二個參考輸入來實現,在主參考出錯的情況可以切換到這個備份參考輸入。這種備份時鐘的指配有時被稱為“時鐘冗余”。監測主時鐘、檢測故障然后切換到備份的能力被稱為“參考切換”功能。

對于主時鐘和輔時鐘均出現故障的情況,可實施另一層保護功能,被稱為“保持(holdover)”。在保持模式中,時鐘系統進入一種模式,即在輸入失效之前盡可能長時間地保持時鐘頻率。對于給定的時鐘系統,保持的準確性和持續時間取決于時鐘電路架構。本文第二部分在討論網絡時鐘時對此會有更詳細的闡述,因為那些系統中的保持模式要嚴格得多。對于收發器系統,保持模式并不試圖讓收發器工作在它的正常性能水平,而是要保持足夠的時鐘功能,如可生成適當的系統警報以啟動系統修復。

總而言之,多種多樣的系統需求廣泛存在,以支持各種各樣的空間標準、系統通道數要求和架構方案。這些系統的時鐘必須足夠靈活,以適應廣泛的應用、保證系統可靠性并且還能夠提供轉換器所要求的極低抖動和相位噪聲。

(1) AD9445:14位125MSPS , IF采樣ADC

(3) 采樣系統和時鐘相位噪聲和抖動的影響。

電子發燒友App

電子發燒友App

評論