應(yīng)對(duì)FPGA/SDI子系統(tǒng)中的高速板布局挑戰(zhàn)

美國(guó)國(guó)家半導(dǎo)體公司? Tsun-kitChin簡(jiǎn)介

電視和影院已經(jīng)進(jìn)入數(shù)字時(shí)代。視頻圖像曾以標(biāo)準(zhǔn)傳輸率(270Mb/s)傳輸,后來(lái)升級(jí)到高傳輸率(1.485Gb/s),現(xiàn)在已上升到3Gb/s。更高傳輸率實(shí)現(xiàn)了更高分辨率的娛樂(lè)圖像傳輸,但同時(shí)也使硬件工程師和物理布局設(shè)計(jì)師面臨著更大的挑戰(zhàn)。很多視頻系統(tǒng)都采用多功能FPGA和多傳輸率SDI集成電路,以支持高性能專(zhuān)業(yè)視頻在長(zhǎng)距離的傳輸。FPGA需要高密度、細(xì)跡線(xiàn)寬度的傳輸,而高速模擬SDI傳輸需要阻抗匹配和信號(hào)保真。本論文概述了硬件工程師面臨的挑戰(zhàn),并為處理這些挑戰(zhàn)提供了建議。

FPGA/SDI子系統(tǒng)

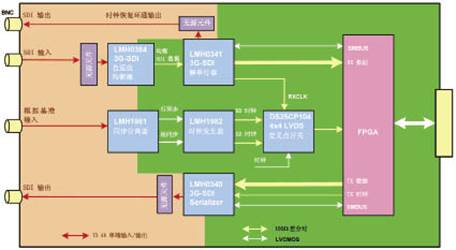

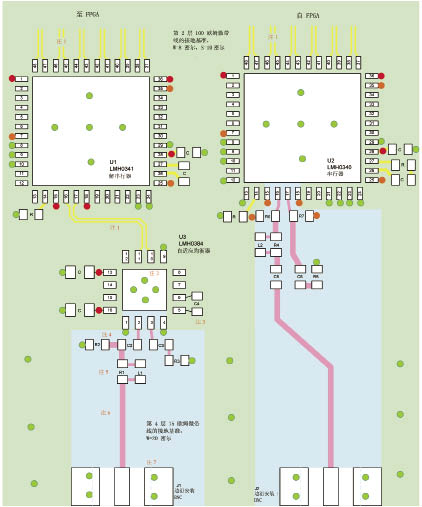

在典型的FPGA/SDI板中,數(shù)字視頻信號(hào)在BNC(卡拴式同軸接頭)與高性能SDI75?跡線(xiàn)模擬集成電路之間傳輸。FPGA和SDI集成電路之間的互連包含通過(guò)FPGA細(xì)間距球柵發(fā)送的多對(duì)100?差分信號(hào)。其中一個(gè)布局難點(diǎn)是75?單端跡線(xiàn)和100?差分跡線(xiàn)的共存。通常,這兩種跡線(xiàn)在元件所在頂層上傳輸。適合75?的跡線(xiàn)寬度對(duì)于100?跡線(xiàn)可能過(guò)寬。圖1是FPGA/SDI的示意框圖,顯示75?和100?的兩個(gè)區(qū)。

圖1 典型FPGA/SDI框圖

SDI布局難點(diǎn)

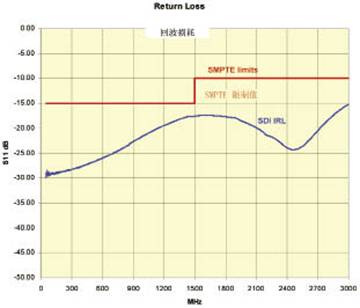

電影與電視工程師學(xué)會(huì)(SMPTE)發(fā)布了同軸電纜上數(shù)字視頻的傳輸標(biāo)準(zhǔn)。規(guī)定信號(hào)幅值為800mV±10%。必須通過(guò)芯片外的75?±1%精確終端電阻器滿(mǎn)足此幅值要求。SMPTE標(biāo)準(zhǔn)還包含輸入和輸出的回波損耗要求,基本規(guī)定了輸入或輸出端口如何近似于75?網(wǎng)絡(luò)。圖2顯示SMPTE對(duì)回波損耗的要求。

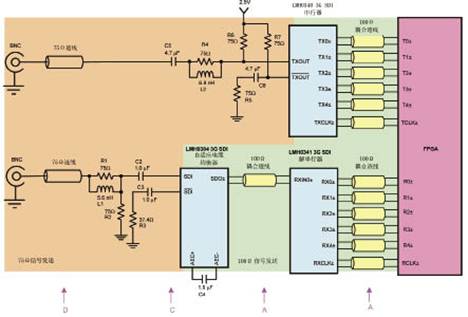

芯片外阻抗平衡網(wǎng)絡(luò)由電感器和并聯(lián)電阻器構(gòu)成,通常用于抵消SDI集成電路的輸入或輸出電容。大交流耦合電容器(4.7μF)通常用于傳輸SDI串行位流,以避免低頻直流漂移。如圖3所示,75?跡線(xiàn)的SDI集成電路及其BNC連接器之間附有多個(gè)芯片外無(wú)源元件。每個(gè)元件都具有串聯(lián)寄生電感,每個(gè)元件焊盤(pán)又具有并聯(lián)寄生電容,從而影響與75?匹配的總阻抗。SDI布局的難點(diǎn)在于最大限度減少外部無(wú)源元件在75?SDI端口造成的阻抗失配。

選擇FPGA/SDI子系統(tǒng)的板堆疊

應(yīng)該使用什么跡線(xiàn)寬度 在小于3Gb/s的SDI速度中,銅損耗很小,并不構(gòu)成選擇跡線(xiàn)寬度的重要考慮因素。選擇略小于元件接合焊盤(pán)的跡線(xiàn)寬度更為重要,以最大限度減少阻抗失配。0402尺寸的無(wú)源元件需要20密爾x25密爾的接合焊盤(pán),以使15密爾到20密爾的跡線(xiàn)寬度最適合于75?SDI跡線(xiàn)。

為了便于傳輸和偏斜匹配,F(xiàn)PGA的100?差分信號(hào)使用細(xì)跡線(xiàn)寬度傳輸。寬松的耦合跡線(xiàn)通常用于避免較大的阻抗變化,而分支出的緊密耦合跡線(xiàn)則連接到終端電阻器或交流耦合電容器。

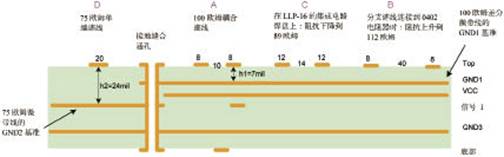

圖4顯示了適用于FPGA和SDI信號(hào)傳輸?shù)陌宥询B。在此堆疊中,SDI信號(hào)跡線(xiàn)采用在第4層以GND2為基準(zhǔn)的75?單端微帶線(xiàn)。GND2是在第4信號(hào)層形成的金屬島。第2和第3層的金屬(GND1和VCC面)在75?跡線(xiàn)區(qū)被移除,以使其不會(huì)降低跡線(xiàn)的特征阻抗。FPGA的100?差分跡線(xiàn)是在第2層以GND1為基準(zhǔn)的寬松耦合微帶線(xiàn)。兩個(gè)接地基準(zhǔn)(GND1和GND2)通過(guò)接地縫補(bǔ)鍍通孔相連。此板堆疊排列允許通過(guò)調(diào)節(jié)絕緣長(zhǎng)度h2自由選擇75?跡線(xiàn)的寬度,以及通過(guò)調(diào)節(jié)h1自由選擇100?跡線(xiàn)的寬度。

圖2? SDI端口和SMPTE限制值的輸入回波損耗圖

圖3 典型SDI電路(僅顯示高速信號(hào)路徑)

圖4 具有75?和100?跡線(xiàn)單獨(dú)接地參考的板堆疊

BNC連接器的布局

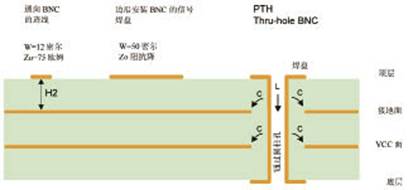

很多SDI板的常見(jiàn)問(wèn)題是使用非優(yōu)化BNC連接器布局,因此產(chǎn)生嚴(yán)重的阻抗失配、無(wú)法滿(mǎn)足回波損耗要求,并削弱了設(shè)備的信號(hào)保真度。圖5顯示板的橫截面,其中12密爾寬的微帶線(xiàn)連接到50密爾寬的邊沿安裝BNC焊盤(pán)上。接地面被置于頂部跡線(xiàn)下的絕緣距離點(diǎn)上,以實(shí)現(xiàn)目標(biāo)跡線(xiàn)阻抗。連接器的接合焊盤(pán)是寬微帶線(xiàn),因此焊盤(pán)的特征阻抗略低于跡線(xiàn)阻抗。焊盤(pán)具有較大的阻抗降,從而影響回波損耗和限制跡線(xiàn)的傳輸帶寬。

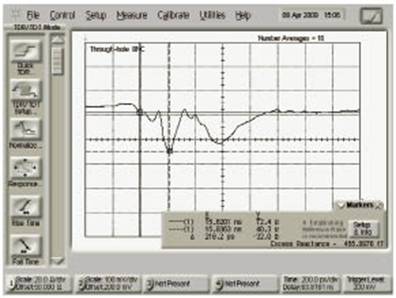

圖5還顯示了通孔BNC布局的橫截面。內(nèi)接地和供電面與鍍通孔絕緣,以避免短路。圓柱孔帶有一定的電感。每個(gè)接地或供電面的鍍通孔都具有寄生電容。小間隔的大鍍通孔將抑制容易造成大組抗降的多余電容。圖6顯示具有60密爾孔和20密爾間隔的設(shè)計(jì)不佳通孔BNC的阻抗形態(tài),圖中顯示了鍍通孔的阻抗從75?跡線(xiàn)下降到40?。

圖5 BNC布局的橫截面圖

圖6 設(shè)計(jì)不佳的通孔BNC的阻抗形態(tài)

設(shè)計(jì)良好的BNC布局

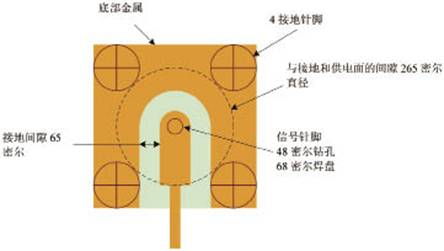

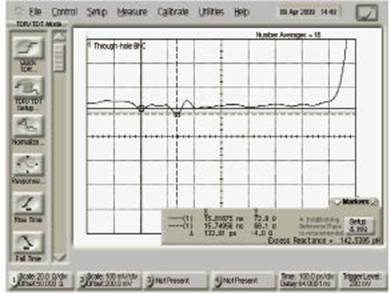

設(shè)計(jì)良好的BNC布局的目標(biāo)是避免BNC布局與連接到布局的跡線(xiàn)間產(chǎn)生過(guò)多的阻抗失配,可以遵循信號(hào)路徑查找板結(jié)構(gòu)變化可能導(dǎo)致的阻抗失配。時(shí)域反射計(jì)是能夠確定阻抗失配發(fā)生位置的儀器。可以使用電磁仿真器檢查板布局設(shè)計(jì)中的阻抗變化。如果阻抗過(guò)低,應(yīng)設(shè)計(jì)能夠抵消過(guò)多電容的板結(jié)構(gòu);如果阻抗過(guò)高,應(yīng)增加額外寄生電容使阻抗值接近目標(biāo)值。通過(guò)正確的電感和電容值,可以建立具有所需特征阻抗的通孔BNC布局。圖7顯示良好的通孔BNC布局示例,圖8顯示非常接近75?目標(biāo)值布局的阻抗。

圖7 良好通孔BNC布局的頂視圖

圖8 良好通孔BNC布局的阻抗形態(tài)

FPGA/SDI板的布局指導(dǎo)原則

FPGA/SDI板的數(shù)據(jù)傳輸率低于3Gb/s,信號(hào)轉(zhuǎn)換時(shí)間約為100微微秒。SDI板布局的難點(diǎn)不在于速度,而在于計(jì)劃一種布局策略以最大限度減少與75?SDI端口很多外部元件的阻抗失配,設(shè)計(jì)大BNC控制器的受控阻抗布局和實(shí)施支持75?和100?跡線(xiàn)的板堆疊。可以通過(guò)遵循以下這些簡(jiǎn)單的布局指導(dǎo)原則解決這些難點(diǎn):

?將跡線(xiàn)阻抗設(shè)為75?±10%、100?±10%

?使用最小的表面貼裝元件和最小的無(wú)源元件接合焊盤(pán)

?選擇能最大限度減少信號(hào)路徑上阻抗失配的跡線(xiàn)寬度

?選擇支持單獨(dú)接地基準(zhǔn)75?單端跡線(xiàn)和100?寬松耦合差分跡線(xiàn)的板堆疊

?使用表面貼裝陶瓷電容器和射頻信號(hào)電感器

?使對(duì)回波損耗有影響的元件(終端電阻器、阻抗平衡網(wǎng)絡(luò))盡可能接近集成電路針腳

?使用75?受控阻抗,設(shè)計(jì)良好的BNC布局

?保持互補(bǔ)信號(hào)發(fā)送的對(duì)稱(chēng)性

?均勻地傳送100?差分跡線(xiàn)(使跡線(xiàn)上的跡線(xiàn)寬度和跡線(xiàn)間隔保持均勻)

?避免陡彎,使用45度彎曲

?遵循信號(hào)路徑識(shí)別幾何變化,并預(yù)估相應(yīng)的阻抗變化

?使用整平面。如果需要采用凹凸地面抵消過(guò)多的寄生電容,應(yīng)謹(jǐn)慎使用;借助三維仿真工具決定布局

?使用最短的VCC和接地路徑,將針腳連接到通孔面

布局示例

圖9是美國(guó)國(guó)家半導(dǎo)體LMH03843Gbps/HD/SDSDI自適應(yīng)電纜均衡器、LMH0341SDI解串行器、LMH0340SDI串行器和FPGA(未顯示)的簡(jiǎn)要布局圖。本例使用圖4中顯示的堆疊。第2層(綠色顯示)是8密爾寬100?差分跡線(xiàn)的接地基準(zhǔn),它連接到LMH0384的輸出針腳SDO+和SDO-以及LMH0340和LMH0341的LVDS信號(hào)傳送線(xiàn)。第4層上的金屬島(藍(lán)色顯示)用作75?跡線(xiàn)的接地面。這兩個(gè)接地基準(zhǔn)使用設(shè)備DAP連接通過(guò)地面縫合到一起。

圖9 LMH0384、LMH0340和LMH0341的布局示例

交流耦合電容器C2緊鄰S(chǎng)DI+的輸入針腳。阻抗匹配網(wǎng)絡(luò)L1和R1通過(guò)C2盡可能地靠近輸入針腳SDI+。75?終端電阻器R2置于C2后方,以最大限度減小接線(xiàn)柱的影響。

這種設(shè)計(jì)使用0402尺寸元件,盡可能減少75?跡線(xiàn)的阻抗變化,75?跡線(xiàn)通過(guò)20密爾微帶線(xiàn)連接到第4層基準(zhǔn)。BNC使用的布局應(yīng)具有良好的信號(hào)發(fā)送,以實(shí)現(xiàn)低回波損耗。

圖9注釋如下:

注1-使用100?差分阻抗連接到第2層基準(zhǔn)的耦合跡線(xiàn)。

注2-第2和第4層的接地縫合。

注3-C4鄰近集成電路針腳。

注4-C2盡量靠近集成電路輸入針腳;R275?接收端子置于C2后方。

注5-L1、R1阻抗匹配網(wǎng)絡(luò)通過(guò)C2鄰近SDI+針腳。

注6-使用75?受控阻抗跡線(xiàn)連接到第4層基準(zhǔn)。使用0402元件。使用15-25密爾的跡線(xiàn)寬度,以最大限度減少較大元件焊盤(pán)導(dǎo)致的阻抗降。

注7-BNC使用75?受控阻抗布局。

總結(jié)

SDI板布局的難點(diǎn)在于設(shè)計(jì)一種方案,可以最大限度減少75?端口上很多外部元件引起的阻抗失配。使用75?微帶線(xiàn)以及與無(wú)源元件的接合焊盤(pán)尺寸相當(dāng)?shù)嫩E線(xiàn)寬度可以實(shí)現(xiàn)使阻抗失配降到最低的目標(biāo)。使用第二接地基準(zhǔn)就可以為連接到高針腳數(shù)FPGA的100?差分跡線(xiàn)靈活選擇較細(xì)跡線(xiàn)寬度。務(wù)必使用75?受控阻抗設(shè)計(jì)良好的BNC布局。建議在信號(hào)路徑上查找因布局結(jié)構(gòu)變化引起的阻抗變化,并設(shè)計(jì)一種方式可以抵消過(guò)多電感或電容以保持目標(biāo)特征阻抗值。通過(guò)遵循幾個(gè)簡(jiǎn)單的布局指導(dǎo)原則,可以設(shè)計(jì)符合SDI高信號(hào)保真要求的板,并實(shí)現(xiàn)高密度連接至FPGA。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論