隨著計算機技術和IC技術的不斷發展,使得數字化雷達視頻的存儲和遠距離傳輸在實際中得到越來越多的應用。

? ?? 1 視頻采集方案可行性分析

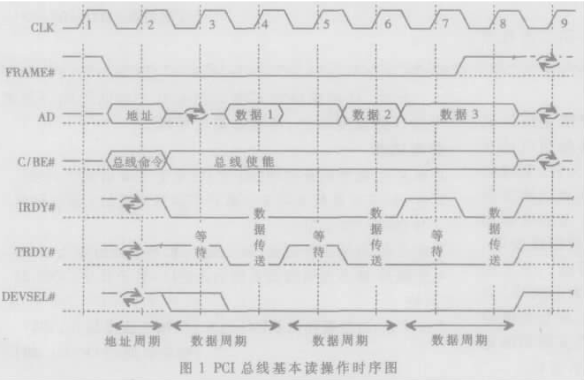

考慮:方案的設計主要考慮雷達視頻帶寬,即距離分辨率。在采集卡部分影響帶寬的數據瓶頸在于三方面:AD采樣量化、FIFO讀寫速度和PCI的DMA速度。

方案:硬件方案中采用TLC5540,最高采樣率可以達到40MHz,采樣深度為8bits;FIFO采用IDT72V36100,最高讀寫速度可以達到 133MHz;計算機PCI總線的數據帶寬可達到532Mbps,

實現:在實際中,由于受硬件環境,如主機板和CPU的影響,采用133Mbps的PCI卡。在 PC機部分數據瓶頸主要在于磁盤數據訪問速度,普通磁盤的數據訪問速度為40Mbps。若數字化雷達視頻帶寬達到30Mbps、量化深度為8bits,則 數據采樣率為30MHz,距離分辨率為300,000,000/2/30,000,000=5m,這樣的分辨率能夠滿足一般的導航和警戒雷達。若量化深度 降低,則距離分辨率將進一步提高。由以上分析可見所采用方案能夠滿足視頻的帶寬要求。

2系統實現的關鍵點

?

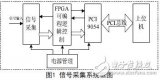

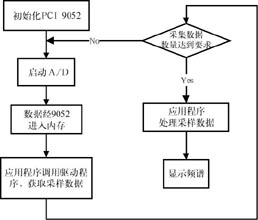

圖1 數字化視頻信號的流程

由底層到應用程序,雷達數據主要經過三個數據傳輸過程。(1)由數據采集卡至設備驅動,在數據采集卡中采用了雙FIFO技術,通過DMA單個 FIFO一次傳輸一幀雷達數據,即一個主脈沖正程的雷達回波信號。這里雙FIFO的作用在于信號的實時傳送,采集卡對FIFO1寫入時,驅動程序通過 DMA將FIFO2的數據傳入BLK2中,此為數據通道CH2,CH1為FIFO1與BLK2之間的通道。在系統中,CH1和CH2分時復用一個DMA通 道。(2)驅動程序和顯示應用模塊的數據交互,采用了乒乓存儲區的技術,如圖1所示。當DMA占用BLK1時,顯示應用程序將BLK2中的雷達視頻數據讀 入,進行數據合并、抗異步干擾處理,并實時顯示。(3)驅動模塊與數據存儲模塊的數據交互,這個交互過程和上面相似,不過,對于BLK1、BLK2的訪問 都要和顯示應用程序分時進行。

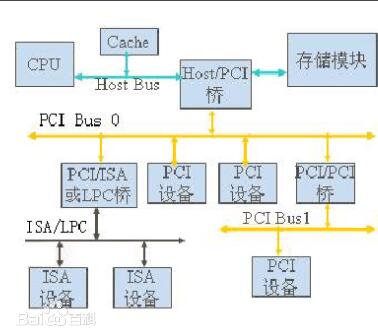

在時序上,各個數據通道的詳細分時關系如圖2所示。

?

圖2 數字化雷達視頻信號在存儲器中的時序

如圖2所示,在第N+1個主脈沖回波內,數據采集卡將AD變換之后實時數字雷達信號寫入FIFO2中(數據排隊),通過DMA將FIFO2的數據傳入BLK1(CH1),同時將BLK2的數據傳入顯示應用模塊(CH4)和數據存儲模塊(CH6)。

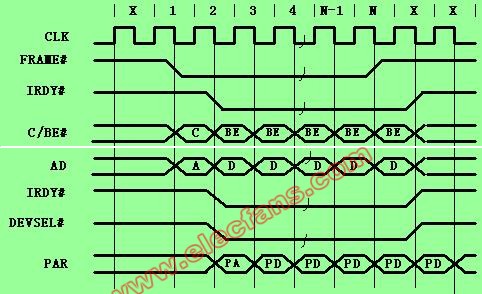

由于在CH1~CH6中傳送的數字化雷達視頻數據都有特定的時序,且都是實時數據,故通道中的數據幀格式相對簡單,幀頭沒有同步頭和差錯控制。幀格式如圖3所示。

?

圖3 數字化視頻信息的幀格式

在幀頭高字位給出13位方位碼,同時預留出高3位,用以傳輸方位碼的特征信息,如正北信號、扇區信號和圖元信號,這些信號在硬件(數據采集卡) 中容易實現,能節省軟件的處理時間。在目前的系統中,這些特征信息還用不到,在具體到雷達數據的分析時,這些信息能起到很重要的作用。幀頭的低字位給出距 離信息,包括低4位的量程信息和高12位的距離采樣深度。

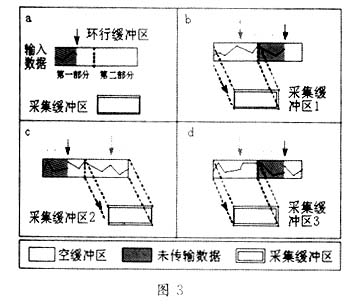

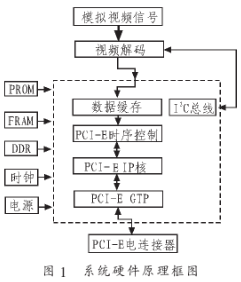

2.2 數據采集卡的實現

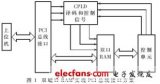

雷達數據采集卡在本系統中起到基石的作用,它將由雷達接收機送下來的模擬視頻信號采樣量化,經過量程歸并后,相對于主脈沖對齊,然后加入幀頭信息,通過DMA傳輸給驅動程序。數據采集卡的功能結構如圖4所示。

?

圖4 數據采集卡結構圖

數據采集卡共有七個主要模塊:PCI總線控制模塊采用通用芯片PCI9080橋接本地總線和PCI總線;本地總線控制模塊CM負責卡內控制信號 和狀態信號的交互;SYN為外部方位碼和主脈沖的同步模塊,它根據主脈沖產生AD的采樣時鐘和量程歸并時鐘;AD采用TLC5540對雷達視頻信號進行采 樣量化;MERGE模塊為量程歸并模塊;PACK模塊將由SYN和MERGE模塊送來的方位碼和視頻數據打包成幀,并排隊送入FIFO;FIFO模塊將幀 結構的雷達數據通過DMA傳給驅動程序。在硬件的實現上采用了可編程器件CPLD。

2.3用CPLD實現雙FIFO控制

采集卡中數字化雷達視頻信號在推入FIFO之前要經過打包成幀的處理,這個處理過程通過一片EPM7128SLC84-10實現。其內部的控制邏輯如圖5所示。

?

圖5 數據打包成幀的邏輯結構

圖3中,數據幀的幀頭包含方位信息和數據量以及量程信息,這一部分的處理在圖5的head模塊中實現;視頻量化深度為8位,并行推入FIFO為 16位,這就需要將數據移位合并,這個過程在body模塊中通過兩個8位D觸發器陣列實現;在主脈沖前沿需要將幀頭信息插入,這個邏輯控制通過clk模塊 中的一個狀態機實現。狀態機的轉移圖如圖6所示。

?

圖6 數據幀的時序狀態控制

狀態機的時鐘為數據推入時鐘d_merge_clk,狀態轉移通過主脈沖mainpulse_syn和幀數據時鐘d_pack_clk控制,其 中d_pack_clk通過d_merge_clk二分頻得到。通過mainpulse的上升沿判斷進入新的一幀數據,通過d_pack_clk的前兩個 時鐘周期(head_sel=1,2)插入幀頭。狀態機的邏輯仿真如圖7所示。

對于雙FIFO的乒乓操作,也是通過一個狀態機實現的。狀態機轉移圖如圖8所示。

狀態機的時鐘為d_merge_clk,通過主脈沖mainpulse_syn控制狀態轉移,對FIFO1和FIFO2進行輪詢操作。狀態機的邏輯仿真如圖9所示。

?

圖7 數據幀的時序狀態機的邏輯仿真

?

圖8 雙FIFO的兵乓操作狀態控制

?

圖9 雙FIFO的乒乓操作狀態控制仿真

本文論證了雷達視頻實時數據采集的實用性和可行性,并提出了一套切實可行的方案。此項技術的推廣,無疑將提高雷達視頻終端的兼容性、可移植性和通用性。

電子發燒友App

電子發燒友App

評論