接口信號(hào)能工作在8Gbps及以上速率,由于速率很高,PCB布線設(shè)計(jì)要求會(huì)更嚴(yán)格,在前幾篇關(guān)于PCB布線內(nèi)容的基礎(chǔ)上,還需要根據(jù)本篇內(nèi)容的要求來(lái)進(jìn)行PCB布線設(shè)計(jì)。 高速信號(hào)布線時(shí)盡量少打孔

2023-08-02 08:41:11 1434

1434

高速PCB布線實(shí)踐指南詳細(xì)介紹(例題分析)

雖然印制電路板(PCB)布線在高速電路中具有關(guān)鍵的作用,但它往往是電路設(shè)計(jì)過(guò)程的最后幾個(gè)步驟之一。高速PCB布線有很多

2009-12-04 09:30:59 819

819 高速電路PCB電源布線技巧

PCB設(shè)計(jì)來(lái)說(shuō)電源處理好壞直接關(guān)系到整個(gè)電路板的性能。下面我們分析一下高速電路PCB板的電源布線需要注意的地方和技

2010-03-21 18:29:39 2743

2743

PCB布線后檢查工作也很必須,那么如何對(duì)PCB設(shè)計(jì)中布線進(jìn)行檢查,為后來(lái)的PCB設(shè)計(jì)、電路設(shè)計(jì)鋪好“路”呢?本文會(huì)從PCB設(shè)計(jì)中的各種特性來(lái)教你如何完成PCB布線后的檢查工作,做好最后的把關(guān)工作。##至少應(yīng)該在印制電路板三個(gè)邊沿邊緣1英寸的范圍內(nèi)支撐。

2014-01-10 09:48:17 8007

8007

手術(shù)很重要,術(shù)后恢復(fù)也必不可少!各種PCB布線完成之后,就ok了嗎?很顯然,不是!PCB布線后檢查工作也很必須,那么如何對(duì)PCB設(shè)計(jì)中布線進(jìn)行檢查,為后來(lái)的PCB設(shè)計(jì)、電路設(shè)計(jì)鋪好“路”呢?

2014-09-26 10:50:21 1857

1857 雖然印制電路板(PCB)布線在高速電路中具有關(guān)鍵的作用,但它往往是電路設(shè)計(jì)過(guò)程的最后幾個(gè)步驟之一。高速PCB布線有很多方面的問(wèn)題,關(guān)于這個(gè)題目已有人撰寫(xiě)了大量的文獻(xiàn)。本文主要從實(shí)踐的角度來(lái)探討高速

2022-08-14 11:35:18 757

757 高速電路器件管腳間的引線彎折越少越好。高速信號(hào)布線電路布線的引線最好采用全直線,需要轉(zhuǎn)折,可用45°折線或圓弧轉(zhuǎn)折,這種要求在低頻電路中僅僅用于提高鋼箔的固著強(qiáng)度,而在高速電路中,滿足這一要求卻可以減少高速信號(hào)對(duì)外的發(fā)射和相互間的耦合,減少信號(hào)的輻射和反射。

2023-04-12 11:33:46 961

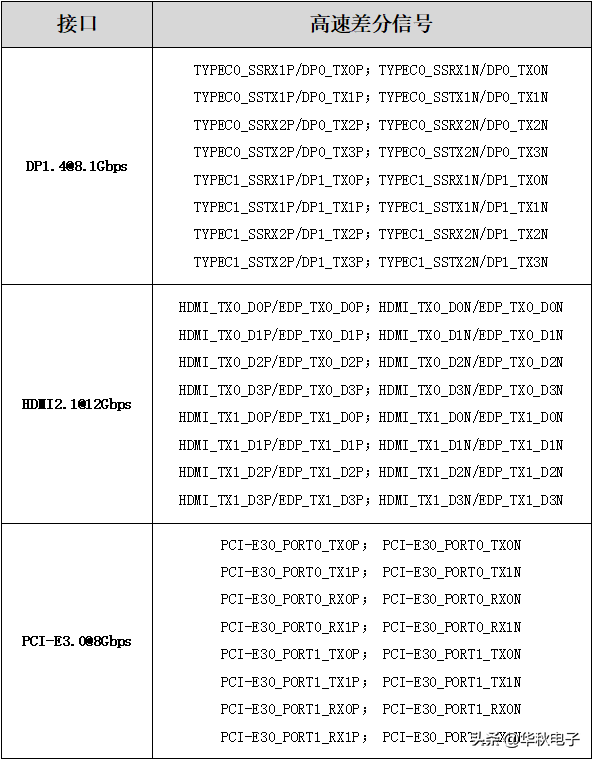

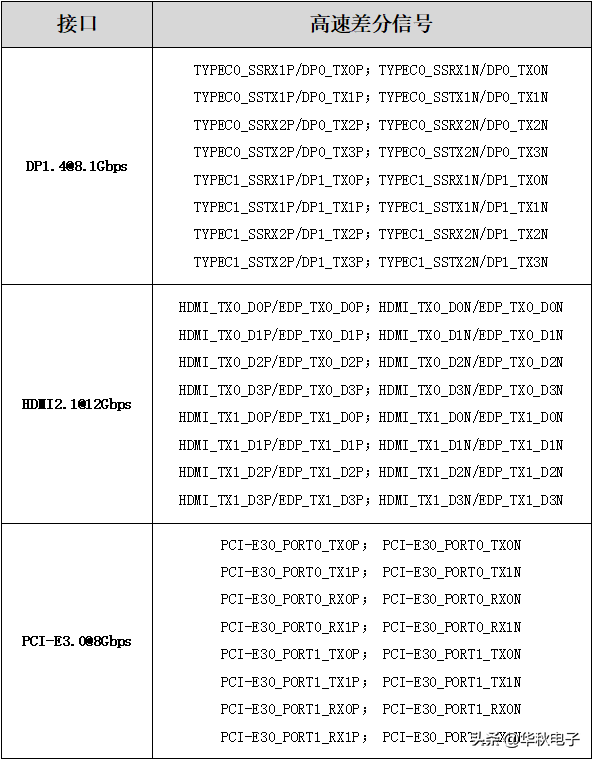

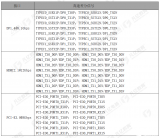

961 如下表所示,接口信號(hào)能工作在8Gbps及以上速率,由于速率很高,PCB布線設(shè)計(jì)要求會(huì)更嚴(yán)格,在前幾篇關(guān)于PCB布線內(nèi)容的基礎(chǔ)上,還需要根據(jù)本篇內(nèi)容的要求來(lái)進(jìn)行PCB布線設(shè)計(jì)。 高速信號(hào)布線時(shí)盡量

2023-08-01 18:10:06 1266

1266

如下表所示,接口信號(hào)能工作在8Gbps及以上速率,由于速率很高,PCB布線設(shè)計(jì)要求會(huì)更嚴(yán)格,在前幾篇關(guān)于PCB布線內(nèi)容的基礎(chǔ)上,還需要根據(jù)本篇內(nèi)容的要求來(lái)進(jìn)行PCB布線設(shè)計(jì)。 高速信號(hào)布線時(shí)盡量

2023-08-03 17:13:35 645

645

如下表所示,接口信號(hào)能工作在8Gbps及以上速率,由于速率很高,PCB布線設(shè)計(jì)要求會(huì)更嚴(yán)格,在前幾篇關(guān)于PCB布線內(nèi)容的基礎(chǔ)上,還需要根據(jù)本篇內(nèi)容的要求來(lái)進(jìn)行PCB布線設(shè)計(jì)。

高速信號(hào)布線時(shí)盡量少

2023-08-01 18:02:03

盲目的拉線,拉了也是白拉!有些小伙伴在pcb布線時(shí),板子到手就是干,由于前期分析工作做的不足或者沒(méi)做,導(dǎo)致后期處理時(shí)舉步維艱。比如電源線、雜線拉完了,卻漏掉一組重要的信號(hào)線,導(dǎo)致這組線沒(méi)辦法同組同層

2022-03-23 17:55:19

等三個(gè)方面來(lái)闡述。1.直角走線 直角走線一般是PCB布線中要求盡量避免的情況,也幾乎成為衡量布線好壞的標(biāo)準(zhǔn)之一,那么直角走線究竟會(huì)對(duì)信號(hào)傳輸產(chǎn)生多大的影響呢?從原理上說(shuō),直角走線會(huì)使傳輸線的線寬

2012-07-21 14:22:45

確保信號(hào)完整性的一個(gè)重要部分是信號(hào)走線的物理布線。PCB設(shè)計(jì)人員經(jīng)常承受壓力,不僅要縮小設(shè)計(jì),還要保持信號(hào)完整性。找到平衡點(diǎn)就是要知道問(wèn)題可能發(fā)生的位置以及在系統(tǒng)出現(xiàn)故障之前可以推送信封的距離

2023-04-12 15:20:37

)進(jìn)行手動(dòng)布線并加以固定,可以形成自動(dòng)布線時(shí)可依據(jù)的路徑。 無(wú)論關(guān)鍵信號(hào)的數(shù)量有多少,首先對(duì)這些信號(hào)進(jìn)行布線,手動(dòng)布線或結(jié)合自動(dòng)布線工具均可。關(guān)鍵信號(hào)通常必須通過(guò)精心的電路設(shè)計(jì)才能達(dá)到期望的性能。布線完成

2022-04-18 15:22:08

,可以形成自動(dòng)布線時(shí)可依據(jù)的路徑。無(wú)論關(guān)鍵信號(hào)的數(shù)量有多少,首先對(duì)這些信號(hào)進(jìn)行布線,手動(dòng)布線或結(jié)合自動(dòng)布線工具均可。關(guān)鍵信號(hào)通常必須通過(guò)精心的電路設(shè)計(jì)才能達(dá)到期望的性能。布線完成 后,再由有關(guān)的工程人員

2021-03-31 06:00:00

15條高速PCB布線經(jīng)驗(yàn)分享

2021-01-29 06:10:51

在高速PCB電路板的設(shè)計(jì)和制造過(guò)程中,工程師需要從布線、元件設(shè)置等方面入手,以確保這一PCB板具有良好的信號(hào)傳輸完整性。在今天的文章中,我們將會(huì)為各位新人工程師們介紹PCB信號(hào)完整性設(shè)計(jì)中常

2018-11-27 09:57:50

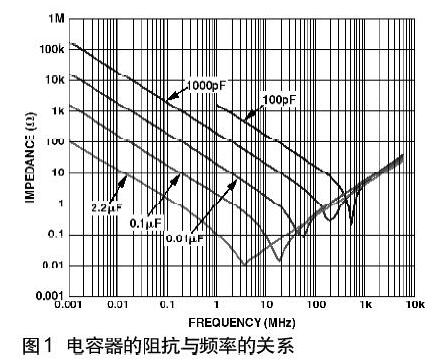

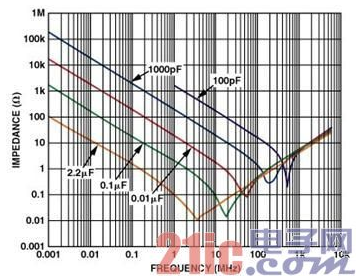

`高速PCB板的電源布線設(shè)計(jì)隨著集成電路工藝和集成度的不斷提高,集成電路的工作電壓越來(lái)越低,速度越來(lái)越快。進(jìn)入新世紀(jì)后,CPU和網(wǎng)絡(luò)都邁入了GHZ的時(shí)代,這對(duì)于PCB板的設(shè)計(jì)提出了更高的要求。本文正是基于這種背景下,對(duì)高速PCB設(shè)計(jì)中最重要的環(huán)節(jié)之一——電源的合理布局布線進(jìn)行分析和探討。`

2009-12-09 13:58:28

PCB(印制電路板)布線在高速電路中具有關(guān)鍵作用,那么高速PCB的布線需要考慮哪些事項(xiàng)呢? 這個(gè)問(wèn)題大家考慮過(guò)嗎?

2019-08-02 06:46:56

各因素,做出全面的折衷考慮;既滿足設(shè)計(jì)要求,又降低設(shè)計(jì)復(fù)雜度。本文從PCB的布線、布局及高速PCB的設(shè)計(jì)三個(gè)部分進(jìn)行分析,介紹高速PCB的可控性與電磁兼容性設(shè)計(jì)。

2019-07-25 08:14:06

本帖最后由 eehome 于 2013-1-5 10:01 編輯

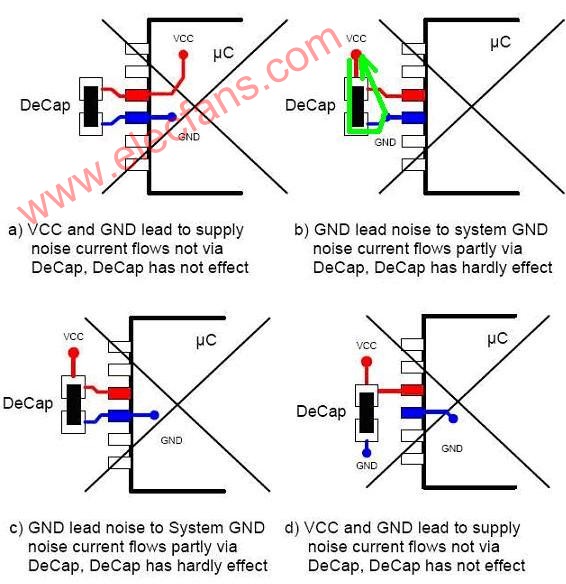

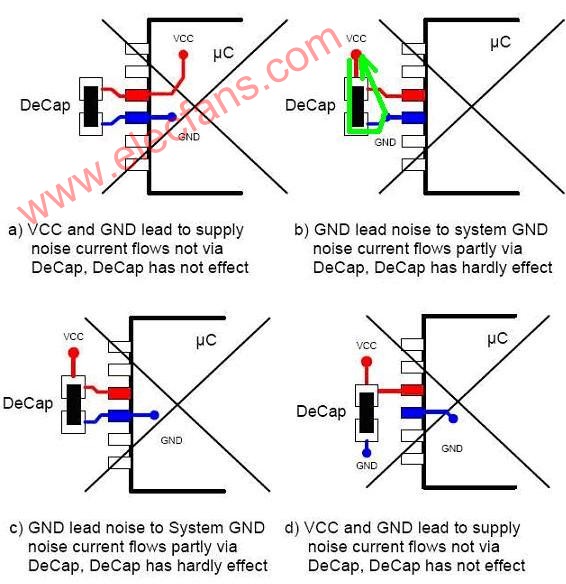

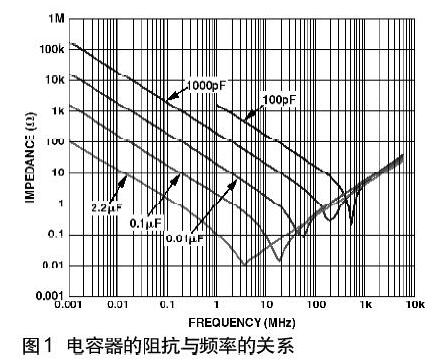

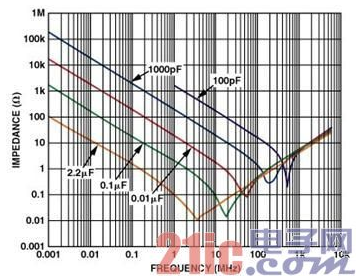

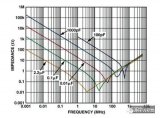

高速PCB板信號(hào)接地設(shè)計(jì)中存在接地噪聲及電磁輻射等問(wèn)題,提出了高速PCB接地模型,并從PCB設(shè)計(jì)中布線策略的分析和去耦電容的使用等幾個(gè)方面討論了解決高速PCB板的接地噪聲和電磁輻射問(wèn)題的方法。

2012-03-31 14:31:52

效應(yīng)和信號(hào)的完整性問(wèn)題;而當(dāng)系統(tǒng)時(shí)鐘達(dá)到120MHz時(shí),除非使用高速電路設(shè)計(jì)知識(shí),否則基于傳統(tǒng)方法設(shè)計(jì)的PCB將無(wú)法工作。因此,高速電路設(shè)計(jì)技術(shù)已經(jīng)成為電子系統(tǒng)設(shè)計(jì)師必須采取的設(shè)計(jì)手段。只有通過(guò)

2015-05-05 09:30:27

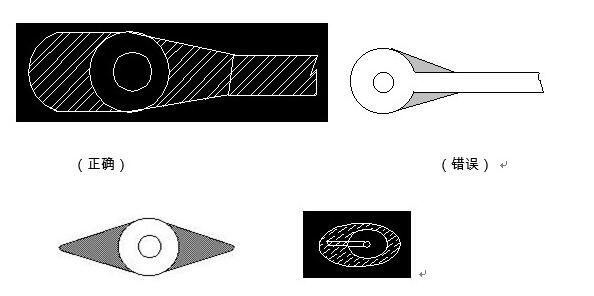

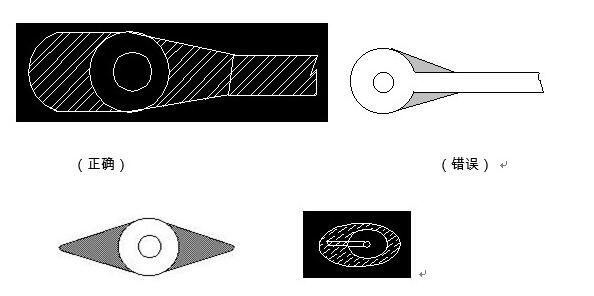

高速PCB設(shè)計(jì)中常規(guī)PCB布線,有以下基本要求:(1)QFP、SOP等封裝的矩形焊盤(pán)出線,應(yīng)從PIN中心引出(一般采用鋪shape)(2)布線到板邊的距離不小于20MIL。(3)金屬外殼器件下

2017-02-16 15:06:01

` 本帖最后由 飛翔的烏龜005 于 2017-2-10 10:43 編輯

高速PCB設(shè)計(jì)中常規(guī)PCB布線,有以下基本要求:(1)QFP、SOP等封裝的矩形焊盤(pán)出線,應(yīng)從PIN中心引出(一般采用

2017-02-10 10:42:11

的平面層,回流路徑分布在信號(hào)周?chē)鱾€(gè)地和電源上,仿真時(shí)需要使用3D場(chǎng)提取工具分析,這時(shí)候打彎布線和過(guò)孔的回流需要具體分析;高速數(shù)字電路分析一般只處理有完整平面層的多層PCB,使用2D場(chǎng)提取分析,只考慮在

2012-10-17 15:59:48

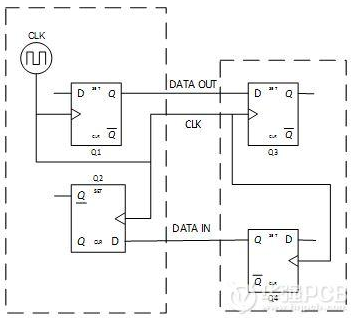

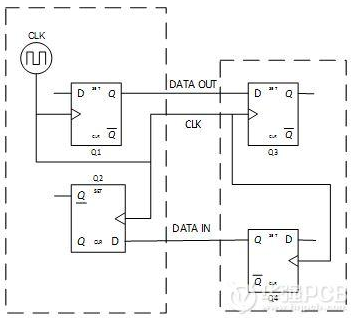

本期講解PCB設(shè)計(jì)中高速信號(hào)關(guān)鍵信號(hào)的布線要求。一、時(shí)鐘信號(hào)布線要求在數(shù)字電路設(shè)計(jì)中,時(shí)鐘信號(hào)是一種在高態(tài)與低態(tài)之間振蕩的信號(hào),決定著電路的性能。時(shí)鐘電路在數(shù)字電路中點(diǎn)有重要地位,同時(shí)又是產(chǎn)生

2017-10-19 14:25:36

高速PCB設(shè)計(jì)指南之(一~八 )目錄2001/11/21CHENZHI/LEGENDSILICON一、1、PCB布線2、PCB布局3、高速PCB設(shè)計(jì)二、1、高密度(HD)電路設(shè)計(jì)2、抗干擾技術(shù)3

2012-07-13 16:18:40

高速信號(hào)PCB布線中降低寄生電感的具體措施

2021-03-08 08:49:46

,將近20% 的設(shè)計(jì)主頻超過(guò)120MHz。 當(dāng)系統(tǒng)工作在50MHz時(shí),將產(chǎn)生傳輸線效應(yīng)和信號(hào)的完整性問(wèn)題;而當(dāng)系統(tǒng)時(shí)鐘達(dá)到120MHz時(shí),除非使用高速電路設(shè)計(jì)知識(shí),否則基于傳統(tǒng)方法設(shè)計(jì)的PCB將無(wú)法工作

2012-09-19 17:08:44

。本篇介紹了高速數(shù)字硬件電路設(shè)計(jì)中信號(hào)完整性在通常設(shè)計(jì)的影響。這包括特征阻抗控制、終端匹配、電源和地平面、信號(hào)布線和串?dāng)_等問(wèn)題。掌握這些知識(shí),對(duì)一個(gè)數(shù)字電路設(shè)計(jì)者而言,可以在電路設(shè)計(jì)的早期,就注意到潛在

2009-10-14 09:32:02

高速數(shù)字硬件電路設(shè)計(jì)中信號(hào)完整性在通常設(shè)計(jì)的影響是什么?高速電路設(shè)計(jì)中信號(hào)完整性面臨的挑戰(zhàn)有哪些?怎么處理?

2021-04-22 06:26:55

高速PCB設(shè)計(jì)中的信號(hào)完整性概念以及破壞信號(hào)完整性的原因高速電路設(shè)計(jì)中反射和串?dāng)_的形成原因

2021-04-27 06:57:21

高速電路設(shè)計(jì)學(xué)習(xí) 一、PCB設(shè)計(jì)時(shí)高速信號(hào)和低速信號(hào)區(qū)分 在高速PCB電路設(shè)計(jì)過(guò)程中,經(jīng)常會(huì)遇到信號(hào)完整性問(wèn)題,導(dǎo)致信號(hào)傳輸質(zhì)量不佳甚至出錯(cuò)。那么如何區(qū)分高速信號(hào)和普通信號(hào)呢?很多人覺(jué)得信號(hào)頻率高

2020-12-21 09:23:34

!添加客服即可直接購(gòu)買(mǎi)!打開(kāi)下方鏈接加客服領(lǐng)取,暗號(hào):1-13部http://zyunying.zhangfeidz.com?id=20承諾:只需1.99元下單,無(wú)任何套路。高速ADC PCB布局布線技巧,需要完整版的朋友可以下載附件保存資料~

2021-12-28 13:35:51

影響高速信號(hào)鏈設(shè)計(jì)性能的機(jī)制是什么?高速ADC設(shè)計(jì)中的PCB布局布線技巧有哪些?

2021-04-21 06:29:52

考慮?第三篇 高速PCB設(shè)計(jì)(一)、電子系統(tǒng)設(shè)計(jì)所面臨的挑戰(zhàn)隨著系統(tǒng)設(shè)計(jì)復(fù)雜性和集成度的大規(guī)模提高,電子系統(tǒng)設(shè)計(jì)師們正在從事100MHZ以上的電路設(shè)計(jì),總線的工作頻率也已經(jīng)達(dá)到或者超過(guò)50MHZ,有的

2010-02-10 12:47:02

等高頻信號(hào)線都是要求盡可能的走線越短越好。 3、高速電子器件管腳間的引線彎折越少越好 高頻電路布線的引線最好采用全直線,需要轉(zhuǎn)折,可用45度折線或者圓弧轉(zhuǎn)折,這種要求在低頻電路中僅僅用于提高銅箔

2017-01-20 11:44:22

電路設(shè)計(jì),尤其是現(xiàn)代高速電路系統(tǒng)的設(shè)計(jì),是一個(gè)隨著電子技術(shù)的發(fā)展而日新月異的工作,具有很強(qiáng)的趣味性,也具有相當(dāng)?shù)奶魬?zhàn)性。《高速電路設(shè)計(jì)與仿真分析:Cadence實(shí)例設(shè)計(jì)詳解》的目的是要使電子系

2020-01-06 14:03:29

本帖最后由 張飛電子學(xué)院郭嘉 于 2021-6-17 11:39 編輯

從分層、布局及布線三方面,詳解EMC的PCB設(shè)計(jì)技術(shù)除了元器件的選擇和電路設(shè)計(jì)之外,良好的印制電路板(PCB)設(shè)計(jì)在

2021-06-17 11:37:10

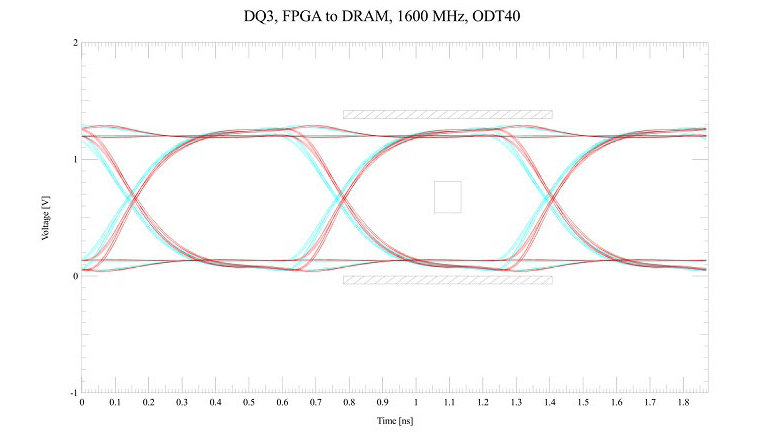

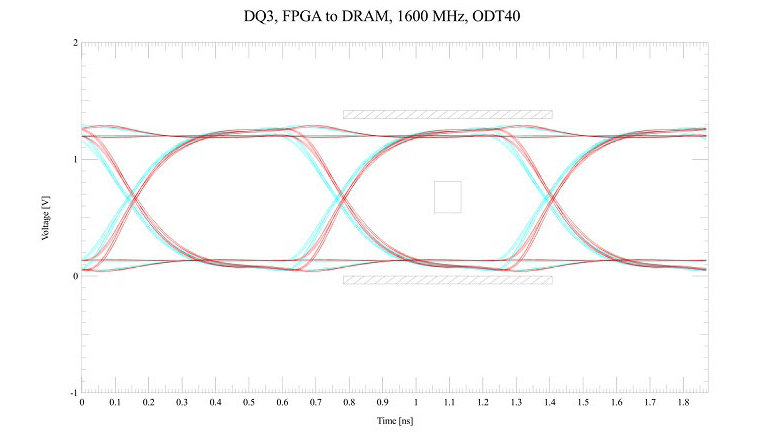

PCB板設(shè)計(jì)之前,首先建立高速數(shù)字信號(hào)傳輸?shù)?b class="flag-6" style="color: red">信號(hào)完整性模型。 根據(jù)SI模型對(duì)信號(hào)完整性問(wèn)題進(jìn)行一系列的預(yù)分析,根據(jù)仿真計(jì)算的結(jié)果選擇合適的元器件類(lèi)型、參數(shù)和電路拓?fù)浣Y(jié)構(gòu),作為電路設(shè)計(jì)的依據(jù)。 在

2018-08-29 16:28:48

PCB板設(shè)計(jì)之前,首先建立高速數(shù)字信號(hào)傳輸?shù)?b class="flag-6" style="color: red">信號(hào)完整性模型。 根據(jù)SI模型對(duì)信號(hào)完整性問(wèn)題進(jìn)行一系列的預(yù)分析,根據(jù)仿真計(jì)算的結(jié)果選擇合適的元器件類(lèi)型、參數(shù)和電路拓?fù)浣Y(jié)構(gòu),作為電路設(shè)計(jì)的依據(jù)。 在

2008-06-14 09:14:27

印刷電路板(PCB)布線在高速電路中具有關(guān)鍵的作用,但它往往只是電路設(shè)計(jì)過(guò)程的最后幾個(gè)步驟之一。高速PCB布線有很多方面的問(wèn)題,關(guān)于這個(gè)主題已有大量的文獻(xiàn)可供參考。本文主要從實(shí)踐的角度來(lái)探討高速電路的布線

2018-10-12 10:22:31

開(kāi)關(guān)電源 PCB電路設(shè)計(jì)中的接地與布線.pdf非常適合開(kāi)關(guān)電源設(shè)計(jì)人員參閱資料來(lái)源于網(wǎng)絡(luò)資源

2020-07-31 17:25:26

現(xiàn)承接電路設(shè)計(jì)。pcb布線等活。。有意者聯(lián)系qq416594931.。。價(jià)格公道,質(zhì)量絕對(duì)可靠。服務(wù)絕對(duì)熱情。

2014-03-03 09:54:59

對(duì)于高速信號(hào),pcb的設(shè)計(jì)要求會(huì)更多,因?yàn)?b class="flag-6" style="color: red">高速信號(hào)很容易收到其他外在因素的干擾,導(dǎo)致實(shí)際設(shè)計(jì)出來(lái)的東西和原本預(yù)期的效果相差很多。 所以在高速信號(hào)pcb設(shè)計(jì)中,需要提前考慮好整體的布局布線,良好

2023-04-12 14:22:25

非常經(jīng)典的實(shí)用資料PCB電路設(shè)計(jì)中的接地與布線資料來(lái)自網(wǎng)絡(luò)資源

2020-08-20 22:44:11

數(shù)字電路中,為了提高信號(hào)質(zhì)量,降低布線難度,一般采用多層板,分配專門(mén)的電源層,地層。 56、在布局、布線中如何處理才能保證 50M 以上信號(hào)的穩(wěn)定性? 高速數(shù)字信號(hào)布線,關(guān)鍵是減小傳輸線對(duì)信號(hào)質(zhì)量

2018-09-20 10:38:32

,其布線對(duì)整個(gè)設(shè)計(jì)至關(guān)重要!【第一招】多層板布線高頻電路往往集成度較高,布線密度大,采用多層板既是布線所必須,也是降低干擾的有效手段。在PCB Layout階段,合理的選擇一定層數(shù)的印制板尺寸,能

2017-11-15 12:09:58

,其布線對(duì)整個(gè)設(shè)計(jì)至關(guān)重要! 【第一招】多層板布線 高頻電路往往集成度較高,布線密度大,采用多層板既是布線所必須,也是降低干擾的有效手段。在PCB Layout階段,合理的選擇一定層數(shù)的印制板尺寸

2018-09-19 15:54:50

越高,這就要求我們?cè)谶M(jìn)行PCB Layout時(shí),除了選擇合適的層數(shù)的PCB板,還需要進(jìn)行合理的元器件布局規(guī)劃,并采用正確的布線規(guī)則來(lái)完成設(shè)計(jì)。【第二招】高速電子器件管腳間的引線彎折越少越好高頻電路布線

2019-09-05 03:52:48

高速PCB板的電源布線設(shè)計(jì):本文分析討論了高速PCB板上由于高頻信號(hào)干擾和走線寬度的減小而產(chǎn)生的電源噪聲和壓降,并提出了高速PCB的電源模型,采用電源總線網(wǎng)絡(luò)布線,選取合適

2009-03-24 14:08:40 0

0 本文針對(duì)高速PCB板信號(hào)接地設(shè)計(jì)中存在接地噪聲及電磁輻射等問(wèn)題,提出了高速PCB接地模型,并從PCB設(shè)計(jì)中布線策略的分析和去耦電容的使用等幾個(gè)方面討論了解決高速PCB板的接地噪聲

2009-12-08 14:53:23 63

63 PCB布線規(guī)則之PCI卡篇

PCI卡的布線比較講究,這是PCI信號(hào)的特點(diǎn)決定的。在常規(guī)性的高頻數(shù)字電路設(shè)計(jì)中我們總是力求避免阻抗

2009-11-18 14:01:57 1110

1110 PCB布線規(guī)則詳解解說(shuō)

電源、地線的處理 既使在整個(gè)PCB板中的布線完成得都很好,但由于電源、 地線的考慮不周到而引起的干擾,會(huì)

2009-11-24 13:14:03 1759

1759 在當(dāng)今的工業(yè)領(lǐng)域,系統(tǒng)電路板布局已成為設(shè)計(jì)本身的一個(gè)組成部分。因此,設(shè)計(jì)工程師必須了解影響高速信號(hào)鏈設(shè)計(jì)性能的機(jī)制。在高速模擬信號(hào)鏈設(shè)計(jì)中,印刷電路板(PCB)布局布線

2012-04-24 14:09:37 0

0 電機(jī)控制與驅(qū)動(dòng)電路設(shè)計(jì)中模擬信號(hào)隔離技巧詳解

2016-01-06 17:28:45 0

0 高速PCB板的電源布線設(shè)計(jì),有需要的下來(lái)看看。

2016-02-22 16:14:48 31

31 介紹數(shù)字電路PCB布線設(shè)計(jì)考慮指南,信號(hào)線阻抗匹配指南等電路設(shè)計(jì)知識(shí)。

2016-02-24 10:52:21 19

19 本篇介紹了高速數(shù)字硬件電路設(shè)計(jì)信號(hào)完整性在通常設(shè)計(jì)的影響。這包括特征阻抗控制、終端匹配、電源和地平面、信號(hào)布線和串?dāng)_等問(wèn)題。

2016-05-13 14:06:16 0

0 PCB電路設(shè)計(jì)中布線的EMC分析,下來(lái)看看

2016-07-29 19:05:18 0

0 隨著封裝密度的增加和工作頻率的提高,MCM電路設(shè)計(jì)中的信號(hào)完整性問(wèn)題已不容忽視。本文以檢測(cè)器電路為例,首先利用APD軟件實(shí)現(xiàn)電路的布局布線設(shè)計(jì),然后結(jié)合信號(hào)完整性分析,對(duì)電路布局布線結(jié)構(gòu)進(jìn)行反復(fù)

2018-02-10 16:43:55 1948

1948 設(shè)計(jì)PCB時(shí),往往很想使用自動(dòng)布線。通常,純數(shù)字的電路板(尤其信號(hào)電平比較低,電路密度比較小時(shí))采用自動(dòng)布線是沒(méi)有問(wèn)題的。但是,在設(shè)計(jì)模擬、混合信號(hào)或高速電路板時(shí),如果采用布線軟件的自動(dòng)布線工具

2018-05-04 15:50:21 5849

5849

本文主要詳解PCB布線、焊盤(pán)及敷銅的設(shè)計(jì)方法,首先從pcb布線的走向、布線的形式、電源線與地線的布線要求介紹了PCB布線的設(shè)計(jì),其次從焊盤(pán)與孔徑、PCB設(shè)計(jì)中焊盤(pán)的形狀和尺寸設(shè)計(jì)標(biāo)準(zhǔn)、PCB制造工藝對(duì)焊盤(pán)的要求介紹了PCB焊盤(pán)的設(shè)計(jì),最后從pcb覆銅技巧及設(shè)置介紹了pcb覆銅設(shè)計(jì),具體的跟隨小編來(lái)了解一下。

2018-05-23 15:31:05 25653

25653

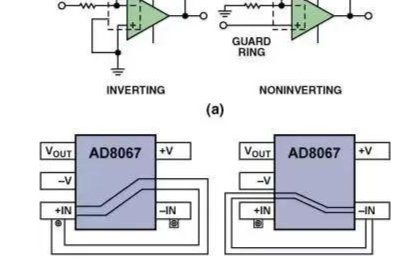

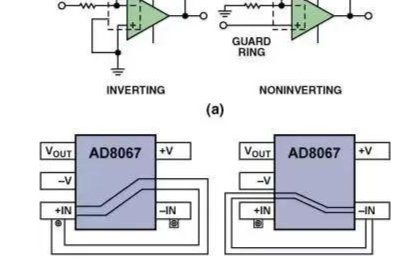

雖然這里主要針對(duì)與高速運(yùn)算放大器有關(guān)的電路,但是這里所討論的問(wèn)題和方法對(duì)用于大多數(shù)其它高速模擬電路的布線是普遍適用的。當(dāng)運(yùn)算放大器工作在很高的射頻(RF)頻段時(shí),電路的性能很大程度上取決于PCB布線

2019-05-29 14:18:13 588

588

EDA技術(shù)已經(jīng)研發(fā)出一整套高速PCB和電路板級(jí)系統(tǒng)的設(shè)計(jì)分析工具和方法學(xué),這些技術(shù)涵蓋高速電路設(shè)計(jì)分析的方方面面:靜態(tài)時(shí)序分析、信號(hào)完整性分析、EMI/EMC設(shè)計(jì)、地彈反射分析、功率分析以及高速布線

2019-05-22 15:15:22 773

773 高速電路設(shè)計(jì)領(lǐng)域,關(guān)于布線有一種幾乎是公理的認(rèn)識(shí),即“等長(zhǎng)”走線,認(rèn)為走線只要等長(zhǎng)就一定滿足時(shí)序需求,就不會(huì)存在時(shí)序問(wèn)題。本文對(duì)常用高速器件的互連時(shí)序建立模型,并給出一般性的時(shí)序分析公式。為體現(xiàn)具體問(wèn)題具體分析的原則,避免將公式當(dāng)成萬(wàn)能公式,文中給出了MII 、RMII、RGMII和SPI的實(shí)例分析。

2019-05-16 14:42:37 2782

2782

PCB設(shè)計(jì)工程師在設(shè)計(jì)PCB時(shí),往往很想使用自動(dòng)布線。通常,純數(shù)字的電路板(尤其信號(hào)電平比較低,電路密度比較小時(shí))采用自動(dòng)布線是沒(méi)有問(wèn)題的。但是,在設(shè)計(jì)模擬、混合信號(hào)或高速電路板時(shí),如果采用PCB設(shè)計(jì)軟件的自動(dòng)布線工具,可能會(huì)出現(xiàn)一些問(wèn)題,甚至很可能帶來(lái)嚴(yán)重的電路性能問(wèn)題。

2019-05-07 15:07:18 27786

27786 在PCB布線規(guī)則中,有一條“關(guān)鍵信號(hào)線優(yōu)先”的原則,即電源、摸擬信號(hào)、高速信號(hào)、時(shí)鐘信號(hào)、差分信號(hào)和同步信號(hào)等關(guān)鍵信號(hào)優(yōu)先布線。

2020-01-01 17:12:00 2772

2772 在高速PCB電路板的設(shè)計(jì)和制造過(guò)程中,工程師需要從布線、元件設(shè)置等方面入手,以確保這一PCB板具有良好的信號(hào)傳輸完整性。

2019-08-30 17:45:29 1095

1095 當(dāng)運(yùn)算放大器工作在很高的射頻(RF)頻段時(shí),電路的性能很大程度上取決于PCB布線。“圖紙”上看起來(lái)很好的高性能電路設(shè)計(jì),如果由于布線時(shí)粗心馬虎受到影響,最后只能得到普通的性能。在整個(gè)布線過(guò)程中預(yù)先考慮并注意重要 的細(xì)節(jié)會(huì)有助于確保預(yù)期的電路性能。

2019-11-06 16:18:51 1211

1211

高速電路設(shè)計(jì)是一個(gè)非常復(fù)雜的設(shè)計(jì)過(guò)程,在進(jìn)行高速電路設(shè)計(jì)時(shí)有多個(gè)因素需要加以考慮,這些因素有時(shí)互相對(duì)立。如高速器件布局時(shí)位置靠近,雖可以減少延時(shí),但可能產(chǎn)生串抗和顯著的熱效應(yīng)。因此在設(shè)計(jì)中,需權(quán)衡

2020-07-10 10:28:00 6

6 印制電路板(PCB)布線在高速電路中具有關(guān)鍵的作用,但它往往是電路設(shè)計(jì)過(guò)程的最后幾個(gè)步驟之一。高速PCB布線有很多方面的問(wèn)題,關(guān)于這個(gè)題目已有人撰寫(xiě)了大量的文獻(xiàn)。本文主要從實(shí)踐的角度來(lái)探討高速電路

2020-10-13 14:07:58 1054

1054

在高速電路設(shè)計(jì)中,元件和元件封裝可能影響芯片內(nèi)以及PCB的信號(hào)完整性。實(shí)際上,信號(hào)完整性包括一組確定信號(hào)質(zhì)量的測(cè)量值,作為分析和減輕噪聲,失真和損耗影響的一種方法。這是一組設(shè)計(jì)實(shí)踐和測(cè)試,有兩個(gè)常見(jiàn)

2021-02-10 09:23:00 1780

1780

高速電路設(shè)計(jì)中的信號(hào)衰減是讓人頭疼的一件事,作為電路設(shè)計(jì)工程師在布線時(shí)應(yīng)該降低信號(hào)衰減。本文主要介紹高速電路設(shè)計(jì)中降低信號(hào)衰減方法,希望對(duì)你有所幫助。 一、降低電抗路徑 在高速電路設(shè)計(jì)中,將接地

2021-01-28 11:06:26 2677

2677 電路設(shè)計(jì)軟件存在意義在于設(shè)計(jì)電路,缺少電路設(shè)計(jì)軟件,電路設(shè)計(jì)將變得十分麻煩。對(duì)于電路設(shè)計(jì)軟件,小編在往期系列文章中已有諸多介紹。為繼續(xù)增進(jìn)大家對(duì)電路設(shè)計(jì)軟件的認(rèn)識(shí),本文將基于protel電路設(shè)計(jì)軟件講解如何設(shè)計(jì)高速PCB。如果你對(duì)電路設(shè)計(jì)軟件具有興趣,不妨繼續(xù)往下閱讀哦。

2020-09-26 09:06:41 2752

2752 雖然印刷電路板(PCB)布線在高速電路中具有關(guān)鍵的作用,但它往往只是電路設(shè)計(jì)過(guò)程的最后幾個(gè)步驟之一。

2020-10-21 11:23:37 3283

3283

在布線電路板時(shí), PCB 設(shè)計(jì)人員的任務(wù)很艱巨。當(dāng)涉及到高速 PCB 布線和信號(hào)時(shí),事情就變得更加復(fù)雜。為了幫助不同的 PCB 設(shè)計(jì)人員,已列出了一系列最佳的高速 PCB 布線實(shí)踐,以幫助他們實(shí)現(xiàn)

2020-10-27 19:12:24 2847

2847 功能板,并確定每塊功能板 PCB 外型尺寸、安裝方式,還必須同時(shí)考慮調(diào)試、維修的方便性,以及屏蔽、散熱、EMI 性能等因素。需要工程人員確定布局布線方案,確定關(guān)鍵電路和信號(hào)線和布線方法細(xì)節(jié),以及應(yīng)該遵從的布線原則。PCB 設(shè)計(jì)過(guò)

2022-11-15 16:29:07 1728

1728 電路設(shè)計(jì)軟件存在意義在于設(shè)計(jì)電路,缺少電路設(shè)計(jì)軟件,電路設(shè)計(jì)將變得十分麻煩。對(duì)于電路設(shè)計(jì)軟件,小編在往期系列文章中已有諸多介紹。為繼續(xù)增進(jìn)大家對(duì)電路設(shè)計(jì)軟件的認(rèn)識(shí),本文將基于protel電路設(shè)計(jì)軟件講解如何設(shè)計(jì)高速PCB。如果你對(duì)電路設(shè)計(jì)軟件具有興趣,不妨繼續(xù)往下閱讀哦。

2020-12-06 17:08:00 3210

3210 讓你布線少走彎道的15條高速PCB布線經(jīng)驗(yàn)分享

2022-02-12 10:44:53 5486

5486 讓你布線少走彎道的15條高速PCB布線經(jīng)驗(yàn)分享

2021-03-04 06:24:26 31

31 電子發(fā)燒友網(wǎng)為你提供詳解PCB高速信號(hào)電路設(shè)計(jì)中的布線規(guī)則資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計(jì)、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-25 08:47:42 36

36 雖然印刷電路板(PCB)布線在高速電路中具有關(guān)鍵的作用,但它往往只是電路設(shè)計(jì)過(guò)程的最后幾個(gè)步驟之一。高速PCB布線有很多方面的問(wèn)題,關(guān)于這個(gè)主題已有大量的文獻(xiàn)可供參考。本文主要從實(shí)踐的角度來(lái)探討高速

2021-06-21 10:58:05 0

0 主要研究了高速數(shù)字電路設(shè)計(jì)中信號(hào)反射的抑制方法。理論上分析了信號(hào)反射產(chǎn)生的原因及其對(duì)電路設(shè)計(jì)指標(biāo)的影響通過(guò)電路仿真比較不同的布局布線和端接策略并針對(duì)具體情況提出了合理的布局布線和接方法。該方法已成功應(yīng)用于多DP并聯(lián)處理系統(tǒng)中實(shí)踐證明該方法可靠、系統(tǒng)工作穩(wěn)定。

2021-08-12 17:14:20 15

15 在高速PCB電路設(shè)計(jì)過(guò)程中,經(jīng)常會(huì)遇到信號(hào)完整性問(wèn)題,導(dǎo)致信號(hào)傳輸質(zhì)量不佳甚至出錯(cuò)。那么如何區(qū)分高速信號(hào)和普通信號(hào)呢?

2022-02-09 10:02:28 4

4 當(dāng)今的信號(hào)處理系統(tǒng)普遍需要使用混合信號(hào)器件,例如為了處理寬動(dòng)態(tài)范圍的模擬信號(hào),高速高性能的ADC信號(hào)顯得更加重要。為了在惡劣的數(shù)字環(huán)境中保持模擬信號(hào)寬動(dòng)態(tài)范圍和低噪聲,就要熟知PCB布線技巧以進(jìn)行良好的高速電路設(shè)計(jì)。本文將為您闡述使用高速轉(zhuǎn)換器時(shí),必須遵循的那些重要PCB布局布線規(guī)則。

2022-04-28 09:29:01 1172

1172 本文主要從實(shí)踐的角度來(lái)探討高速電路的布線問(wèn)題。主要目的

在于幫助新用戶當(dāng)設(shè)計(jì)高速電路 PCB 布線時(shí)對(duì)需要考慮的多

種不同問(wèn)題引起注意。

2022-10-21 16:09:05 0

0 在PCB布線規(guī)則中,有一條“關(guān)鍵信號(hào)線優(yōu)先”的原則,即電源、摸擬信號(hào)、高速信號(hào)、時(shí)鐘信號(hào)、差分信號(hào)和同步信號(hào)等關(guān)鍵信號(hào)優(yōu)先布線。

2023-01-13 09:29:19 1290

1290 8Gbps及以上高速信號(hào)PCB布線建議 —來(lái)源:瑞星微RK3588 PCB設(shè)計(jì)白皮書(shū) 如表1-1所示,RK3588芯片以下接口的信號(hào)能工作在8Gbps及以上速率,由于速率很高,PCB布線設(shè)計(jì)要求

2023-08-02 07:35:01 423

423

如下表所示,接口信號(hào)能工作在8Gbps及以上速率,由于速率很高,PCB布線設(shè)計(jì)要求會(huì)更嚴(yán)格,在前幾篇關(guān)于PCB布線內(nèi)容的基礎(chǔ)上,還需要根據(jù)本篇內(nèi)容的要求來(lái)進(jìn)行PCB布線設(shè)計(jì)。高速信號(hào)布線時(shí)盡量少打孔

2023-08-03 17:31:07 663

663

如下表所示,接口信號(hào)能工作在8Gbps及以上速率,由于速率很高,PCB布線設(shè)計(jì)要求會(huì)更嚴(yán)格,在前幾篇關(guān)于PCB布線內(nèi)容的基礎(chǔ)上,還需要根據(jù)本篇內(nèi)容的要求來(lái)進(jìn)行PCB布線設(shè)計(jì)。 高速信號(hào)布線時(shí)盡量

2023-08-03 18:15:02 487

487 pcb信號(hào)完整性詳解 隨著電子領(lǐng)域技術(shù)日新月異的發(fā)展,高速電路已經(jīng)成為了電路設(shè)計(jì)的重要領(lǐng)域之一。在高速電路中,信號(hào)完整性顯得尤為重要。在設(shè)計(jì)PCB電路時(shí),信號(hào)完整性是一個(gè)必須考慮的因素。那么

2023-09-08 11:46:58 921

921 高速PCB板的電源布線設(shè)計(jì)

2022-12-30 09:22:11 5

5 高速電路無(wú)疑是PCB設(shè)計(jì)中要求非常嚴(yán)苛的一部分,因?yàn)?b class="flag-6" style="color: red">高速信號(hào)很容易被干擾,導(dǎo)致信號(hào)質(zhì)量下降,所以在PCB設(shè)計(jì)的過(guò)程中就需要避免或降低這種情況的發(fā)生。 在具體的高速電路布局布線中,這些知識(shí)技能需要掌握

2023-11-06 14:55:20 256

256 高速電路無(wú)疑是PCB設(shè)計(jì)中要求非常嚴(yán)苛的一部分,因?yàn)?b class="flag-6" style="color: red">高速信號(hào)很容易被干擾,導(dǎo)致信號(hào)質(zhì)量下降,所以在PCB設(shè)計(jì)的過(guò)程中就需要避免或降低這種情況的發(fā)生。 在具體的高速電路布局布線中,這些知識(shí)技能需要掌握

2023-11-06 15:14:06 263

263 一站式PCBA智造廠家今天為大家講講PCB設(shè)計(jì)關(guān)鍵信號(hào)如何去布線?PCB關(guān)鍵信號(hào)的布線要求。在PCB設(shè)計(jì)布線規(guī)則中,有一條“關(guān)鍵信號(hào)線優(yōu)先”的原則,即電源、摸擬信號(hào)、高速信號(hào)、時(shí)鐘信號(hào)、差分信號(hào)

2023-11-22 09:11:10 377

377

在解決矛盾方面各有優(yōu)勢(shì)和限制。本文將從原理、優(yōu)缺點(diǎn)、解決方案等方面詳細(xì)討論如何解決高速信號(hào)的手工布線和自動(dòng)布線之間的矛盾。 首先,我們來(lái)了解手工布線和自動(dòng)布線的基本原理。 手工布線是指設(shè)計(jì)師根據(jù)電路設(shè)計(jì)要求,手工選

2023-11-24 14:38:18 246

246

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論