【摘 要】 介紹了一種在有差錯信道中能夠高可靠性傳輸數據的雙調制解調器的實現方案。它主要由DSP最小系統,串行通信接口,A/D轉換電路和CPLD控制邏輯構成。系統采用兩條線路同時傳輸數據,接收端則根據誤碼率的高低在兩條線路間進行智能切換,選擇性地接收,以此來實現數據的高可靠性傳輸。

?? 關鍵詞:雙調制解調器 數據傳輸 誤碼率 DSP 閃爍存儲器 A/D轉換器

1 引 言

在有差錯信道中進行數據的高可靠性甚至無誤碼傳輸,可采用傳統的差錯重傳(ARQ)和前向糾錯(FEC)等技術,但這些技術都不可避免地存在時延和時延抖動,信道利用率低,開銷大等弊端,不適合于需要一定的可靠性又要求實時傳輸或對突發業務立即進行處理的場合 ,如多媒體數據(語音,圖像 ,文本數據)的通信、電力調度系統之間的通信、公安系統突發任務的下達等。基于TMS320C54的雙MODE M可在一定程度上避免這些問題,它采用兩路全雙工的數據通信鏈路來進行數據傳輸,相當于用兩條線路來傳輸一路信息,接收端根據兩條線路的接收質量智能地決定接收哪路信息,自動切換,無需采用A RQ或FEC等技術就可實現數據的高可靠性傳輸。該系統采用DSP技術,以平衡對稱設計思路 ,實現雙MOD EM在同一平臺上實施 ,并利用軟件無線電技術實現多種選擇靈活搭配,除了具有電路設計 、調試簡單 、可靠性高和抗噪聲能力強等特點外,還具有以下優點:

·傳輸中心頻率靈活可變,可適用于上音頻電力線載波(f=2880Hz,3000Hz)、微波(f=1700Hz)、無線(f=1500Hz),以及電力線載波機話音通道(f=1200Hz)組成的通訊網中,采用本機傳送數據可統一所有的MODEM型號,便于互換與維修。

???·解調部分具有AGC(自動增益控制)功能。

?? ·具有定性的誤碼顯示,線路信噪比狀況一目了然。

·支持兩個MODEM獨立使用。

2 雙MODEM的硬件設計及其實現

2.1 雙MODEM系統的組成

???? ?????????????????

?????????????????

??? 雙MODEM系統的組成如圖1所示,主要由以下五部分構成:

?? (1)DSP最小系統

? 數字處理系統由于其可靠性高、可編程性強等優勢在通信、航天制導、儀器儀表等各個領域正得到越來越廣泛的應用。在雙MODEM中由一片TMS320C5402 DSP芯片和一片EPROM構成的DSP最小系統是整個系統的關鍵部分。TMS320C54X是TI公司TMS320系列芯片中新一代16-bit定點DSP,適合于高速的數字信號處理。其特點如下:

·先進的多總線結構,一條程序總線,三條數據總線,四條地址總線,使得靈活性和性能大大提高。

? ·外接1024kHz晶振,指令周期為10ns,100MIPS運算速度。

???·提供Power Down低功耗方式。

·17×17-bit的并行乘法器為非流水單周期的乘法/累加(MAC)操作產生40-bit的乘積 。

·8個輔助寄存器和一個專用運算單元支持間接尋址。

·4級流水操作用于延遲分支,調用和返回指令。

·16個軟件可編程的等待狀態發生器,用于程序、數據、I/O存儲器空間的延時等待操作。

·可訪問的擴展存儲器空間為192k×16-bit(其中64k程序存儲器、64k數據存儲器、64kI /O存儲器)。

·支持多達16個用戶可屏蔽中斷(SINT15—SINT0),JTAG掃描仿真邏輯(IEEE1149.1)??

? (2)CPLD控制邏輯

現場可編程邏輯門陣列(FPGA)和高性能數字信號處理器(DSP)是信號處理領域兩大關鍵器件,FPGA和DSP的運算速度及并行處理能力成為制約高速信號處理應用的主要因素,FPGA以其設計靈活性及硬件高密度性在信號處理領域顯示出越來越重要的作用。該系統的CPLD控制邏輯采用XILIN的XC9536來完成,XC9536的可編程I/O引腳,可以實現DSP、SCC、A/D轉換等所需的控制邏輯。

? (3)A/D變換

系統接收時首先將模擬的語音信號通過A/D轉換變為數字信號送入TMS320C5402DSP,發送時將數字調制信號通過D/A轉換變為模擬信號后再上信道傳輸,為此我們選擇了TI公司單片集成AD和DA轉換通道的音頻模數和數模轉換器320AD56作為系統的A/D轉換器件,該器件采用Σ-Δ轉換方法,采樣率為22.05kHz,帶寬為8.8kHz,分辨率為16Bits,功耗為150mW,+5 V單電源供電,同時320AD56的時鐘可以直接與TTL、CMOS、或正的ECL邏輯電平相連。

? (4)閃爍存儲器(Flash)

Flash Memory是一個非易失性固態存儲器,這種存儲器的特點是在寫之前要以塊為單位執行擦除命令,即:使所有字節均變為0XFF,然后再寫入數據,而且斷電以后數據不丟失。我們采用AMD公司的AM28F010作為系統的EPROM,它工作所需的時序信號/WE、/RD、/BCE由CP LD控制邏輯提供。AM28F010的工作電壓為+5V,容量為64k×8bit,速度為150ns。

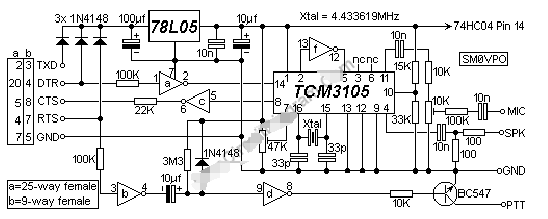

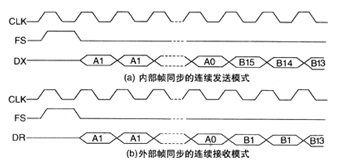

? (5)串口通信模塊

MODEM從發送方串行接收數據,然后經過調制將數字信號轉換為模擬信號,最后通過線路傳送到接收方。接收方也需要通過MODEM從線路上將信號解調,將模擬信號轉換為數字信號,然后串行發送給接收方。本系統中為了實現串行通信,采用AM85C30作為串口通信控制器(SC C),AM85C30是AMD公司的Zilog系列產品,采用CMOS結構,是一種全雙工雙通道、多數據協議的數據通信控制器,可以通過軟件設置實現多種數據通信方式。AM85C30的每個通道都有一套自己的讀/寫寄存器集,所有通信模式都是通過操作寫寄存器來實現的,同時所有狀態判斷都是通過操作讀寄存器來實現的,隨著數據接收/發送,讀寄存器的值可能會發生變化,這些變化能觸發程序活動或內部硬件設置變化。

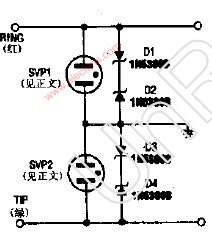

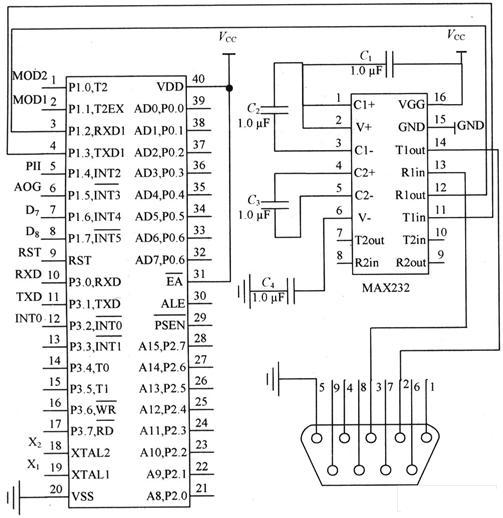

2.2 RS-232接口電路的設計

RS-232標準的接口應能承受接口引腳中任何兩個引腳的短接,而其本身及所聯設備不受到損壞,其電平標準規定了雙極性邏輯電平,即邏輯電平由電壓幅值和極性共同來描述,輸入的邏輯電平是+3V到+15V和-3V到-15V,電壓-3V到+3V之間屬于不確定的;輸出的邏輯電平是+5V到+15V和-5V到-15V,電壓-5V到+5V之間屬于不確定的。由此可知,RS-232的電壓和邏輯電平不能直接用于計算機電路,需要進行電平轉換。在雙MODEM系統中,采用了三片SN75196集成芯片作為RS-232線路驅動器和線路接收器,以此來實現RS-232和計算機電路之間的電平轉換。SN75196是一種專用的多路RS-232收發器,其驅動器/接收器·82·數目為5/3,工作所需的電源電壓為±9V和+5V。

3 雙MODEM的軟件設計及其實現

雙MODEM的軟件設計采用標準的C語言和TMS320C54X的匯編語言混合編制完成,主要由以下幾個要點構成:

3.1 系統初始化

系統上電工作之前,首先必須進行初始化。主要包括對TMS320C5402DSP的狀態寄存器ST0 、ST1,處理器模式狀態寄存器PMST,時鐘模式寄存器CLKMD和軟等待狀態寄存器SWWSR的初始化。對AM85C30通信口的初始化,包括設置合適的數據傳輸格式,數據傳輸波特率,中斷允許寄存器等。其中波特率的設置只需將除數因子寫入AM85C30的“波特率除數鎖存器”WR12、WR 13中,用TMS320C54匯編語言編制的初始化程序將在C語言的主程序中調用。

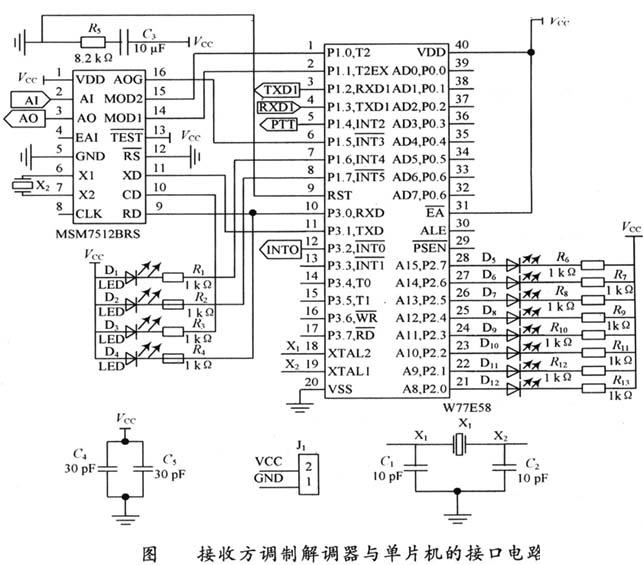

3.2 中斷服務程序

中斷服務處理子程序是通信應用程序的核心,當系統上電初始化時,在中斷向量表的相應位置將初始化為一個臨時中斷服務處理子程序的入口地址,一旦初始化結束,每當一個指定的通信事件出現時,AM85C30將產生一次通信中斷,CPU將依據此中斷號查看中斷向量表,調用執行所指向的新的中斷處理程序,完成收/發處理。收/發數據的程序流程如圖2、圖3所示:

?????????????????????? ?????????? ?????????????

?????????? ?????????????

3.3 環行緩沖區與幀結構?

? (1)環行緩沖區

?????????????????????

??? 在數據通信過程中,發送端和接收端都需要采用一定大小的緩沖區,緩沖區的操作需要采用先進先出(FIFO)的原則,即保證新插入的數據不能覆蓋尚未處理的數據,采用環形緩沖區技術則可很好地解決這個問題,假設數據緩沖區為buffer〔len〕,即長度為len的緩沖區 ,為了達到環形緩沖區操作的目的,需要定義一控制塊結構:

?? typedef struct{

?? int cnt;

?? int rdi;

?? int wri;int*buf;

}BCB

cnt域表示當前緩沖區內的數據長度,rdi表示從當前環形緩沖區中讀取數據的指針位置,wri表示往當前環形緩沖區中存放數據的指針位置,buf指針指向緩沖區的首地址。

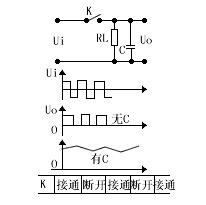

? (2)幀結構

由于雙MODEM系統接收數據時要依據誤碼率的高低在兩條線路間進行智能切換,有選擇性地接收,從而實現數據的高可靠性傳輸。誤碼率的大小雖然是衡量線路傳輸狀況的指標 ,但它是一個長期統計的結果,與當前線路傳輸質量無線性比例關系,在一小段時間內,有可能誤碼率高的線路傳輸的數據更正確,由于這種長期統計和短時數據的正確與否無線性比例關系,如果直接用數據流方式進行熱切換,就存在誤判并導致數據的誤收和對短時突發誤碼反映遲鈍和誤碼擴大的現象。因此必需將數據以一定長度為單位劃分為一個個的幀(fra me),再以幀為單位結合誤碼率進行判斷、切換,這樣就可以把誤碼發生的位置定位在一幀長度內,使切換更準確,數據更可靠,在分幀切換當中,發送端先將數據裝幀打包,幀結構至少應包括幀號、幀數據長度、幀數據等。為此,我們定義了如圖4所示的幀結構。幀結構采用類似HDLC的幀結構,幀起止標志固定為0x7e的8位數據,兩端以0結束,中間是六連1,便于與幀數據相區分,幀結束標志與幀開始標志相同。CRC采用16位的M序列,為了提高CRC校驗的計算速度,采用了查表法。

??????????????????? ??

4 結束語??

?? 實際信道都不是理想的無差錯信道,所傳輸的 數據總會出現一定的誤碼。為此,我們采用高速DSP技術所設計的雙MODEM系統,除了具有一般MODEM的通用功能之外,更主要的是可在有差錯的信道中,實時地進行數據的高可靠性甚至無誤碼傳輸。實際線路測試結果表明該系統在工作條件范圍內,當歸一化信噪比≥17dB時,對511偽隨機碼的誤碼率Pe≤1×10-6,在中低速語音壓縮編碼后使用雙MODEM技術進行數據傳輸將有廣闊的市場發展前景。

2 (美)Joe Campbell 著,游疆來等譯.串行通信編程指南.北京:北京科海培訓中心 ,1990

3 陳堅,孫志月.MODEM通信編程技術.西安:西安電子科技大學出版社,1998.3

?? 關鍵詞:雙調制解調器 數據傳輸 誤碼率 DSP 閃爍存儲器 A/D轉換器

1 引 言

在有差錯信道中進行數據的高可靠性甚至無誤碼傳輸,可采用傳統的差錯重傳(ARQ)和前向糾錯(FEC)等技術,但這些技術都不可避免地存在時延和時延抖動,信道利用率低,開銷大等弊端,不適合于需要一定的可靠性又要求實時傳輸或對突發業務立即進行處理的場合 ,如多媒體數據(語音,圖像 ,文本數據)的通信、電力調度系統之間的通信、公安系統突發任務的下達等。基于TMS320C54的雙MODE M可在一定程度上避免這些問題,它采用兩路全雙工的數據通信鏈路來進行數據傳輸,相當于用兩條線路來傳輸一路信息,接收端根據兩條線路的接收質量智能地決定接收哪路信息,自動切換,無需采用A RQ或FEC等技術就可實現數據的高可靠性傳輸。該系統采用DSP技術,以平衡對稱設計思路 ,實現雙MOD EM在同一平臺上實施 ,并利用軟件無線電技術實現多種選擇靈活搭配,除了具有電路設計 、調試簡單 、可靠性高和抗噪聲能力強等特點外,還具有以下優點:

·傳輸中心頻率靈活可變,可適用于上音頻電力線載波(f=2880Hz,3000Hz)、微波(f=1700Hz)、無線(f=1500Hz),以及電力線載波機話音通道(f=1200Hz)組成的通訊網中,采用本機傳送數據可統一所有的MODEM型號,便于互換與維修。

???·解調部分具有AGC(自動增益控制)功能。

?? ·具有定性的誤碼顯示,線路信噪比狀況一目了然。

·支持兩個MODEM獨立使用。

2 雙MODEM的硬件設計及其實現

2.1 雙MODEM系統的組成

????

?????????????????

???????????????????? 雙MODEM系統的組成如圖1所示,主要由以下五部分構成:

?? (1)DSP最小系統

? 數字處理系統由于其可靠性高、可編程性強等優勢在通信、航天制導、儀器儀表等各個領域正得到越來越廣泛的應用。在雙MODEM中由一片TMS320C5402 DSP芯片和一片EPROM構成的DSP最小系統是整個系統的關鍵部分。TMS320C54X是TI公司TMS320系列芯片中新一代16-bit定點DSP,適合于高速的數字信號處理。其特點如下:

·先進的多總線結構,一條程序總線,三條數據總線,四條地址總線,使得靈活性和性能大大提高。

? ·外接1024kHz晶振,指令周期為10ns,100MIPS運算速度。

???·提供Power Down低功耗方式。

·17×17-bit的并行乘法器為非流水單周期的乘法/累加(MAC)操作產生40-bit的乘積 。

·8個輔助寄存器和一個專用運算單元支持間接尋址。

·4級流水操作用于延遲分支,調用和返回指令。

·16個軟件可編程的等待狀態發生器,用于程序、數據、I/O存儲器空間的延時等待操作。

·可訪問的擴展存儲器空間為192k×16-bit(其中64k程序存儲器、64k數據存儲器、64kI /O存儲器)。

·支持多達16個用戶可屏蔽中斷(SINT15—SINT0),JTAG掃描仿真邏輯(IEEE1149.1)??

? (2)CPLD控制邏輯

現場可編程邏輯門陣列(FPGA)和高性能數字信號處理器(DSP)是信號處理領域兩大關鍵器件,FPGA和DSP的運算速度及并行處理能力成為制約高速信號處理應用的主要因素,FPGA以其設計靈活性及硬件高密度性在信號處理領域顯示出越來越重要的作用。該系統的CPLD控制邏輯采用XILIN的XC9536來完成,XC9536的可編程I/O引腳,可以實現DSP、SCC、A/D轉換等所需的控制邏輯。

? (3)A/D變換

系統接收時首先將模擬的語音信號通過A/D轉換變為數字信號送入TMS320C5402DSP,發送時將數字調制信號通過D/A轉換變為模擬信號后再上信道傳輸,為此我們選擇了TI公司單片集成AD和DA轉換通道的音頻模數和數模轉換器320AD56作為系統的A/D轉換器件,該器件采用Σ-Δ轉換方法,采樣率為22.05kHz,帶寬為8.8kHz,分辨率為16Bits,功耗為150mW,+5 V單電源供電,同時320AD56的時鐘可以直接與TTL、CMOS、或正的ECL邏輯電平相連。

? (4)閃爍存儲器(Flash)

Flash Memory是一個非易失性固態存儲器,這種存儲器的特點是在寫之前要以塊為單位執行擦除命令,即:使所有字節均變為0XFF,然后再寫入數據,而且斷電以后數據不丟失。我們采用AMD公司的AM28F010作為系統的EPROM,它工作所需的時序信號/WE、/RD、/BCE由CP LD控制邏輯提供。AM28F010的工作電壓為+5V,容量為64k×8bit,速度為150ns。

? (5)串口通信模塊

MODEM從發送方串行接收數據,然后經過調制將數字信號轉換為模擬信號,最后通過線路傳送到接收方。接收方也需要通過MODEM從線路上將信號解調,將模擬信號轉換為數字信號,然后串行發送給接收方。本系統中為了實現串行通信,采用AM85C30作為串口通信控制器(SC C),AM85C30是AMD公司的Zilog系列產品,采用CMOS結構,是一種全雙工雙通道、多數據協議的數據通信控制器,可以通過軟件設置實現多種數據通信方式。AM85C30的每個通道都有一套自己的讀/寫寄存器集,所有通信模式都是通過操作寫寄存器來實現的,同時所有狀態判斷都是通過操作讀寄存器來實現的,隨著數據接收/發送,讀寄存器的值可能會發生變化,這些變化能觸發程序活動或內部硬件設置變化。

2.2 RS-232接口電路的設計

RS-232標準的接口應能承受接口引腳中任何兩個引腳的短接,而其本身及所聯設備不受到損壞,其電平標準規定了雙極性邏輯電平,即邏輯電平由電壓幅值和極性共同來描述,輸入的邏輯電平是+3V到+15V和-3V到-15V,電壓-3V到+3V之間屬于不確定的;輸出的邏輯電平是+5V到+15V和-5V到-15V,電壓-5V到+5V之間屬于不確定的。由此可知,RS-232的電壓和邏輯電平不能直接用于計算機電路,需要進行電平轉換。在雙MODEM系統中,采用了三片SN75196集成芯片作為RS-232線路驅動器和線路接收器,以此來實現RS-232和計算機電路之間的電平轉換。SN75196是一種專用的多路RS-232收發器,其驅動器/接收器·82·數目為5/3,工作所需的電源電壓為±9V和+5V。

3 雙MODEM的軟件設計及其實現

雙MODEM的軟件設計采用標準的C語言和TMS320C54X的匯編語言混合編制完成,主要由以下幾個要點構成:

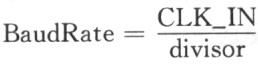

3.1 系統初始化

系統上電工作之前,首先必須進行初始化。主要包括對TMS320C5402DSP的狀態寄存器ST0 、ST1,處理器模式狀態寄存器PMST,時鐘模式寄存器CLKMD和軟等待狀態寄存器SWWSR的初始化。對AM85C30通信口的初始化,包括設置合適的數據傳輸格式,數據傳輸波特率,中斷允許寄存器等。其中波特率的設置只需將除數因子寫入AM85C30的“波特率除數鎖存器”WR12、WR 13中,用TMS320C54匯編語言編制的初始化程序將在C語言的主程序中調用。

3.2 中斷服務程序

中斷服務處理子程序是通信應用程序的核心,當系統上電初始化時,在中斷向量表的相應位置將初始化為一個臨時中斷服務處理子程序的入口地址,一旦初始化結束,每當一個指定的通信事件出現時,AM85C30將產生一次通信中斷,CPU將依據此中斷號查看中斷向量表,調用執行所指向的新的中斷處理程序,完成收/發處理。收/發數據的程序流程如圖2、圖3所示:

??????????????????????

?????????? ?????????????

?????????? ?????????????3.3 環行緩沖區與幀結構?

? (1)環行緩沖區

?????????????????????

??? 在數據通信過程中,發送端和接收端都需要采用一定大小的緩沖區,緩沖區的操作需要采用先進先出(FIFO)的原則,即保證新插入的數據不能覆蓋尚未處理的數據,采用環形緩沖區技術則可很好地解決這個問題,假設數據緩沖區為buffer〔len〕,即長度為len的緩沖區 ,為了達到環形緩沖區操作的目的,需要定義一控制塊結構:

?? typedef struct{

?? int cnt;

?? int rdi;

?? int wri;int*buf;

}BCB

cnt域表示當前緩沖區內的數據長度,rdi表示從當前環形緩沖區中讀取數據的指針位置,wri表示往當前環形緩沖區中存放數據的指針位置,buf指針指向緩沖區的首地址。

? (2)幀結構

由于雙MODEM系統接收數據時要依據誤碼率的高低在兩條線路間進行智能切換,有選擇性地接收,從而實現數據的高可靠性傳輸。誤碼率的大小雖然是衡量線路傳輸狀況的指標 ,但它是一個長期統計的結果,與當前線路傳輸質量無線性比例關系,在一小段時間內,有可能誤碼率高的線路傳輸的數據更正確,由于這種長期統計和短時數據的正確與否無線性比例關系,如果直接用數據流方式進行熱切換,就存在誤判并導致數據的誤收和對短時突發誤碼反映遲鈍和誤碼擴大的現象。因此必需將數據以一定長度為單位劃分為一個個的幀(fra me),再以幀為單位結合誤碼率進行判斷、切換,這樣就可以把誤碼發生的位置定位在一幀長度內,使切換更準確,數據更可靠,在分幀切換當中,發送端先將數據裝幀打包,幀結構至少應包括幀號、幀數據長度、幀數據等。為此,我們定義了如圖4所示的幀結構。幀結構采用類似HDLC的幀結構,幀起止標志固定為0x7e的8位數據,兩端以0結束,中間是六連1,便于與幀數據相區分,幀結束標志與幀開始標志相同。CRC采用16位的M序列,為了提高CRC校驗的計算速度,采用了查表法。

??????????????????? ??

4 結束語??

?? 實際信道都不是理想的無差錯信道,所傳輸的 數據總會出現一定的誤碼。為此,我們采用高速DSP技術所設計的雙MODEM系統,除了具有一般MODEM的通用功能之外,更主要的是可在有差錯的信道中,實時地進行數據的高可靠性甚至無誤碼傳輸。實際線路測試結果表明該系統在工作條件范圍內,當歸一化信噪比≥17dB時,對511偽隨機碼的誤碼率Pe≤1×10-6,在中低速語音壓縮編碼后使用雙MODEM技術進行數據傳輸將有廣闊的市場發展前景。

參考文獻

1 (美)TI公司著.DigitalSignalProcessing Solution.19992 (美)Joe Campbell 著,游疆來等譯.串行通信編程指南.北京:北京科海培訓中心 ,1990

3 陳堅,孫志月.MODEM通信編程技術.西安:西安電子科技大學出版社,1998.3

電子發燒友App

電子發燒友App

評論