今天看到一個格雷碼計數的程序,搜了下定義,覺得還是云里霧里,定義寫的是若任意兩個相鄰的代碼只有一位二進制數不同,則這種編碼為格雷碼。首先數據傳輸時,如果是兩字節數據0x12和0x34,那最后轉成格雷

2018-08-20 14:41:36

格雷碼簡介及格雷碼與二進制的轉換程序格雷碼簡介 格雷碼(英文:Gray Code, Grey Code,又稱作葛萊碼,二進制循環碼)是1880年由法國工程師Jean-Maurice-Emlle

2011-04-22 09:00:58

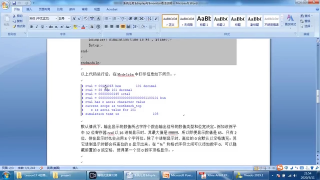

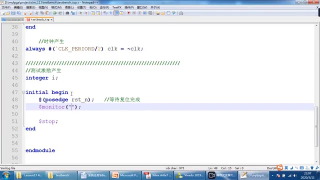

下面是代碼和編譯結果,幫我看一下吧

2014-05-24 22:56:19

- DS1820/1822溫度傳感器函數21. SPI Functions - SPI 函數22. Power Management Functions - 電源管理函數23. Gray Code Conversion Functions - 格雷碼轉換函數

2009-04-22 10:36:02

21. SPI Functions - SPI函數22. Power Management Functions - 電源管理函數23. Gray Code Conversion Functions - 格雷碼轉換函數[hide][/hide]

2010-03-19 21:29:39

DS1820/1822溫度傳感器函數21.SPI Functions - SPI 函數22.Power Management Functions-電源管理函數23.Gray Code Conversion Functions-格雷碼轉換函數

2011-03-03 13:59:11

關系,因而在狀態圖中每條轉移邊需要包含輸入和輸出的信息。狀態編碼 數字邏輯系統狀態機設計中常見的編碼方式有:二進制碼(Binary碼)、格雷碼(Gray碼)、獨熱碼(One-hot碼)以及二一十進制碼(BCD

2012-03-09 10:04:18

過程,它發生在輸入變量變化時。此時,修改卡諾圖,增加多余項,在卡諾圖的兩圓相切處增加一個圓,可以消除邏輯冒險。但該法對于計數器型產生的毛刺是無法消除的。

2、采用格雷碼我們可以通過改變設計,破壞毛刺

2023-11-02 17:22:20

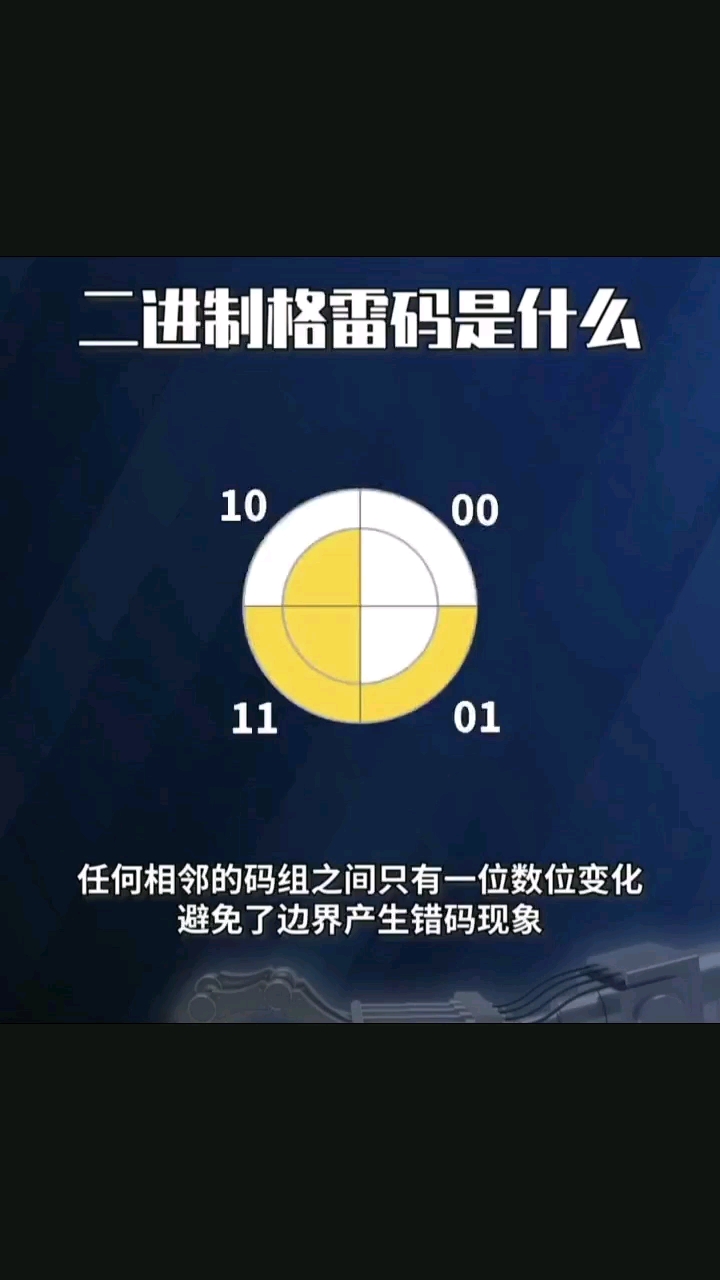

通過改變設計,破壞毛刺產生的條件,來減少毛刺的發生。例如,在數字電路設計中,常常采用格雷碼計數器取代普通的二進制計數器,這是因為格雷碼計數器的輸出每次只有一位跳變,消除了競爭冒險的發生條件,避免了毛刺

2018-08-01 09:53:36

消除的。

2、采用格雷碼

我們可以通過改變設計,破壞毛刺產生的條件,來減少毛刺的發生。例如,在數字電路設計中,常常采用格雷碼計數器取代普通的二進制計數器,這是因為格雷碼計數器的輸出每次只有一位跳變 消除

2024-02-21 16:26:56

時鐘域處理方法如下:打兩拍;異步雙口RAM;格雷碼轉換。01方法一:打兩拍大家很清楚,處理跨時鐘域的數據有單bit和多bit之分,而打兩拍的方式常見于處理單bit數據的跨時鐘域問題。打兩拍的方式,其實

2021-03-04 09:22:51

大家好,我正在學習FPGA關于狀態機的知識點。看到書中寫到:格雷碼最大優點在于編碼依次變化,相鄰兩個編碼之間只有一位發生變化,這樣就不會產生“過渡噪聲”。例如:二進制編碼0111轉換為下一

2017-06-19 20:29:26

相對于同步電路其分析與時序約束更加復雜,但是具有低電源功耗,無時鐘偏斜等問題。異步電路容易產生亞穩態問題,需要在設計是進行特殊的設計處理。比如兩級同步,異步FIFO,格雷碼等。思考:可以從多個角度來解答這個問題:1. 基本概念,2電路特性,3.設計方法,4.時序分析更多題目詳見附件

2018-12-14 16:28:59

獨熱碼在狀態機里面使用比價廣泛,這一塊有些人愛用,有些人嫌煩,有時候可以用用格雷碼跳轉,不過格雷碼只支持那種一步到底的,中間有分支就不好做了,所以后來還是回到了獨熱碼的正道上。說白了獨熱碼

2018-06-07 17:57:14

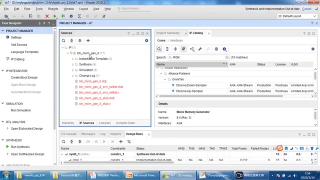

我想使用用戶定義基元(UDP)來構建一個項目來將二進制轉換為格雷碼,但UDP似乎無法轉換為項目,我該怎么辦?binary_to_gray_udp.rar 39 KB以上來自于谷歌翻譯以下為原文I

2019-03-07 13:48:00

,制作簡便,成本低等優點。增量式編碼器結構簡單,制作容易,一般在碼盤上刻A、B、Z三道均勻分布的刻線。由于其給出的位置信息是增量式的,當應用于伺服領域時需要初始定位。格雷碼絕對式編碼器一般都做成循環二進制

2014-03-18 10:03:58

響應,公式如下:最大響應頻率(Hz)/ (脈沖數/轉) * 60 = 軸的轉速RPM6、輸出電壓是指輸出脈沖的電壓。輸出電壓會因輸出電流的變換而有所變化。7、格雷碼格雷碼是高級數據,因為是單元距離

2021-05-17 13:20:52

時鐘域處理方法如下:打兩拍;異步雙口RAM;格雷碼轉換。01方法一:打兩拍大家很清楚,處理跨時鐘域的數據有單bit和多bit之分,而打兩拍的方式常見于處理單bit數據的跨時鐘域問題。打兩拍的方式,其實

2021-02-21 07:00:00

的三種方法跨時鐘域處理方法如下: 1. 打兩拍; 2. 異步雙口RAM; 3. 格雷碼轉換。 方法一:打兩拍 大家很清楚,處理跨時鐘域的數據有單bit和多bit之分,而打兩拍的方式常見于處理

2021-01-08 16:55:23

在編寫有限狀態機時,為什么采用獨熱碼會占用更多的觸發器和更少的組合邏輯?從FPGA內部結構和數電知識基礎上怎樣理解???求大神們不吝賜教,多謝。

2016-03-02 00:33:29

。而絕對式編碼器是直接輸出數字量的傳感器,它是利用自然二進制或循環二進制(格雷碼)方式進行光電轉換的,編碼的設計一般是采用自然二進制碼、循環二進制碼、二進制補碼等。特點是不要計數器,在轉軸的任意位置

2011-03-08 14:16:59

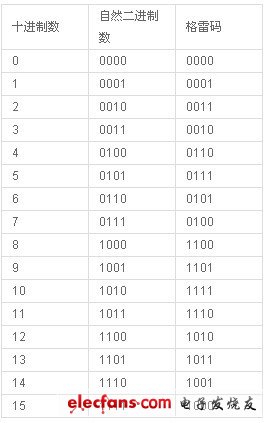

的權為21=2,b2位的權為22=4,b3位的權為23=8,例: 0111= 0×8 + 1×4 + 1×2 + 1×1=7 一般情況下,十進制碼與二進制碼之間的關系可表示為:(N)D= b3 W3 + b2 W2 + b1 W1 + b0 W0 表1.4.1幾種常見碼對照表表1.4.2 格雷碼

2009-04-06 23:55:36

的是8421BCD碼,無權碼用得較多的是余三碼和格雷碼,我們通常所說的BCD碼指的是8421BCD碼。這些編碼跟十進制數對應的關系如下:十進制數 8421BCD碼 余3碼 格雷碼

2011-11-03 17:36:24

你好!目前我正在編寫一個代碼,涉及ASCII字符與其Gray代碼等價的轉換。我已經為我正在使用的測試代碼附加了一個文件。我花了好幾個小時試圖弄清楚在調用ascii和調用gray之間應該放置什么,以便所有東西都按預期流動,所以我一直試圖弄清楚如何確切地告訴代碼進行轉換。我在想你們是不是能幫上忙或者至少給出你的想法。任何幫助是贊賞!

2020-03-27 09:22:23

正在做一個環形倒立擺(C51單片機控制)!!遇到問題如下 請大家指點迷津{:1:};我用的是10位絕對型倒立擺 ,有10條數據線,輸出格雷碼. 請問這10條數據線是否直接與單片機 IO口相連,連完之后又該如何對這組格雷碼進行檢測并輸出二進制數!!{:21:}大神大神 請幫助一下

2014-07-28 22:03:58

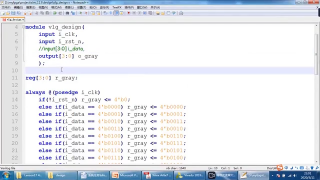

可編程邏輯器件(PLD),只不過我們一般將其用作非易失存儲器,我們以Atmel的AT28C16為例介紹如何具體實現組合邏輯的設計 首先我們要設計4位的二進制轉4位格雷碼轉換器,設一組4位二進制數值,數值按

2015-10-25 22:13:16

RAM測試方法基于格雷碼掃描的MARCH改進方法

2020-12-30 07:58:25

編程,程序設計時,應選擇合理的編碼方式,常用的編碼方式有:順序編碼(也稱為二進制編碼)、格雷碼和獨熱碼,對于小型數字系統設計使用順序編碼和格雷碼更有效[9].就順序編碼而言,有時會有多個位同時發生

2018-09-28 16:02:42

修改常數、 報警值設定等。Intel公司的8279具有鍵盤顯示接口的強大功能,擴展4×4的鍵盤和外接5位LED顯示器,使之具有良好的人機界面。8155主要完 成風向格雷碼信號的并行采集

2010-02-02 12:35:37

以手到擒來。這里介紹的三種方法跨時鐘域處理方法如下:打兩拍;異步雙口 RAM;格雷碼轉換。01方法一:打兩拍大家很清楚,處理跨時鐘域的數據有單 bit 和多 bit 之分,而打兩拍的方式常見于處理單 bit

2020-09-22 10:24:55

通過對FPGA芯片內部EBRSRAM的深入研究,提出了一種利用格雷碼對地址進行編碼的異步FIFO設計方案。

2021-04-13 06:41:03

響應頻率300 K Hz[/td][td=106]輸出長線驅動、推拉輸出、SSI、格雷碼4-20毫安、0-5v、1-5v、0-10v工作電壓DC5V、DC5-26V24v外殼材質進口鋁合金,表面氧化

2021-10-19 15:56:35

反射碼(循環碼)十進制數 二進制數 格雷碼 十進制數 二進制數 格雷碼 0 0000 0000 8 1000 1100 1 0001 0001 9 1001 1101 2 0010 0011 10

2011-04-11 10:00:29

以手到擒來。這里介紹的三種方法跨時鐘域處理方法如下:打兩拍;異步雙口 RAM;格雷碼轉換。01方法一:打兩拍大家很清楚,處理跨時鐘域的數據有單 bit 和多 bit 之分,而打兩拍的方式常見于處理單 bit

2020-10-20 09:27:37

是,該技術僅覆蓋近距離,對環境光敏感,并且僅限于掃描應用。還需要復雜的算法和校準。另外,該技術對結構化或復雜的表面敏感。 2、結構光成像 在結構光中,將預定的光圖案投影到物體上,比如格雷碼,并且

2019-11-19 15:28:37

求一個一種可控4位碼轉換電路設計。選擇合適的芯片設計一個可逆的4位碼轉換電路。當控制信號為1時,它將8421碼轉換為格雷碼;當控制信號為0時,它將格雷碼轉換為8421碼。

2020-05-25 10:12:53

本帖最后由 gk320830 于 2015-3-8 19:55 編輯

設計要求:在控制信號C=1時,將8421碼轉換為格雷碼;C=0時,將格雷碼轉換為8421碼;寫出設計步驟,列出碼變換

2012-12-27 21:25:09

以及四位碼A3A2A1A0,輸出為四位碼Y3Y2Y1Y0。當C=1時,A3A2A1A0為二進制碼,Y3Y2Y1Y0為格雷碼,電路將二進制碼轉換成格雷碼:當C=0時,A3A2A1A0為格雷碼

2015-10-24 11:03:28

對于計數器型產生的毛刺是無法消除的。

2、采用格雷碼我們可以通過改變設計,破壞毛刺產生的條件,來減少毛刺的發生。例如,在數字電路設計中,常常采用格雷碼計數器取代普通的二進制計數器,這是因為格雷碼

2023-05-30 17:15:28

; 8421BCD、2421BCD、余3碼、格雷碼、奇偶校驗碼、ASCⅡ碼11-2 基本邏輯門電路

2009-09-24 10:15:49

為了實現多對極磁電式軸角編碼器的高分辨率絕對式檢測并降低其成本,基于改進格雷碼構建了一種新型多極磁電軸角編碼器模型,提出一種基于校準查表的信號處理方式,以消除磁場非線性和裝配誤差對測量精度

2010-06-02 10:04:24

組合邏輯電路設計二、 實驗原理1. 編碼器把二進制碼按一定的規律編排,例如 8421 碼、格雷碼等,使每組代碼具有一特定的含義(代表某個數或控制信號)稱為編碼 。 具有編碼功能的邏輯電路稱為編碼器 。如圖是常用的 8 線-3 線優先編碼器 74LS148 與其功能表。 ????′ = 0表

2021-07-30 07:41:16

編碼器 編碼器的定義:在數字系統里,常常需要將某一信息(輸入)變換為某一特定的代碼(輸出)。把二進制碼按一定的規律編排,例如8421碼、格雷碼等,使每組代碼具有一特定的含義(代表某個數字或控制信號

2021-09-03 06:35:59

//Asynchronic FIFO //function description//using gray code to synchronic asynchronic signalmoduleAsyncFIFO(wclk,rclk,wen,ren,din,dout,wrst,rrst,rempty,wfull);parameterDataWidth=8,RamDepth =16,AddrWidth=4;//portwriteinputwclk;inputwen;input[(DataWidth-1):0]din;inputwrst;//portreadinputrclk;inputren;inputrrst;//output portoutput[(DataWidth-1):0]dout;outputrempty;//high activeoutputwfull;//high active//regrempty;//regwfull;//wire[(DataWidth-1):0]dout;reg[(DataWidth-1):0]dout;wirerempty_val;wirewfull_val;/*****************************///FIFO MEMORYreg[(DataWidth-1):0]FIFO_RAM[(RamDepth-1):0];//writewire[(AddrWidth-1):0]raddr;//read addresswire[(AddrWidth-1):0]waddr;//write addressreg[AddrWidth:0]rptr_binary;//read pointer with MSBreg[AddrWidth:0]wptr_binary;//write pointer with MSBwire[AddrWidth:0]rptr_gray;//read pointer transform to gray code wire[AddrWidth:0]wptr_gray;//write pointer transform to gray codereg[AddrWidth:0]wptr_gray1;reg[AddrWidth:0]rptr_gray1;//用寄存器輸出的原因是,因為在同步到另一個時鐘域的時候,必須不經過任何組合邏輯,同步器的第一級對于組合邏輯產生的毛刺很敏感,//同時同步器的兩個寄存器要盡量的放的近些。防止設計者加入組合邏輯//synchronic reg variate reg[AddrWidth:0]w_rptr_gray;reg[AddrWidth:0]w_rptr_gray1; reg[AddrWidth:0]r_wptr_gray;reg[AddrWidth:0]r_wptr_gray1;//write and read address generationassignraddr = rptr_binary[(AddrWidth-1):0];assignwaddr = wptr_binary[(AddrWidth-1):0];/*******************the synchronization of asynchronous clock dpmains************///read pointer synchronize to write clockalways @(posedge wclk,negedge wrst)if(!wrst){w_rptr_gray1,w_rptr_gray}

2016-07-04 16:48:19

我在網上看到一篇利用格雷碼來設計異步FIFO,但是看他們寫的一些源碼,小弟有些不是很理解,在設計時為什么會出現Waddr和wptr兩個關于寫指針的問題,他們之間的關系是什么????wptr在定義時候為什么比Waddr多一位呀???

2017-05-19 11:04:13

請問:看了幾天,沒頭緒。難道是做成很多副圖片,按順序投射出來的?謝謝

2019-02-13 10:17:48

解決方案支持全局和滾動快門攝像頭的同步攝像頭采集投影儀和攝像頭校準例程用于生成視差圖、景深圖和點云的結構化照明算法采用了格雷碼和混合三相掃描技術

2018-11-06 17:00:34

20mA。每個漏極開路端口的LED亮度可通過256級PWM控制信號獨立調節。輸入端口對(PORT6、PORT7)可配置成接受旋轉開關的2位格雷碼輸入。此外,如果沒有用作按鍵開關控制,最多6列引腳可作為通用漏極開路輸出(GPO),用于LED驅動或邏輯控制。

2021-05-18 07:04:23

:“編譯器”和“正確的語法中的預處理器定義”(TestValay= 1)(見屏幕截圖2)PSoC Creator把定義定義為“1=”而不是“1”。所以代碼沒有顯示正確,格雷碼確實是編譯的!編譯器工作

2019-02-22 06:25:24

產品介紹:precilec雷恩rcs58s系列,屬于雷恩絕對值產品的一個標準類型,外徑58mm,單圈16位,輸出信號為格雷碼制SSI同步串行,產品采用嚴格防塵防水,高的防護等級,ip66/ip67

2022-01-10 14:42:07

并行接口:運用每一個比特一條線同時傳送全部比特。數據傳輸由推換電路里兩個晶體管開展。例如信息通過PLC能夠被計算出來。在自動控制系統中開展從格雷碼到二進碼的轉換,由于這類方式的編碼能夠馬上被發送。位

2022-07-08 13:30:06

技術規格工作電壓10 ... 30 V DC空載電流最大 140 mA功耗≤ 2,5 W , 沒有輸出驅動器線性度± 0,5 LSB輸出碼格雷碼,二進制碼Code

2022-08-10 13:04:14

技術規格工作電壓10 ... 30 V DC空載電流最大 140 mA功耗≤ 2,5 W , 沒有輸出驅動器線性度± 0,5 LSB輸出碼格雷碼,二進制碼Code

2022-08-10 13:05:57

)0 %電氣技術規格工作電壓10 ... 30 V DC空載電流最大 140 mA功耗≤ 2,5 W , 沒有輸出驅動器線性度± 0,5 LSB輸出碼格雷碼,二進

2022-08-15 13:19:23

技術規格工作電壓10 ... 30 V DC空載電流最大 140 mA功耗≤ 2,5 W , 沒有輸出驅動器線性度± 0,5 LSB輸出碼格雷碼,二進制碼Code

2022-08-15 13:23:42

技術規格工作電壓10 ... 30 V DC空載電流最大 140 mA功耗≤ 2,5 W , 沒有輸出驅動器線性度± 0,5 LSB輸出碼格雷碼,二進制碼Code

2022-08-16 09:08:52

技術規格工作電壓10 ... 30 V DC空載電流最大 140 mA功耗≤ 2,5 W , 沒有輸出驅動器線性度± 0,5 LSB輸出碼格雷碼,二進制碼Code

2022-08-16 09:10:24

技術規格工作電壓10 ... 30 V DC空載電流最大 140 mA功耗≤ 2,5 W , 沒有輸出驅動器線性度± 0,5 LSB輸出碼格雷碼,二進制碼Code

2022-08-16 09:14:06

技術規格工作電壓10 ... 30 V DC空載電流最大 140 mA功耗≤ 2,5 W , 沒有輸出驅動器線性度± 0,5 LSB輸出碼格雷碼,二進制碼Code

2022-08-16 09:15:34

技術規格工作電壓10 ... 30 V DC空載電流最大 140 mA功耗≤ 2,5 W , 沒有輸出驅動器線性度± 0,5 LSB輸出碼格雷碼,二進制碼Code

2022-08-16 09:16:44

技術規格工作電壓10 ... 30 V DC空載電流最大 140 mA功耗≤ 2,5 W , 沒有輸出驅動器線性度± 0,5 LSB輸出碼格雷碼,二進制碼Code

2022-08-16 09:24:10

則采用獨立電源供電,以支持1.8 V CMOS或LVDS輸出。標準串行端口接口(SPI)支持各種產品特性和功能,例如:數據格式化(偏移二進制、二進制補碼或格雷碼)

2022-08-25 16:25:54

Nidec(尼得科) 旋轉編碼開關 SH-7010MA封裝/規格: SW6_7.3x7.1mm_SM, 旋轉編碼開關。公用端子插腳中心位置可用格雷碼輸出良好的視覺性可水洗BCD 10 Position端接樣式:J型引線

2022-10-24 14:05:49

Nidec(尼得科) 旋轉編碼開關 SH-7010 MB封裝/規格: SW6_7.3x7.1mm_SM, 旋轉編碼開關 SMD BCD 100mA 5VDC。公用端子插腳中心位置可用格雷碼輸出良好的視覺性可水洗BCD 10 Position端接樣式:鷗翼

2022-10-24 14:13:29

Nidec(尼得科) 旋轉編碼開關 SH-7050 MA封裝/規格: SW6_7.3x7.1mm_SM, 旋轉編碼開關 SMD BCD 100mA 5VDC。公用端子插腳中心位置可用格雷碼輸出良好的視覺性可水洗BCD 16Position端接樣式:J型引線

2022-10-24 17:04:31

Nidec(尼得科) 旋轉編碼開關 SH-7050MB封裝/規格: SW6_7.3x7.1mm_SM, 旋轉編碼開關。公用端子插腳中心位置可用格雷碼輸出良好的視覺性可水洗BCD 16Position端接樣式:鷗翼

2022-10-24 17:15:52

參數表節選:的技術參數 WCS2B-LS311產品闡述 讀頭,SSI 接口,格雷碼通用規格通過速度≤ 12,5 m/s測量范圍最大 327 m編碼尺的自由公差水平: 10 mm

2022-11-09 13:07:02

參數表節選:的技術參數 WCS3B-LS311產品闡述 讀頭,SSI 接口,格雷碼通用規格通過速度≤ 12,5 m/s測量范圍最大 314,5 m編碼尺的自由公差水平: 31

2022-12-05 13:21:24

電子發燒友App

電子發燒友App

評論