摘要:

飛思卡爾Kinetis MCU系列是一款高度集成、低功耗32位微處理器,基于ARM Cortex M4內核并擁有面向工業控制和多市場業務的內置DSP功能。Kinetis MCU采用Cadence模擬混合信號驗證平臺。本文將主要介紹Kinetis MCU混合信號的驗證策略和挑戰,其中包括混合信號建模、連接驗證、混合信號VIP、混合信號功率驗證和混合信號覆蓋范圍。

1 介紹

飛思卡爾Kinetis MCU系列是一款高度集成、低功耗32位微處理器,基于ARM Cortex M4內核并擁有面向工業控制和多市場業務的內置DSP功能。該產品是一大創新成果,是飛思卡爾邁出的重要一步。

Kinetis擁有多個復雜的混合信號IP。這些IP擁有多種不同的模式和設置,可支持多個電源。模擬部分可與數字部分以及其他模擬設計緊密合作。從模擬IP的角度來看,與性能需求相比,該IP功能變得越來越重要。從片上系統的角度來看,由于設計復雜,很難發現隱藏的錯誤。

鑒于以上幾點,kinetis產品采用了最新的數模混合信號驗證方法學。Verilog-AMS語言為模擬IP建模,采用了Cadence AMS designer驗證平臺進行仿真。

本文包括4部分:第一部分為背景介紹,第二部分為Kinetis MCU混合信號驗證方法概述,第三部分為Kinetis MCU混合信號驗證在AMS建模、AMS VIP、連接性驗證、功率驗證和AMS覆蓋范圍所面臨的挑戰。

2 設計與實施

2.1 AMS Designer

Cadence Virtuoso® AMS Designer是一款靈活的混合信號模擬器,它可以連接高級模擬和數字環境,從而實現無縫的混合信號模擬和驗證。它將數字NC-Sim引擎與4款流行的MMSIM模擬引擎(Spectre、SpectreRF、APS® 和UltraSim®)相結合。根據設計特性,為設計人員提供他們所需的仿真結果。

AMS designer集成了面向混合信號驗證的Virtuoso全定制環境和面向在數字驗證環境中的用于混合信號驗證的Cadence敏捷型功能驗證平臺。它可支持向下算法,從而在早期設計周期中迅速檢測到設計錯誤,并采用混合信號硬件描述語言來加快仿真速度。

2.2混合信號驗證的策略和方法

驗證采用了軟硬件協同仿真方法

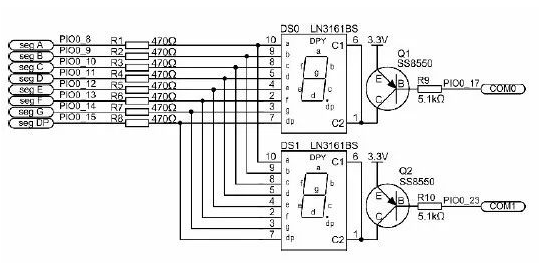

SoC測試平臺是建立在基于C語言的定向測試案例、??基于系統Verilog的測試平臺組件,基于Verilog-AMS的測試平臺組件和基與system verilog的隨機約束激勵。驗證方法包括形式驗證、基于斷言的驗證、覆蓋驅動的隨機約束驗證方法。

2.3混合信號驗證的挑戰

在所有主要的設計挑戰中,混合信號驗證是最大的一個。對于絕大部分的芯片故障,大部分都是可以通過更好的驗證方法預防的。那么混合信號驗證最大的挑戰是什么?就是AMS建模、功耗驗證、驗證IP、連通性驗證、H/S協同仿真和覆蓋率。接下來將會詳細介紹Kinetis混合信號驗證是如何克服這些挑戰的。

2.3.1 混合信號驗證的挑戰之一 – 行為建模

AMS建模有一個共同的規則----建你所需要的模型,而不是你能建的模型。

本文選自電子發燒友網6月《智能工業特刊》Change The World欄目,轉載請注明出處。

用戶評論(0)