1、簡介

IPOntellectualPIDperty)是隨著EDA(ElectroniDesignAn-tomation)技術發展而提出的新概念。隨著微電子工業的飛速革命,集成電路的設計規模越來越大,以滿足日漸復雜的電子系統的需要,同時又由于上市時間廠linetoMarket)的要求,必須花費盡可能少的時間來證明部件和系統的可靠性。所以,從共享的角度來看待問題,對已經過設計驗證的功能模塊的重用無疑是解決這個瓶頸的最佳方案。

當前的設計思想是類似軟件的面向對象的概念,采用虛擬插座VS(VirtuaS0ckets)的概念,把多個不同來源的電路模塊組合起來達到要求的功能,并將其集成在一塊硅片上。IP就是實現這種功能模塊的混合、嗎配和重用以實現片上系統(SystemonACh響設計的最好方法。這將使系統級IC集成設計成為切實可行的技術方向。

IP就其本質來講即是一個能提供正確接口信號的功能模塊。MentorGraPhics所下的定義是可重用的部件(ReusableComPOnentS)。具體在ASIC/IC設計中,通常指的是一個軟核,是一個通過具體電路驗證(Silicon-Verified)的功能模塊,它以可綜合的寄存器傳輸級RWRegisterTranslationbevel)文件給出,通過庫文件調用可實現它的重用。

2、可編程DMA控制器

DMA直接存儲器存取臟制器是用于微處理器系統的外圍接口電路芯片。它能夠增強系統外部設備同主存儲器之間信息傳送的性能,從而增強數據吞吐量。

8237A是Intel公司推出的8位DMA控制器,提供了大量的可編程控制特性,同時可以允許程序動態編程控制而優化系統。它主要配合微控制器,完成外圍設備與存儲器之間的大量高速數據傳輸工作,并且它也提供存儲器到存儲器的傳送功能。當前存在著大量采用8237A作為外圍接口電路芯片的微控制電路,所以8237A的IP設計對于這些系統片上集成具有重要意義。

8237A的IP包含以下幾個特點:

(1)包含了四個通道,每個通道可以有四種工作模式,可以單字節傳送、塊傳送房求傳送、級連工作。每個通道可以通過級連模式連接附加的控制器芯片而擴展成為任意通道數,其它的三個模式可以由用戶編程為外圍器件提供DMA傳送服務。

(2)通道編程設置為自動初始化,每當傳送結束或者EOP信號有效時,通道可以自動初始化。由于每個通道的地址和字寄存器都是16位,所以具有64K地址以及字計數能力。

(3)提供通道優先權控制,進行固定和循環優先權調度。8237A最突出的特點是具有對多種傳輸方式的控制。

3、電路功能模塊設計

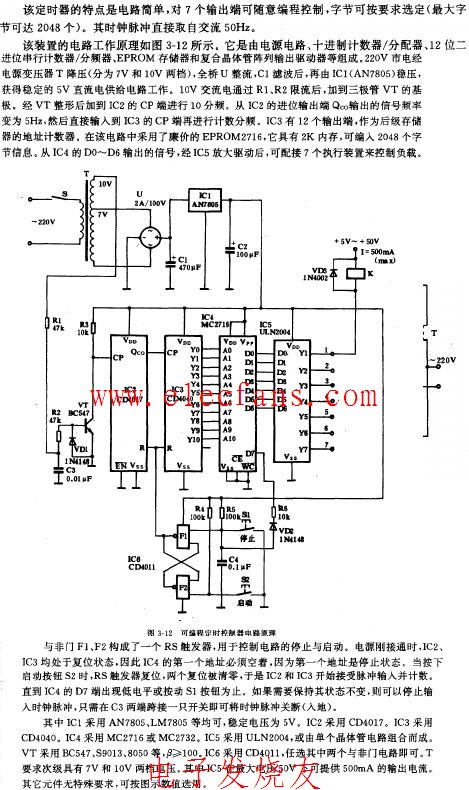

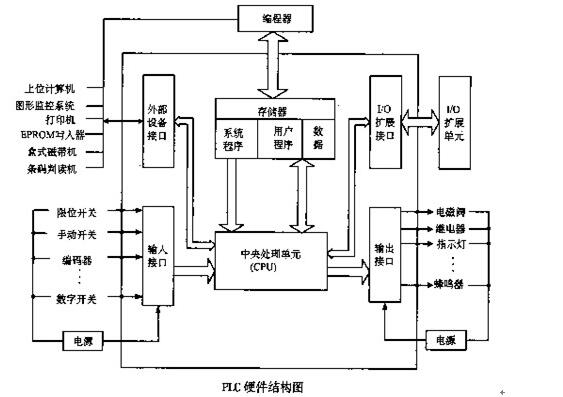

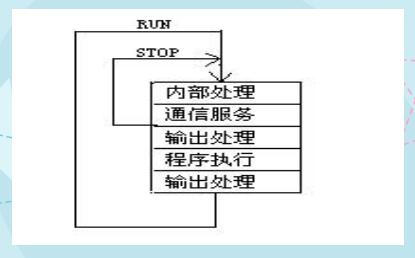

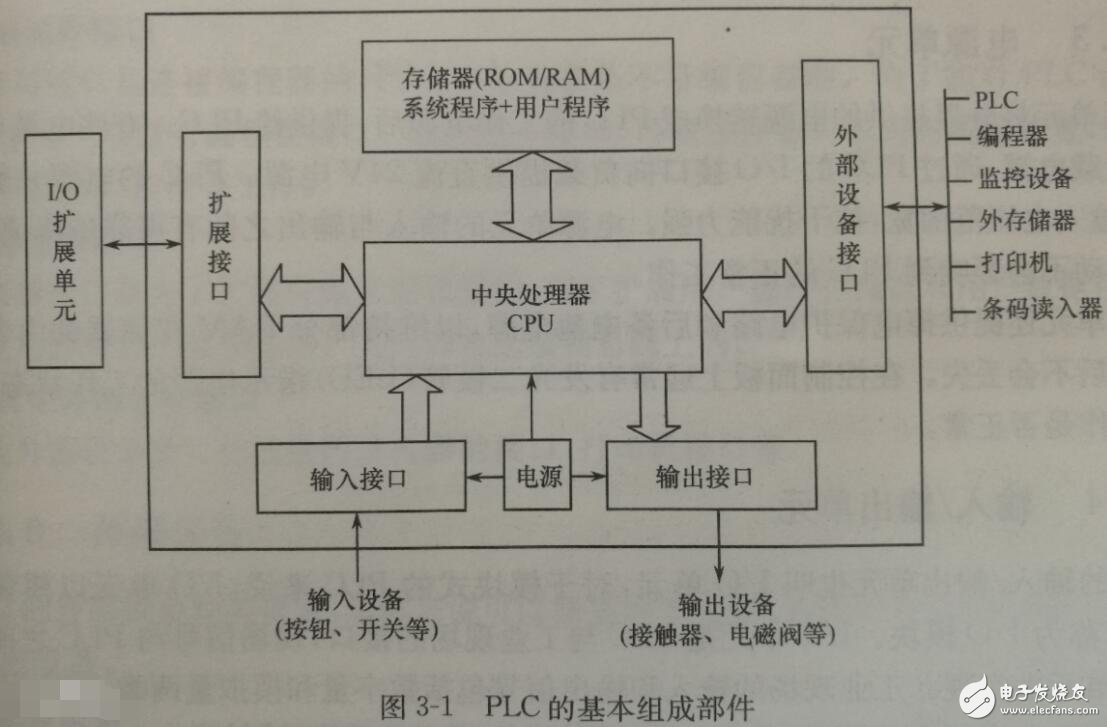

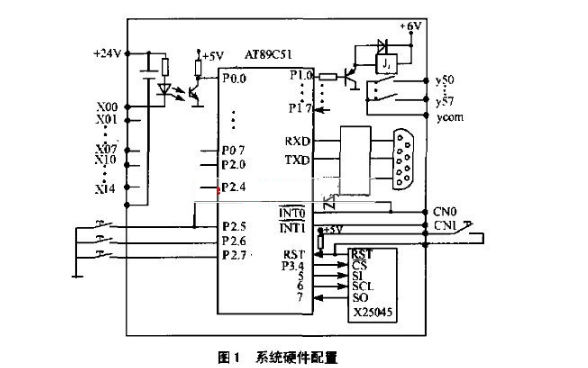

整個系統設計成為全同步電路。根據Intel提供的器件時序,設計在系統時鐘CLK的下降沿將狀態翻轉,給出相應控制信號;而系統的數據通道在系統時鐘CLK的上升沿進行數據傳遞。通過對文獻間所進行的邏輯分析,所設計的IP電路劃分為如下模塊:接口模塊、通道請求優先級及屏蔽控制模塊。中央控制模塊、通道地址和計數器控制模塊、命令寄存器模塊、狀態寄存器模塊。如圖1。

3.1接口模塊

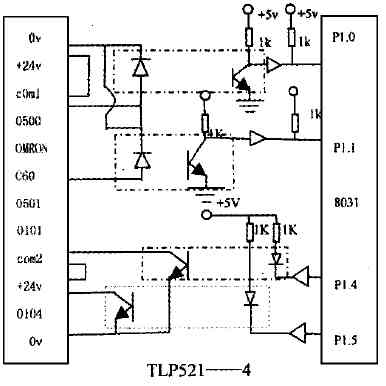

接口電路的主要功能是實現與CPU和存儲器以及外部設備的連接。接收CPU寫入的命令字、地址、字節數、模式控制率等;向CPU提供狀態字以及各個寄存器的內容。對于存儲器和外設的接口一般都是提供傳輸數據的當前地址,在存儲器至存儲器傳輸工作模式下,還要使用臨時寄存器Temp對傳輸的數據進行暫存。

3.2通道請來優先級及屏蔽控制模塊

這個模塊利用邊沿檢測器和或邏輯實現了對DREQ(DMARequest晴求的沿觸發以及電平觸發的檢測。同時通過優先級設置和屏蔽寄存器的設置判定對應請求是否有效,之后將有效的請求送給中央控制模塊,由中央控制模塊對相應的通道進行處理,并且發送DACK(DMAcknowle吃小向應信號通知外設撤消DREQ請求。優先級可以用命令方式設置為固定優先級和循環優先級。

3.3中央控制模塊

這是整個IP設計的核心部分,該模塊作為DMA控制器的主要工作模塊,相應地執行各種控制命令,負責在空閑(id由周期響應CPU操作;在執行(ActiVe調期,協調DMA內部的其它模塊,接管總線控制,提供數據傳輸所需要的所有地址、數據暫存控制,并向外提供讀寫時序信號。

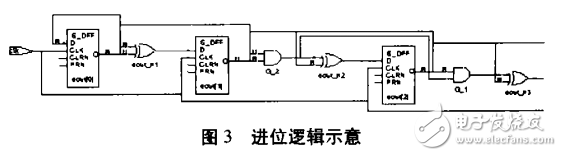

8237A的工作過程可以分為7個狀態,即SI,SO,S1,S2,S3,S4和Sw。它的狀態轉移如圖2所示。該模塊的主要構成部分就是系統狀態機,而其中的引,SZ,S4狀態對于數據通道進行主要操作,8237A是一個同步電路,所以中央控制模塊就設計成一個同步狀態機,每個狀態都是一個時鐘周期的寬度。

3.4 ?Inc/Dec單元

因為在S1,S2,S4這三個狀態,也就是三個周期中,8237A必須執行加載,地址改變,恢復這三個操作,而在部分情況下地址必須要求在S4改變,所以就不能保證一個周期一個操作。這樣就必須以每個通道的當前寄存器作為Inc/Dec的源和目的操作數。

如果每個通道的地址和計數采用同步計數器,該同步計數器由每個通道的當前寄存器實現,這樣的話,四個通道的地址和字數計算就至少需要四個同步計數器;那么這個設計與直接采用組合邏輯Inc/Dec單元的設計相比,就少了一個4路16位的多路選通器。如果按照ASIC庫標準單元設計,該多路選通器將占用16X4個CMOS門,同時由于同步計數器的進位判斷邏輯并本比直接的組合邏輯Inc單元少,所以在假設門的傳輸延遲滿足工作頻率的情況下,它們都可以采用每級一個與門的邏輯,應該為14個二輸入與門與匕個二輸入異或門,每個與門占用兩個CMOS門,每個異或門占用四個CMOS門。這樣采用同步計數器將占用Zx4xl4+4x4xls=352個CMOS門;采用組合邏輯Inc單元將占用16X4+Zxl4+4X15=152個CMOS門。即使在只有加1邏輯的情況下,同步計數器的進位判斷邏輯比直接的組合邏輯Inc單元多。如果再加上減1邏輯,同步計數器占用的CMOS門將會以接近4倍的關系和直接的組合邏輯Inc/Dec單元一起增長,所以應該采用組合邏輯Inc/Dec單元。

當然以上的設計都是在采用ASIC標準單元庫的情況下,由于采用FPGA實現時,沒有可以直接利用的MUX單元,4路16位的多路選通器就會占用較多的邏輯資源,同時影響系統頻率的提高,而且FPGA中提供專用的進位鏈邏輯來優化計數器設計,所以應該采用四個同步計數器的設計實現。所以在IP的設計中,考慮到實現目標工藝的不同,以及對于系統整體性能的需求不同,提供了可以參數化選擇的實現方法。

3.5先后觸發器

在8237ADMA控制器中,先后觸發器的作用就是在系統讀寫DMA中的16位寄存器時,提供高低8位寄存器部分的先后次序控制。

設計中,對于高低8位寄存器部分的讀寫要根據先后觸發器的值進行判斷操作。由于整個系統是同步設計,就不能采用利用讀寫信號的上升沿直接將先后觸發器翻轉的方法。所以,設計中對讀寫信號進行邊沿檢測,利用檢測得到的讀寫結束信號,在時鐘的上升沿將觸發器翻轉。而且,由于并不是所有的對內部寄存器的讀寫都需要翻轉先后觸發器,所以還要對地址的進行判斷,但是如果在讀寫信號結束時進行檢測,此時的地址可能已經改變。所以設計中在讀寫信號的開始時就進行檢測,并將結果保存,以供在讀寫信號結束時判斷是否翻轉觸發器。

所以系統中先后觸發器有四個邊治檢測器,兩個用來檢測端口讀寫信號的開始,兩個用來檢測端口讀寫信號的結束。

3.6連續傳輸時SI狀態加載高8位地址控制

在DMA連續傳輸時,當地址的低8位從ox00向oxFF變化時,或從oxFT向ox00變化時,需要進入引狀態加載已經變化了的高8位地址。因為地址加1減1邏輯不是用計數器實現的,所以無法采用低8位的進位借位信號進行判斷。設計中采用將高8位的最低位值與運算后得到的值進行異或(XOR),該值的作用就如同進位借位標志。

4、實現與驗證

對于可編程DMA控制器IP的設計實現是采用TOp-down設計方法,首先建立了一個可供仿真的頂層模型,在仿真環境中確定了各種控制信號的時序關系,之后才使用具體的功能電路逐步細化整個系統。這種設計方法,可以在設計的初期就能夠發現結構設計中存在的錯誤和瓶頸,以避免反復設計。由于可編程DMA控制器IP是同步電路,所以在設計中盡量采用各種同步信號,并且采用一些措施來減少組合路徑的延遲,提高系統的工作時鐘頻率,同時消除毛刺,使電路性能更加穩定。

在設計中,作者采用VHDL(VHSIHaldDtSCriptionban-gUage)語言編寫代碼。利用SynoPsys的Design-Analyzer進行編譯和綜合。采用iii,nx驗證IP正確性,采用Altera的MAX-Plus11進行布局布線,選擇ALrFERA的Fled0K30器件,進行了片上驗證。與ALTERA公司提供的8237AIP進行比較,資源占用基本一致,時序分析時性能較好。

在進行ASIC門級后仿真(P0st-simulation)時,采用的是標準的vrrsLtiny,采用cnosl藝,線寬為o.5微米,具有Sin-of性質。提取了布局布線后的各種延遲信息后,在Sn-0PSyS的VSS中進行仿真,驗證了IP的正確性。

5、結論

可編程DMA控制器IP設計實現了IP設計的目標,即設計的重用,實現了一些相應單元模塊的參數化設計。只需要進行很少量的參數修改工作,就可以重構一個適用于不同需求的DMA控制器,例如可以將四個通道進行裁減。而且可以根據實現工藝(ASIC或FPGA)的不同,設定相應參數,選擇合適的設計。

國內對于IP的設計研究還是剛剛開始,通過可編程DMA控制器IP設計可以獲得經驗。在設計中作者基本按照TOP-down的設計方法。在實際驗證時整個電路的各項參數都達到了Intel手冊上提供的參數,電路工作正常,這說明高層設計方法在數字電路的設計工作中是有效的,這個設計也作為這方面的一個探索。

電子發燒友App

電子發燒友App

評論