AXI (Advanced eXtensible Interface) 本是由ARM公司提出的一種總線協議, Xilinx從 6 系列的 FPGA 開始對 AXI 總線提供支持,目前使用 AXI

2020-12-04 12:22:44 6179

6179

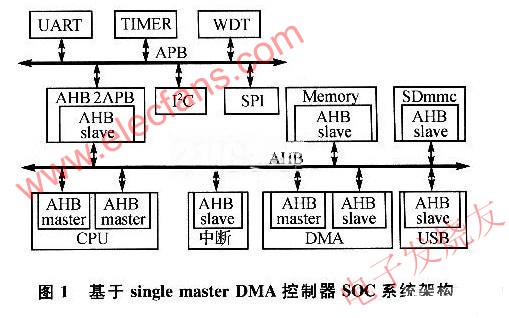

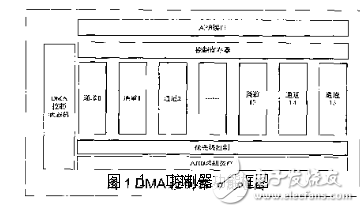

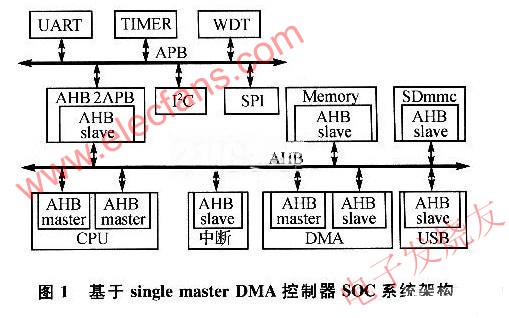

斷給中斷控制器; 5. 擁有8個DMA觸發事件并且可以編碼控制; 6. 128個(64bit)的MFIFO,在傳輸的時候讀寫端可寫入到此FIFO; 7. 支持任意內存到內存的傳輸; 整個系統中的DMA

2020-12-05 10:17:17 3606

3606 前面一節我們學會了創建基于AXI總線的IP,但是對于AXI協議各信號的時序還不太了解。這個實驗就是通過SDK和Vivado聯合調試觀察AXI總線的信號。由于我們創建的接口是基于AXI_Lite協議

2020-12-23 15:32:37 2169

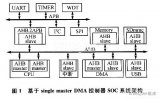

2169 構成的傳輸數據的通道, 一般由數據線、地址線、 控制線構成。?Xilinx從6系列的 FPGA 開始對 AXI 總線提供支持, 此時 AXI 已經發展到

2020-12-25 14:07:02 2957

2957

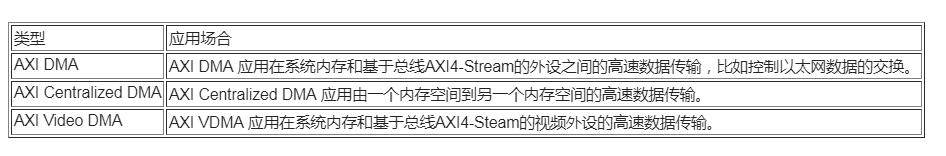

一、AXI DMA介紹 本篇博文講述AXI DMA的一些使用總結,硬件IP子系統搭建與SDK C代碼封裝參考米聯客ZYNQ教程。若想讓ZYNQ的PS與PL兩部分高速數據傳輸,需要利用PS的HP

2020-12-31 09:52:02 7165

7165

利用AXI-DMA批量發送數據到DMAinit_intr_sys函數分析

2021-03-10 06:57:39

AXI總線學習AXI協議的主要特征主要結構通道定義讀寫地址通道讀數據通道寫數據通道寫操作回應信號接口和互聯寄存器片基本傳輸Read burstOverlapping read burstWrite

2022-02-09 07:17:23

1 DMA系統簡介DMA(direct memory access)是一種外設與存儲器或者存儲器與存儲器之間直接傳輸數據的方式,在進行DMA存取時,CPU讓出總線控制權,不在采用輸入輸出指令的方法

2021-07-26 08:11:30

DMA控制器8237A是什么工作原理?DMA控制器8237A的引腳功能及工作方式是什么?

2021-09-18 06:48:59

本帖最后由 yyeee312 于 2015-11-12 15:17 編輯

DMA控制器是一種在系統內部轉移數據的獨特外設,可以將其視為一種能夠通過一組專用總線將內部和外部存儲器與每個具有DMA

2015-11-04 22:50:56

DMA控制器的主要用途是什么?GPIO引腳的I/O端口有何作用?

2022-01-25 06:59:37

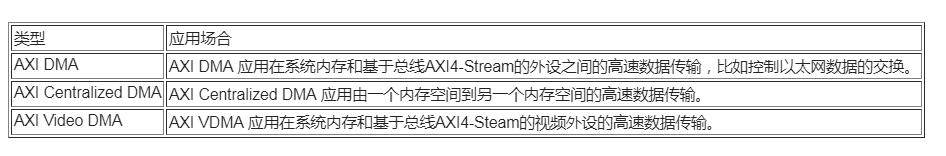

;獨立的控制和狀態流通道,提供相關的包信息;DMA的中斷與系統中斷控制器相連。 (2) AXI Centralized DMA 圖4?41 AXI CDMA 在此系統中,AXI CDMA與處理器

2020-12-23 17:48:04

大家好, 我通過dma tx通道(AXI DMA0)將數據發送到fpga。幾秒鐘后,我希望通過DMA rx通道接收某些字節。執行下面的代碼后(請參考CODE1 :)我正在檢查tx通道的第1位狀態

2020-04-14 07:31:36

。

?適用于具有高初始訪問延遲的內存控制器。

?提供了實現互連架構的靈活性。

?向后兼容AHB和APB接口。

AXI協議的主要特點是:

?獨立的地址/控制和數據階段。

?支持使用字節選通進行未對齊的數據傳輸

2023-08-02 09:44:08

ARM處理器中有些總線APB AHB AXI 3 AXI 4,他們的有什么不同,各自作用?

2023-10-24 07:16:36

CoreLink DMA-350是一款具有AMBA?AXI5接口的直接內存訪問控制器(DMAC),

它提供快速存儲器到存儲器、外圍設備到存儲器、存儲器到外圍設備拷貝,以及

多個通道上的外設到外設能力

2023-08-02 08:03:53

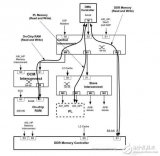

DMA-330周期型號是一款高性能、面積優化的SDRAM或移動SDR內存控制器,可為DMA傳輸提供AXI接口。

它由兩個APB接口編程和控制,一個在TrustZone安全模式下運行,另一個在非安全

2023-08-16 06:41:45

EtherCAT總線運動控制器硬件是如何進行接線的?EtherCAT總線運動控制器有哪些參數設置?

2021-07-15 13:02:24

的理解:1)DMA連接到IP總線。2)OCRAM連接到AXI64總線。3) ITCM和DTCM連接到TCM接口。是否可以將 DMA 緩沖區放在 OCRAM 中,將任務的緩沖區放在 DTCM 或 ITCM

2023-04-04 07:09:50

我已經通過AXI互連將用于PCI Express的DMA子系統連接到DDR4控制器IP。然而,這是在塊設計之外完成的。實際上我沒有使用塊設計。如果我使用塊設計,地址編輯器將出現在一個選項卡中,可以指定每個塊的AXI地址。但是如果沒有塊設計,我該如何打開地址編輯器?

2020-05-08 07:30:19

PL341內存控制器是一款高性能、面積優化的DDR2 SDRAM內存控制器,兼容高級微控制器總線架構(AMBA)AXI協議。

有關AXI協議的詳細說明,請參閱AMBA AXI協議規范。

本節總結了周期模型的功能與硬件的功能,以及周期模型的性能和準確性。

2023-08-12 06:01:49

μDMAC是一種符合高級微控制器總線架構(AMBA)的片上系統(SoC)外圍設備,由ARM開發、測試和許可。

它是一個非常低的門計數DMA控制器,與AMBA AHB Lite協議兼容

2023-08-02 15:36:45

PL340內存控制器是一款高性能、面積優化的SDRAM或移動SDR內存控制器,兼容高級微控制器總線架構(AMBA)AXI協議。

有關AXI協議的詳細說明,請參閱AMBA AXI協議規范。

本節總結

2023-08-12 06:25:03

的請求,還有一個仲裁器來協調各個DMA請求的優先權。DMA 控制器和Cortex-M3核共享系統數據總線執行直接存儲器數據傳輸。當CPU和DMA同時訪問相同的目標(RAM或外設)時,DMA請求可能會

2015-01-13 14:02:03

你好,我正在嘗試深入學習 DMA,但在某些時候我很困惑。它是關于總線矩陣和仲裁機制。STM32F446RE中有2個DMA控制器,每個控制器有1條外設總線和1條內存總線。問題不是關于 DMA 的內存

2022-12-27 06:34:33

我正在使用ZC706套件和ISE14.4。我在PL中使用XPS生成AXI.DDR控制器。 AXI.DDR控制器的S_AXI總線通過AXI互連連接到M_AXI_GP1。當我在板上運行它時,我看到

2019-09-10 07:58:12

stm32的dma控制器有多少個通道,DMA簡介直接存儲器存取(DMA)用來提供在外設和存儲器之間或者存儲器和存儲器之間的高速數據傳輸。無須CPU干預,數據可以通過DMA快速地移動,這就節省了CPU

2021-08-05 07:29:16

DMA控制器的主要特性有哪些?DMA控制器通道的配置過程該怎樣去完成呢?

2021-12-13 06:12:53

這篇應用筆記描述了怎么使用STM32F101xx 和 STM32F103xx的直接存儲器訪問(DMA)控制器。STM32F101xx和STM32F103xx的DMA控制器、CortexTM-M3內核

2023-10-10 08:20:48

它們如何用于接口SoC組件。圖6.AXI互連(AXI4規范)結論在本文中,我們介紹了高級微控制器總線體系結構或AMBA。AMBA是一個開放標準,概述了SoC上的組件如何快速有效地交換數據。AMBA

2020-09-28 10:16:11

的控制和狀態流通道,提供相關的包信息;DMA的中斷與系統中斷控制器相連。(2) AXI Centralized DMA圖4?41 AXI CDMA在此系統中,AXI CDMA與處理器等設備通過AXI

2022-10-14 15:23:41

世界的新手。vivado hls用戶指南(Ug902)告訴我,對于ap_memory它不需要總線進行通信,而是一個bram控制器可以完成將數據“饋送”到輸入的工作,所以我添加了一個Bram控制器IP

2019-02-28 13:47:30

我需要設計一個Zynq(可能是Zynq-7030)主板,支持ARM處理器的SATA硬盤驅動器。我想知道是否可以用GTX收發器實現SATA控制器并將其連接到芯片中的AXI總線。是否有任何參考設計或評估板支持此功能?

2020-07-29 10:28:58

STM32F4的DMA控制器有何作用?如何去實現STM32F4的DMA控制器的收發配置呢?

2021-12-07 07:06:57

我能拿到相應的附件的控制器板嗎?1.PSOC3控制器板-CY8C34 46AXI099具有USB接口FRC連接器取出的所有GPIO2.PSOC5控制器板-CY8C5668 AXI-060具有USB接口FRC連接器取出的所有GPIO請向我提供上述建議。謝謝和問候,卡馬拉吉

2019-07-31 11:41:36

`1、在開發zynq工程時遇到多個axi_hp總線讀寫ddr時,總線鎖死。現象就是axi_hp的wready信號一直為低。架構圖: 2、應用write1、wrtie2、read1同時并行讀寫ddr3

2020-04-15 21:57:28

CAN總線及控制器工作原理是什么?流接口驅動程序工作機制是怎樣的?怎樣去設計CAN總線控制器sJAl000驅動程序?

2021-04-27 06:41:09

EtherCAT總線擴展模塊包含哪些?怎樣去使用正運動技術運動控制器EtherCAT總線?

2021-09-27 08:34:04

嗨,我正在使用Zedboard來測試我們的設計。例如,我們正在嘗試使用AXI_DMA,帶有AXI接口的FIFO,帶有AXI接口的自定義邏輯來建立設計。我們正在嘗試執行簡單的環回測試。當我們進行此測試

2019-03-08 13:57:18

直接存儲器存取DMACPU太忙了,那DMA你來幫我吧,這樣很多事情CPU就不用停下來去管了。在DMA模式下,CPU只須向DMA控制器下達指令,讓DMA控制器來處理數據的傳送,數據傳送完畢再把信息反饋

2021-12-09 06:00:30

eXtensibleInterface)協議是一種面向高性能、高帶寬系統設計的總線協議,能夠滿足各種高速系統的總線互聯。AXI協議的主要特點有:●獨立的地址、控制和數據接口●支持使用字節選通的不對齊數據的傳輸

2019-05-06 16:55:32

總線控制器是如何進行驗收濾波的?

2021-05-18 06:28:38

你好,我正在設計一個 PMSM 電機控制器,我有一個問題,PMSM控制器需要直流總線紋波補償嗎?

2024-01-22 07:56:17

通過 DMA 控制器進行介質訪問控制 (MAC)STM32F4xx系列控制器內部集成了一個以太網外設,它實際上是一個通過DMA控制器進行介質訪問控制(MAC),它的功能就是實現MAC 層的任務。借助

2021-08-13 08:47:19

DMA(Direct Memory Access)的概念DMA方式不用處理器干預完成M與I/O間數據傳送。DMA期間系統總線由其它主模塊控

2008-12-09 11:03:56 50

50 引言

DMA(Direct Memory Access,直接存儲器存取)是一種快速傳送數據的機制。DMA控制器能夠有效替代微處理器的加載/存儲指令,顯著提高系統的并行能力。DMA是在

2010-09-08 11:08:36 2281

2281

在以SD卡為圖像存儲器件的圖像協處理器中,基帶芯片和SD卡控制器在速度上的差異經常會導致數據傳輸錯誤。為解決此問題,設計了一種可適應多種時序情況的DMA控制器。該DMA控制器的狀態機,一方面對基帶芯片和SD卡控制器的操作請求進行仲裁,在響應基帶芯片請

2011-01-15 17:06:20 0

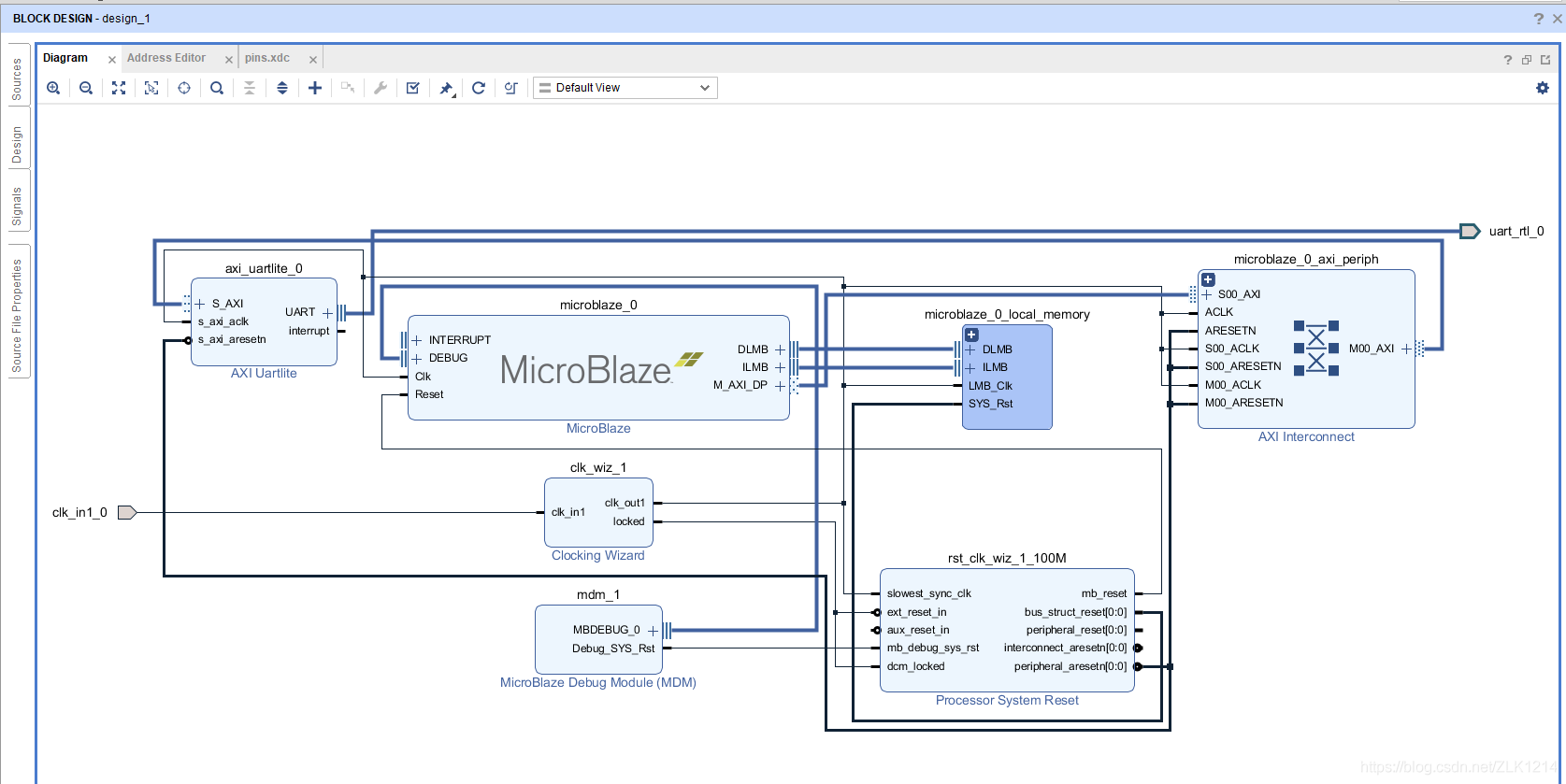

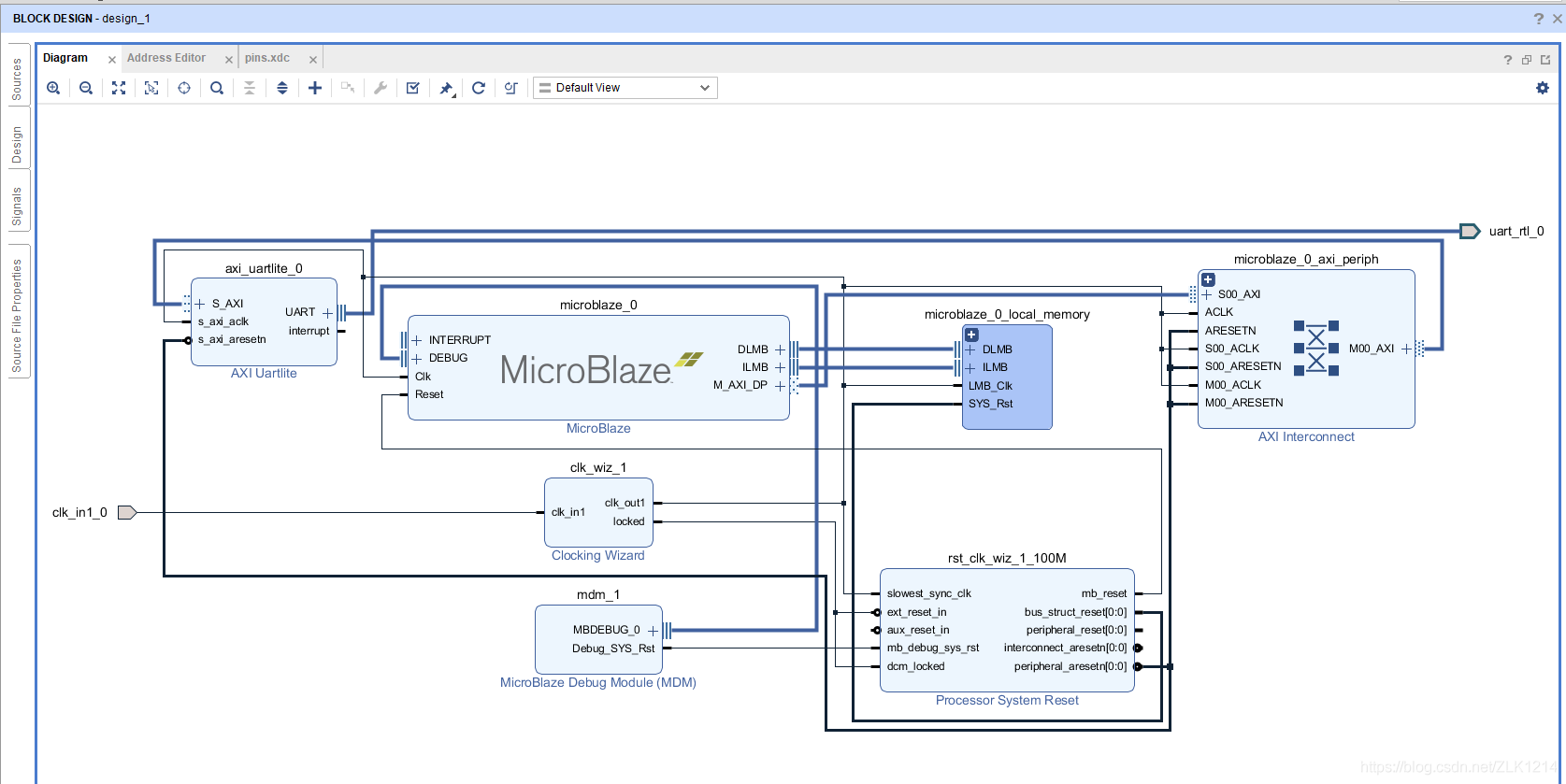

0 目的是利用嵌入在Xilinx FPGA中的MicroBlaze核實現基于AXI總線的雙核嵌入式系統設計以及共享實現LED燈的時控.

2012-03-09 14:17:01 91

91 針對大數據量的串口間通信,在常規的UART串行數據通信的基礎上,結合Cortex-M3微控制器中DMA控制器的作用,實現DMA控制的UART串口數據包收發。設計鏈表項緩存,最終實現DMA的分散/聚集

2012-04-20 10:54:07 46

46 AMBA AXI 總線學習筆記,非常詳細的AXI總線操作說明

2015-11-11 16:49:33 11

11 上周的博客中我們完成了硬件的搭建,并且把硬件部分導入到SDK,見Adam Taylor’s MicroZed Chronicles Part 67: AXI DMA II,下一步通過寫一個簡單的程序

2017-02-08 05:53:11 303

303

上周的博客中我們學習了Zynq SoC的AXI DMA,我解釋了怎樣利用AXI DMA控制器將數據從PL搬運到PS。在本期博客中我們將學習怎樣完成硬件的搭建。 首先我們要更深入的了解一下AXI

2017-02-08 08:10:39 286

286 本文主要介紹zynq linux AXI DMA傳輸步驟教程,具體的跟隨小編一起來了解一下。

2018-07-08 05:46:00 29549

29549

DMA 控制器在外設與主存之間直接傳送數據期間,完全代替 CPU 進行工作。

2017-09-19 16:11:03 6

6 AXI總線的MicroBlaze雙核SoPC系統設計

2017-10-31 08:54:44 8

8 DMA控制器是常見的總線設備之一,很多廠商都有自己的DMA控制器IP核。比如嵌入式處理器的龍頭ARM公司就有自己的DMA控制器解決方案提供給客戶,另外像Freescale,Fujitsu等芯片

2017-12-06 13:41:59 3329

3329

介紹一種基于PCI總線的高效鏈式DMA控制器的設計與實現,用于高速寬帶的計算機外設接口。利用Altera公司的PCI核——PCI_MT32搭建基于此控制器的數據采集平臺,并成功應用在DVB數據接收卡中。

2017-12-06 13:56:13 2782

2782

DMA(Direct Memory Access)控制器是一種在系統內部轉移數據的獨特外設,可以將其視為一種能夠通過一組專用總線將內部和外部存儲器與每個具有DMA能力的外設連接起來的控制器。它之所以屬于外設,是因為它是在處理器的編程控制下來 執行傳輸的。

2017-12-06 19:19:12 3458

3458 DMA控制器是一種在系統內部轉移數據的獨特外設,可以將其視為一種能夠通過一組專用總線將內部和外部存儲器與每個具有DMA能力的外設連接起來的控制器。它之所以屬于外設,是因為它是在處理器的編程控制下來 執行傳輸的。

2017-12-07 08:51:27 2024

2024

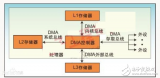

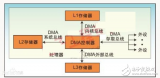

為了具體介紹本多通道 DMA 控制器的設計方案,下面首先對基于 Crossbar 的多通道 DMA 控制器的工作原理進行詳細分析,接著具體說明各個模塊的設計實現,然后對設計進行驗證和分析比較實驗結果,并進行總結。

2017-12-07 09:37:22 4585

4585

DMA既可以指內存和外設直接存取數據這種內存訪問的計算機技術,又可以指實現該技術的硬件模塊(對于通用計算機PC而言,DMA控制邏輯由CPU和DMA控制接口邏輯芯片共同組成,嵌入式系統的DMA控制器內建在處理器芯片內部,一般稱為DMA控制器,DMAC)。

2017-12-07 10:23:24 15810

15810

DMA(Direct Memory Access)控制器是一種在系統內部轉移數據的獨特外設,可以將其視為一種能夠通過一組專用總線將內部和外部存儲器與每個具有DMA能力的外設連接起來的控制器。它之所以屬于外設,是因為它是在處理器的編程控制下來 執行傳輸的。

2017-12-07 14:43:14 3368

3368

DMA控制器是一種在系統內部轉移數據的獨特外設,可以將其視為一種能夠通過一組專用總線將內部和外部存儲器與每個具有DMA能力的外設連接起來的控制器。它之所以屬于外設,是因為它是在處理器的編程控制下來 執行傳輸的。

2017-12-07 15:41:09 3168

3168

DMA既可以指內存和外設直接存取數據這種內存訪問的計算機技術,又可以指實現該技術的硬件模塊(對于通用計算機PC而言,DMA控制邏輯由CPU和DMA控制接口邏輯芯片共同組成,嵌入式系統的DMA控制器內建在處理器芯片內部,一般稱為DMA控制器,DMAC)。

2017-12-07 16:08:38 5155

5155

基于前面對DMA控制器工作流程的詳細分析。運用SystemC 語言,建立DMA控制器的Cye le-Accurat級參考模型。控制器由以下幾個模塊組成:寄存器賦值、狀態轉換。輸出模塊和頂層模塊。具體工作過程可以參考如圖3所示的有限狀態機

2017-12-07 16:21:12 2350

2350

1、AXI 總線通道,總線和引腳的介紹 AXI接口具有五個獨立的通道: (1)寫地址通道(AW):write address channel (2)寫數據通道( W): write data

2018-01-05 08:13:47 9601

9601

本文實現的基于FPGA的PCIe總線接口的DMA控制器是在Altera PHY IP和Synopsys Core IP的基礎上實現的,利用Synopsys VIP驗證環境進行了功能仿真驗證

2018-01-11 10:57:04 11281

11281

在圖1所示架構中,每次DMA傳輸都要發起1次讀與1次寫操作。若在DMA傳輸期間有需要緊急處理的異常響應,AHB總線此時又被DMA控制器占用,則處理器只能等DMA控制器釋放AHB總線后才能占用AHB總線進行操作,影響處理器效率與系統對異步事件的響應速度。

2018-08-24 15:34:53 1563

1563

一個DMA控制器,實際上是采用DMA方式的外圍設備與系統總線之間的接口電路,這個接口電路是在中斷接口的基礎上再加DMA機構組成。習慣上將DMA方式的接口電路稱為DMA控制器。

2019-04-01 16:08:06 10025

10025 DMA(Direct Memory Access)控制器是一種在系統內部轉移數據的獨特外設,可以將其視為一種能夠通過一組專用總線將內部和外部存儲器與每個具有DMA能力的外設連接起來的控制器。它之所以屬于外設,是因為它是在處理器的編程控制下來 執行傳輸的。

2019-11-15 10:25:56 12384

12384 在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三種總線,但PS與PL之間的接口卻只支持前兩種,AXI-Stream只能在PL中實現,不能直接和PS相連,必須通過AXI

2020-09-24 09:50:30 4289

4289

XDMA是Xilinx封裝好的PCIE DMA傳輸IP,可以很方便的把PCIE總線上的數據傳輸事務映射到AXI總線上面,實現上位機直接對AXI總線進行讀寫而對PCIE本身TLP的組包和解包無感。

2020-12-28 10:17:23 2692

2692 不同類型的DMA GPIO PL general purpose AXI GP AXI utlilizing PS DMAC High performance w/DMA ACP w/DMA 幾種

2020-10-09 18:05:57 6390

6390

基于AXI的DMA對內部寄存器的讀寫有著相同的方式。在普通傳輸模式下,DMA內部的寄存器都是由處理器通過AXI-Lite總線進行讀寫的;但基于AXI總線的三種DMA,都增加了S/G傳輸模式,它卸載

2020-10-10 10:23:37 6203

6203

ZYNQ中DMA與AXI4總線 為什么在ZYNQ中DMA和AXI聯系這么密切?通過上面的介紹我們知道ZYNQ中基本是以AXI總線完成相關功能的: 圖4?34連接 PS 和 PL 的 AXI 互聯

2020-11-02 11:27:51 3880

3880

在 AMBA 系列之 AXI 總線協議初探 中,了解到 AXI 總線交互分為 Master / Slave 兩端,而且標準的 AXI 總線支持不同的位寬,既然是總線,那么必須要支持總線互聯,多 Master,多 Slave的場景

2022-02-08 11:44:02 12802

12802 在介紹AXI之前,先簡單說一下總線、接口以及協議的含義。總線、接口和協議,這三個詞常常被聯系在一起,但是我們心里要明白他們的區別。

2021-02-04 06:00:15 10

10 本系列我想深入探尋 AXI4 總線。不過事情總是這樣,不能我說想深入就深入。當前我對 AXI總線的理解尚談不上深入。但我希望通過一系列文章,讓讀者能和我一起深入探尋 AXI4。

2021-03-17 21:40:29 25

25 AXI是個什么東西呢,它其實不屬于Zynq,不屬于Xilinx,而是屬于ARM。它是ARM最新的總線接口,以前叫做AMBA,從3.0以后就稱為AXI了。

2021-04-09 17:10:10 4970

4970

本系列我想深入探尋 AXI4 總線。不過事情總是這樣,不能我說想深入就深入。當前我對 AXI總線的理解尚談不上深入。但我希望通過一系列文...

2022-02-07 11:36:33 4

4 本文以浮點數Floating-point IP核將定點數轉換為浮點數為例,詳細講解AXI DMA IP核的使用方法。

2022-02-16 16:21:37 7545

7545

AXI (高性能擴展總線接口,Advanced eXtensible Interface)是ARM AMBA 單片機總線系列中的一個協議,是計劃用于高性能、高主頻的系統設計的。AXI協議是被優化

2022-10-10 09:22:22 8632

8632 AN3109_用STM32F10x微控制器的DMA和DMA超時仿真通信外設FIFO

2022-11-21 08:11:29 0

0 AN4104_STM32F0xx的DMA控制器的使用

2022-11-21 08:11:37 2

2 在zynq開發過程中,AXI總線經常遇到,每次看到AXI總線相關的信號時都一頭霧水,仔細研究一下,將信號分分類,發現其實也不難。

2023-05-25 11:22:54 570

570

從 FPGA 應用角度看看 AMBA 總線中的 AXI4 總線。

2023-06-21 15:21:44 1729

1729

電子發燒友網站提供《STM32F0xx的DMA控制器的使用.pdf》資料免費下載

2023-09-21 14:49:49 0

0 LogiCORE?IPAXI IIC總線接口連接到AMBA?AXI規范,提供低速、兩線串行總線接口,可連接大量流行的設備。

2023-09-28 15:56:16 4484

4484 LogiCORE IP AXI 通用異步接收發送器 (UART) 16550 連接到高級微控制器總線架構 (AMBA) AXI,為異步串行數據傳輸提供控制器接口。該軟 IP 核旨在通過 AXI4-Lite 接口進行連接。

2023-10-16 11:02:01 1762

1762

由由數據線、地址線、控制線等構成。 接口是一種連接標準,又常常被稱之為物理接口。 協議是傳輸數據的規則。 1.簡介 AXI4總線協議是 ARM 公司 提出的AMBA( Ad vanced Microcontroller Bus Archi te cture)3.0協議中最重要的部分,是一種面向高性能、高帶

2023-12-16 15:55:01 248

248 Transaction Layer的所有功能特性,不僅內置DMA控制器,而且具備AXI4用戶接口,提供一個高性能,易于使用,可定制化的PCIe-AXI互連解決方案,同時適用于ASIC和FPGA。

2024-02-21 15:15:03 144

144

Transaction layer的所有功能特性,不僅內置DMA控制器,而且具備AXI4用戶接口,提供一個高性能,易于使用,可定制化的PCIe-AXI互連解決方案,同時適用于ASIC和FPGA。

2024-02-22 09:15:46 0

0 或Scather Gather DMA,提供FIFO/AXI4-Stream用戶接口。

基于PCI Express Integrated Block,Multi-Channel PCIe RDMA

2024-02-22 11:11:55 156

156

電子發燒友App

電子發燒友App

評論