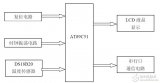

89C52是INTEL公司MCS-51系列單片機中基本的產品,它采用ATMEL公司可靠的CMOS工藝技術制造的高性能8位單片機,屬于標準的MCS-51的HCMOS產品。

它結合了CMOS的高速和高密度技術及CMOS的低功耗特征,它基于標準的MCS-51單片機體系結構和指令系統,屬于89C51增強型單片機版本,集成了時鐘輸出和向上或向下計數器等更多的功能,適合于類似馬達控制等應用場合。

89C52內置8位中央處理單元、512字節內部數據存儲器RAM、8k片內程序存儲器(ROM)32個雙向輸入/輸出(I/O)口、3個16位定時/計數器和5個兩級中斷結構,一個全雙工串行通信口,片內時鐘振蕩電路。此外,89C52還可工作于低功耗模式,可通過兩種軟件選擇空閑和掉電模式。在空閑模式下凍結CPU而RAM定時器、串行口和中斷系統維持其功能。掉電模式下,保存RAM數據,時鐘振蕩停止,同時停止芯片內其它功能。89C52有PDIP(40pin)和PLCC(44pin)兩種封裝形式。

AT89C52是一個低電壓,高性能CMOS 8位單片機,片內含8k bytes的可反復擦寫的Flash只讀程序存儲器和256 bytes的隨機存取數據存儲器(RAM),器件采用ATMEL公司的高密度、非易失性存儲技術生產,兼容標準MCS-51指令系統,片內置通用8位中央處理器和Flash存儲單元,AT89C52單片機在電子行業中有著廣泛的應用。

AT89C52有40個引腳,32個外部雙向輸入/輸出(I/O)端口,同時內含2個外中斷口,3個16位可編程定時計數器,2個全雙工串行通信口,2 個讀寫口線,AT89C52可以按照常規方法進行編程,也可以在線編程。其將通用的微處理器和Flash存儲器結合在一起,特別是可反復擦寫的 Flash存儲器可有效地降低開發成本。

AT89C52有PDIP、PQFP/TQFP及PLCC等三種封裝形式,以適應不同產品的需求。

1、兼容MCS51指令系統

2、8kB可反復擦寫(大于1000次)Flash ROM;

3、32個雙向I/O口;

4、256x8bit內部RAM;

5、3個16位可編程定時/計數器中斷;

6、時鐘頻率0-24MHz;

7、2個串行中斷,可編程UART串行通道;

8、2個外部中斷源,共6個中斷源;

9、2個讀寫中斷口線,3級加密位;

10、低功耗空閑和掉電模式,軟件設置睡眠和喚醒功能;

11、有PDIP、PQFP、TQFP及PLCC等幾種封裝形式,以適應不同產品的需求。

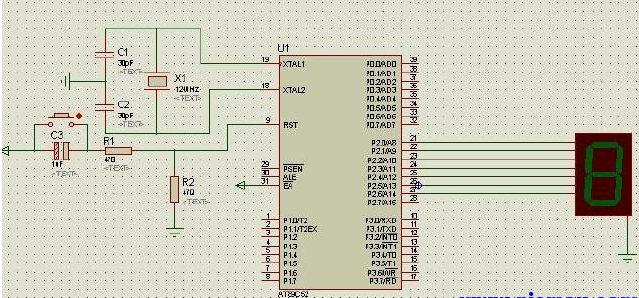

AT89C52為8 位通用微處理器,采用工業標

PDIP封裝的AT89C52引腳圖 準的C51內核,在內部功能及管腳排布上與通用的8xc52 相同,其主要用于會聚調整時的功能控制。功能包括對會聚主IC 內部寄存器、數據RAM及外部接口等功能部件的初始化,會聚調整控制,會聚測試圖控制,紅外遙控信號IR的接收解碼及與主板CPU通信等。主要管腳有:XTAL1(19 腳)和XTAL2(18 腳)為振蕩器輸入輸出端口,外接12MHz 晶振。RST/Vpd(9 腳)為復位輸入端口,外接電阻電容組成的復位電路。VCC(40 腳)和VSS(20 腳)為供電端口,分別接+5V電源的正負端。P0~P3 為可編程通用I/O 腳,其功能用途由軟件定義,在本設計中,P0 端口(32~39 腳)被定義為N1 功能控制端口,分別與N1的相應功能管腳相連接,13 腳定義為IR輸入端,10 腳和11腳定義為I2C總線控制端口,分別連接N1的SDAS(18腳)和SCLS(19腳)端口,12 腳、27 腳及28 腳定義為握手信號功能端口,連接主板CPU 的相應功能端,用于當前制式的檢測及會聚調整狀態進入的控制功能。

P0 口

P0 口是一組8 位漏極開路型雙向I/O 口, 也即地址/數據總線復用口。作為輸出口用時,每位能吸收電流的

方式驅動8 個TTL邏輯門電路,對端口P0 寫“1”時,可作為高阻抗輸入端用。

在訪問外部數據存儲器或程序存儲器時,這組口線分時轉換地址(低8 位)和數據總線復用,在訪問期間激活內部上拉電阻。

在Flash編程時,P0 口接收指令字節,而在程序校驗時,輸出指令字節,校驗時,要求外接上拉電阻。

P1 口

P1 是一個帶內部上拉電阻的8 位雙向I/O 口, P1 的輸出緩沖級可驅動(吸收或輸出電流)4 個TTL 邏輯

門電路。對端口寫“1”,通過內部的上拉電阻把端口拉到高電平,此時可作輸入口。作輸入口使用時,因為內部存在上拉

電阻,某個引腳被外部信號拉低時會輸出一個電流(IIL)。

與AT89C51 不同之處是,P1.0 和P1.1 還可分別作為定時/計數器2 的外部計數輸入(P1.0/T2)和輸入(P1.1/T2EX),

參見表1。

Flash 編程和程序校驗期間,P1 接收低8 位地址。

表.P1.0和P1.1的第二功能

引腳號功能特性

P1.0T2,時鐘輸出

P1.1T2EX(定時/計數器2)

P2 口

P2 是一個帶有內部上拉電阻的8 位雙向I/O 口,P2 的輸出緩沖級可驅動(吸收或輸出電流)4 個TTL 邏輯

門電路。對端口P2 寫“1”,通過內部的上拉電阻把端口拉到高電平,此時可作輸入口,作輸入口使用時,因為內部存在上拉電阻,某個引腳被外部信號拉低時會輸出一個電流(IIL)。

在訪問外部程序存儲器或16 位地數據存儲器(例如執行MOVX @DPTR 指令)時,P2 口送出高8 位地址數據。在訪問8 位地址的外部數據存儲器(如執行MOVX@RI 指令)時,P2 口輸出P2鎖存器的內容。

Flash編程或校驗時,P2亦接收高位地址和一些控制信號。

P3 口

P3 口是一組帶有內部上拉電阻的8 位雙向I/O 口。P3 口輸出緩沖級可驅動(吸收或輸出電流)4 個TTL 邏

輯門電路。對P3 口寫入“1”時,它們被內部上拉電阻拉高并可作為輸入端口。此時,被外部拉低的P3 口將用上拉電阻輸出電流(IIL)。

P3 口除了作為一般的I/O 口線外,更重要的用途是它的第二功能

P3 口還接收一些用于Flash閃速存儲器編程和程序校驗的控制信號。

RST

復位輸入。當振蕩器工作時,RST引腳出現兩個機器周期以上高電平將使單片機復位。

ALE/PROG

當訪問外部程序存儲器或數據存儲器時,ALE(地址鎖存允許)輸出脈沖用于鎖存地址的低8 位字

節。一般情況下,ALE 仍以時鐘振蕩頻率的1/6 輸出固定的脈沖信號,因此它可對外輸出時鐘或用于定時目的。要注意的是:每當訪問外部數據存儲器時將跳過一個ALE 脈沖。

對Flash存儲器編程期間,該引腳還用于輸入編程脈沖(PROG)。

如有必要,可通過對特殊功能寄存器(SFR)區中的8EH 單元的D0 位置位,可禁止ALE 操作。該位置位后,只有一條

MOVX 和MOVC指令才能將ALE 激活。此外,該引腳會被微弱拉高,單片機執行外部程序時,應設置ALE 禁止位無效。

PSEN

程序儲存允許(PSEN)輸出是外部程序存儲器的讀選通信號,當AT89C52 由外部程序存儲器取指令(或數

據)時,每個機器周期兩次PSEN 有效,即輸出兩個脈沖。在此期間,當訪問外部數據存儲器,將跳過兩次PSEN信號。

EA/VPP

外部訪問允許。欲使CPU 僅訪問外部程序存儲器(地址為0000H—FFFFH),EA 端必須保持低電平(接

地)。需注意的是:如果加密位LB1 被編程,復位時內部會鎖存EA端狀態。

如EA端為高電平(接Vcc端),CPU 則執行內部程序存儲器中的指令。

Flash存儲器編程時,該引腳加上+12V 的編程允許電源Vpp,當然這必須是該器件是使用12V編程電壓Vpp。

XTAL1

XTAL2

振蕩器反相放大器的輸出端。

數據存儲

編輯

AT89C52 有256 個字節的內部RAM,80H-FFH 高128 個字節與特殊功能寄存器(SFR)地址是重疊的,也就是高128字節的RAM 和特殊功能寄存器的地址是相同的,但物理上它們是分開的。

當一條指令訪問7FH 以上的內部地址單元時,指令中使用的尋址方式是不同的,也即尋址方式決定是訪問高128 字節RAM 還是訪問特殊功能寄存器。如果指令是直接尋址方式則為訪問特殊功能寄存器。

例如,下面的直接尋址指令訪問特殊功能寄存器0A0H(即P2 口)地址單元。

MOV 0A0H,#data

間接尋址指令訪問高128 字節RAM,例如,下面的間接尋址指令中,R0 的內容為0A0H,則訪問數據字節地址為0A0H,而不是P2 口(0A0H)。

MOV @R0,#data

堆棧操作也是間接尋址方式,所以,高128 位數據RAM 亦可作為堆棧區使用。

·定時器0和定時器1:

AT89C52的定時器0和定時器1 的工作方式與AT89C51 相同。

電子發燒友App

電子發燒友App

評論