7.1電源管理概述

處理器廣泛地利用門時鐘來禁能那些未用的功能和未用功能塊的輸入,因此只有正在有效使用中的邏輯才會消耗動態功率。

ARMv7-M架構支持為減少功耗而讓Cortex-M3和系統時鐘停止運行的系統睡眠模式。

7.2系統電源管理

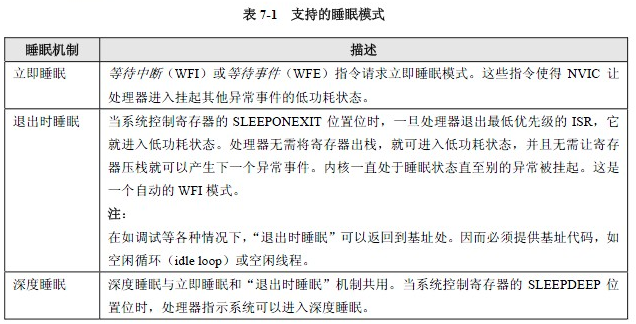

對系統控制寄存器進行寫操作(見“系統控制寄存器”)可以控制Cortex-M3系統功耗的狀態,表7-1列出了支持的睡眠模式。

a.即使沒有異常被激活也可以執行WFI指令。不要使用WFI指令來探測異常是否發生。WFI通常使用

在線程模式下的空閑循環中。要了解更多有關WFI、WFE、BASEPRI以及PRIMASK的信息,請參考

“ARMv7-M架構參考指南”。

處理器導出以下信號以指示處理器進入睡眠的具體時間:

SLEEPING該信號在立即睡眠或“退出時睡眠”模式下有效,表示處理器時鐘可以停

止運行。在接收到一個新的中斷后,NVIC會使該信號變無效,使內核退出睡眠。有關

SLEEPING的用法實例見“SLEEPING”。

SLEEPDEEP當系統控制寄存器的SLEEPDEEP位置位時,該信號在立即睡眠或“退

出時睡眠”模式下有效。該信號被傳送給時鐘管理器,并可以用來門控處理器和包含鎖相環

(PLL)的系統元件以節省功耗。在接收到新的中斷時,嵌套向量中斷控制器(NVIC)將

SLEEPDEEP信號變無效,并在時鐘管理器顯示時鐘穩定時讓內核退出睡眠。有關

SLEEPDEEP的用法實例見“SLEEPDEEP”。

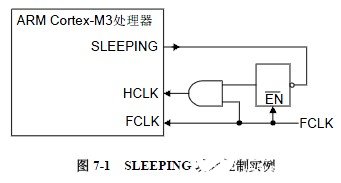

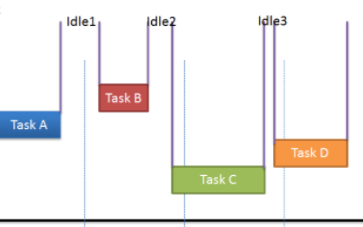

7.2.1 SLEEPING

圖7-1給出了如何在低功耗狀態利用SLEEPING來門控處理器的HCLK時鐘以減少功

耗的實例。如有必要,還可以使用SLEEPING來門控其他系統元件。

為了探測中斷,處理器必須一直接收自由振蕩的FCLK。FCLK用于對以下元件計時:

B)探測中斷的NVIC中的少量邏輯電路

B)DWT和ITM模塊。這些模塊被使能相應功能后可以在睡眠期間產生跟蹤包。如果

“調試異常與監控寄存器”的TRCENA位使能,那些模塊的功耗將會降低。見“調

試異常與監控寄存器”。

在SLEEPING信號有效期間可以降低FCLK頻率。

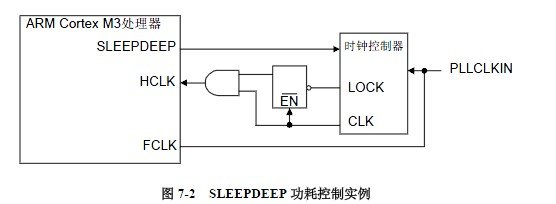

7.2.2 SLEEPDEEP

圖7-2給出了如何在低功耗狀態利用SLEEPDEEP來停止時鐘控制器以進一步減少功耗

的實例。退出低功耗狀態時,LOCK信號指示PLL穩定,并且此時使能Cortex-M3時鐘是

安全的,這可以保證處理器不會重啟直至時鐘穩定。

為了檢測中斷,處理器在低功耗狀態下必須接收自由振蕩的FCLK。在SLEEPDEEP有效期

間可以降低FCLK頻率。

《STM32中文參考手冊_V10.pdf》

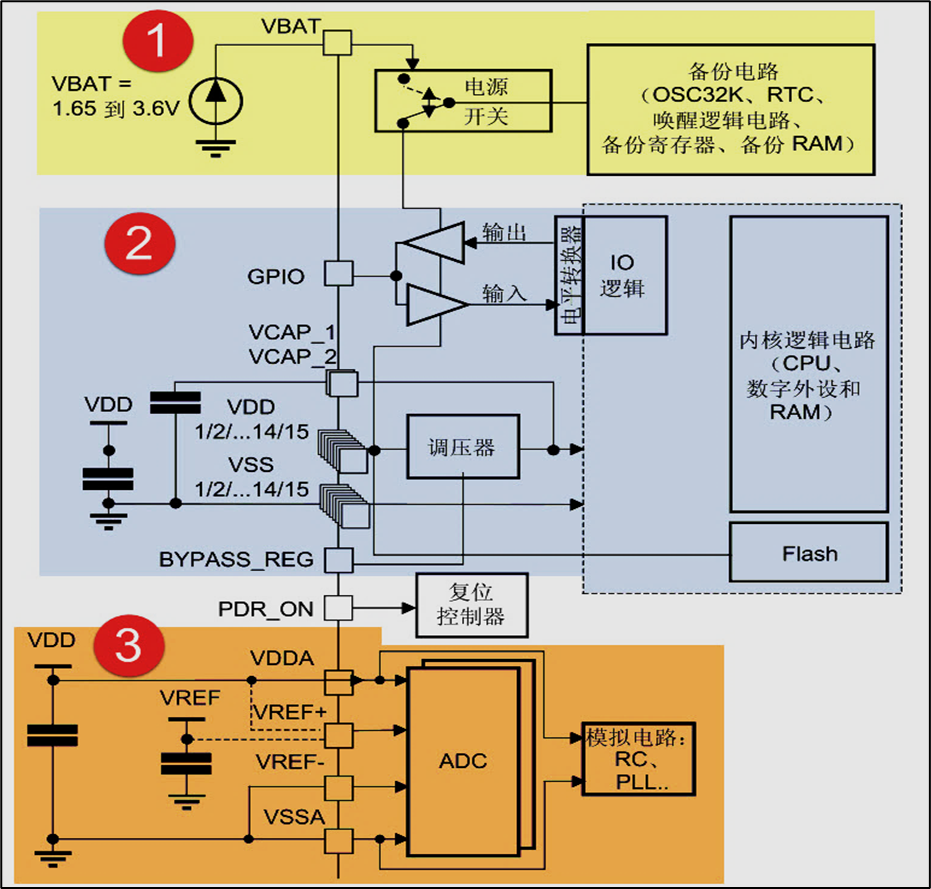

4.1電源

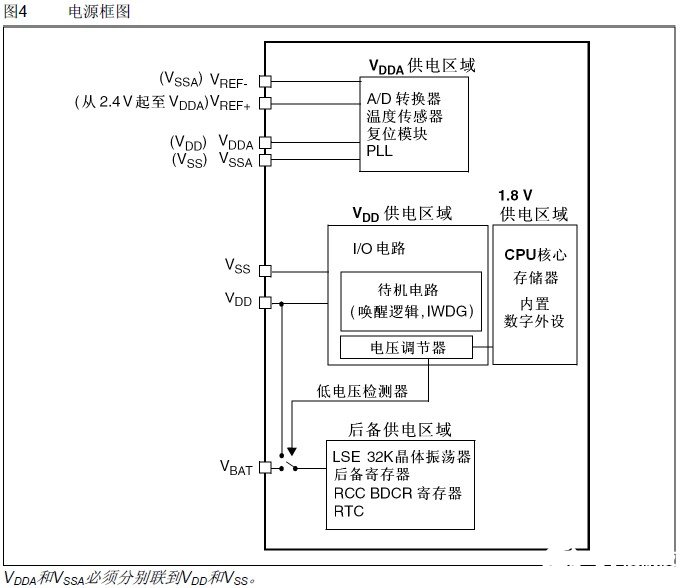

STM32的工作電壓(VDD)為2.0~3.6V。通過內置的電壓調節器提供所需的1.8V電源。 當主電源VDD掉電后,通過VBAT腳為實時時鐘(RTC)和備份寄存器提供電源。

4.1.2電池備份區域使用電池或其他電源連接到VBAT腳上,當VDD斷電時,可以保存備份寄存器的內容和維持RTC的功能。VBAT腳也為RTC、LSE振蕩器和PC13至PC15供電,這保證當主要電源被切斷時RTC能繼續工作。切換到VBAT供電由復位模塊中的掉電復位功能控制。 如果應用中沒有使用外部電池,VBAT必須連接到VDD引腳上。

如果在應用中沒有外部電池,建議VBAT在外部通過一個100nF的陶瓷電容與VDD相連

4.1.3電壓調節器

復位后調節器總是使能的。根據應用方式它以3種不同的模式工作。 ● 運轉模式:調節器以正常功耗模式提供1.8V電源(內核,內存和外設)。

● 停止模式:調節器以低功耗模式提供1.8V電源,以保存寄存器和SRAM的內容。

● 待機模式:調節器停止供電。除了備用電路和備份域外,寄存器和SRAM的內容全部丟失。

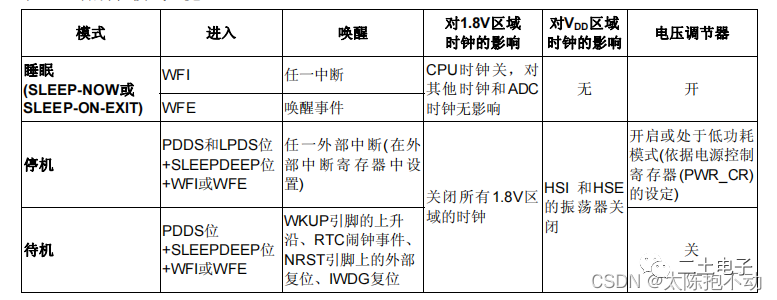

4.3低功耗模式

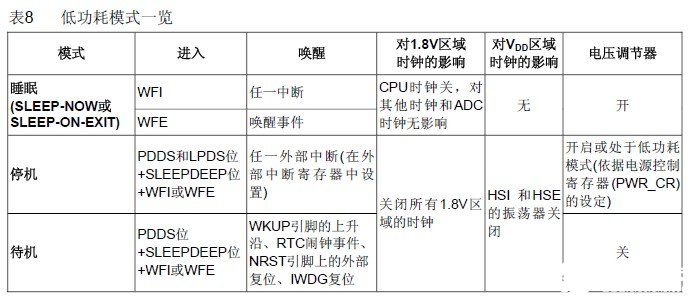

在系統或電源復位以后,微控制器處于運行狀態。當CPU不需繼續運行時,可以利用多種低功耗模式來節省功耗,例如等待某個外部事件時。用戶需要根據最低電源消耗、最快速啟動時間和可用的喚醒源等條件,選定一個最佳的低功耗模式。STM32F10xxx有三種低功耗模式:

● 睡眠模式(Cortex?-M3內核停止,所有外設包括Cortex-M3核心的外設,如NVIC、系統時鐘(SysTick)等仍在運行)

●停止模式(所有的時鐘都已停止)

● 待機模式(1.8V電源關閉)

此外,在運行模式下,可以通過以下方式中的一種降低功耗:

● 降低系統時鐘

●關閉APB和AHB總線上未被使用的外設時鐘。

4.3.1降低系統時鐘

在運行模式下,通過對預分頻寄存器進行編程,可以降低任意一個系統時鐘(SYSCLK、HCLK、PCLK1、PCLK2)的速度。進入睡眠模式前,也可以利用預分頻器來降低外設的時鐘。詳見第6.3.2節:時鐘配置寄存器(RCC_CFGR)。

4.3.2外部時鐘的控制

在運行模式下,任何時候都可以通過停止為外設和內存提供時鐘(HCLK和PCLKx)來減少功耗。 為了在睡眠模式下更多地減少功耗,可在執行WFI或WFE指令前關閉所有外設的時鐘。 通過設置AHB外設時鐘使能寄存器(RCC_AHBENR)、APB2外設時鐘使能寄存器(RCC_APB2ENR)和APB1外設時鐘使能寄存器(RCC_APB1ENR)來開關各個外設模塊的時鐘。

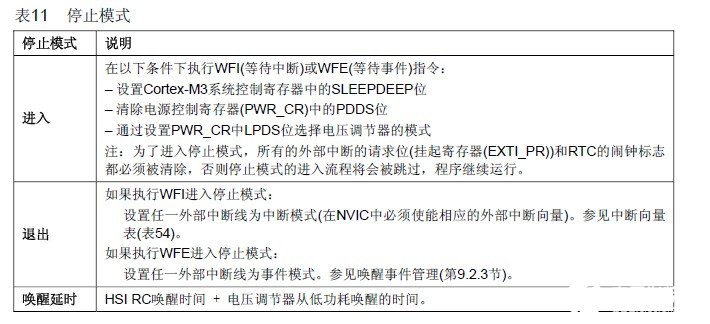

4.3.4停止模式

停止模式是在Cortex?-M3的深睡眠模式基礎上結合了外設的時鐘控制機制,在停止模式下電壓調節器可運行在正常或低功耗模式。此時在1.8V供電區域的的所有時鐘都被停止,PLL、HSI和HSE RC振蕩器的功能被禁止,SRAM和寄存器內容被保留下來。在停止模式下,所有的I/O引腳都保持它們在運行模式時的狀態。進入停止模式關于如何進入停止模式,詳見表11。在停止模式下,通過設置電源控制寄存器(PWR_CR)的LPDS位使內部調節器進入低功耗模式,能夠降低更多的功耗。 如果正在進行閃存編程,直到對內存訪問完成,系統才進入停止模式。 如果正在進行對APB的訪問,直到對APB訪問完成,系統才進入停止模式。 可以通過對獨立的控制位進行編程,可選擇以下功能:

●獨立看門狗(IWDG):可通過寫入看門狗的鍵寄存器或硬件選擇來啟動IWDG。一旦啟動了獨立看門狗,除了系統復位,它不能再被停止。詳見17.3節。

●實時時鐘(RTC):通過備份域控制寄存器(RCC_BDCR)的RTCEN位來設置。

●內部RC振蕩器(LSI RC):通過控制/狀態寄存器(RCC_CSR)的LSION位來設置。

●外部32.768kHz振蕩器(LSE):通過備份域控制寄存器(RCC_BDCR)的LSEON位設置。

在停止模式下,如果在進入該模式前ADC和DAC沒有被關閉,那么這些外設仍然消耗電流。通過設置寄存器ADC_CR2的ADON位和寄存器DAC_CR的ENx位為0可關閉這2個外設。退出停止模式關于如何退出停止模式,詳見下表。當一個中斷或喚醒事件導致退出停止模式時,HSI RC振蕩器被選為系統時鐘。當電壓調節器處于低功耗模式下,當系統從停止模式退出時,將會有一段額外的啟動延時。如果在停止模式期間保持內部調節器開啟,則退出啟動時間會縮短,但相應的功耗會增加。

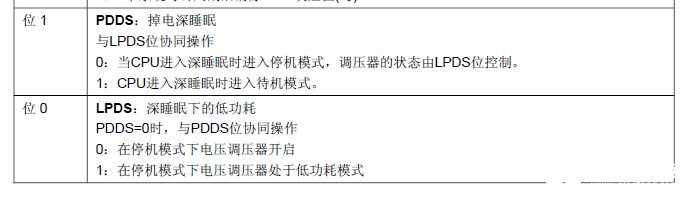

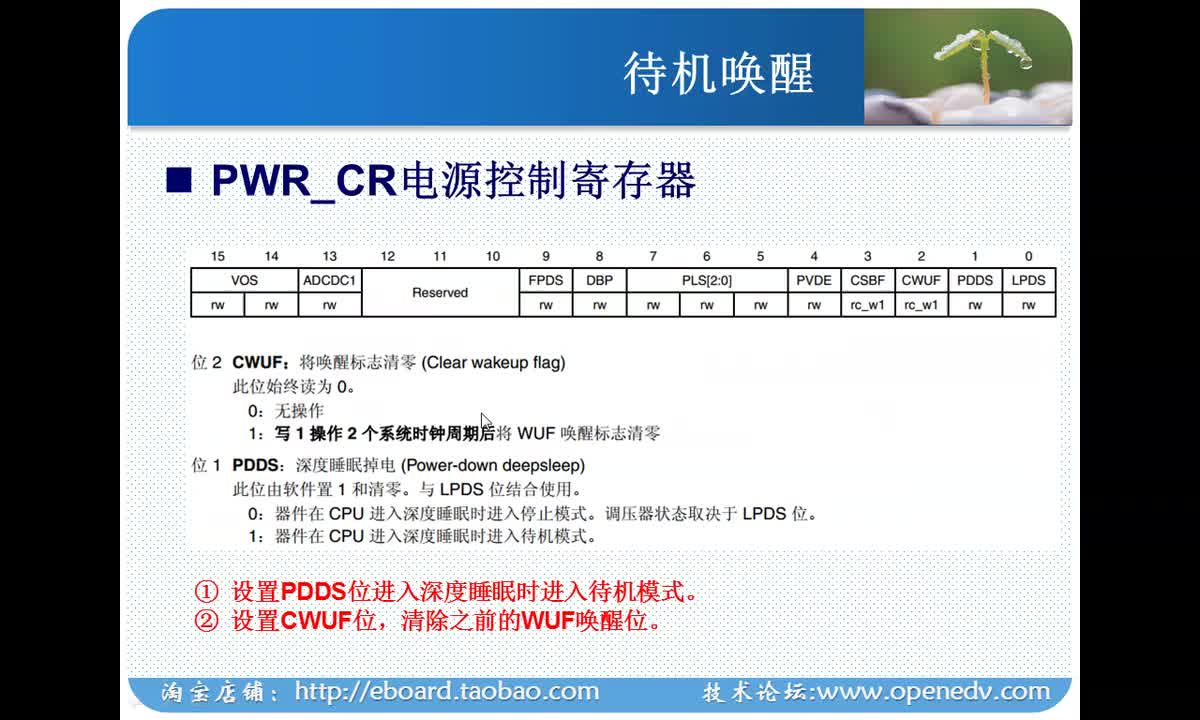

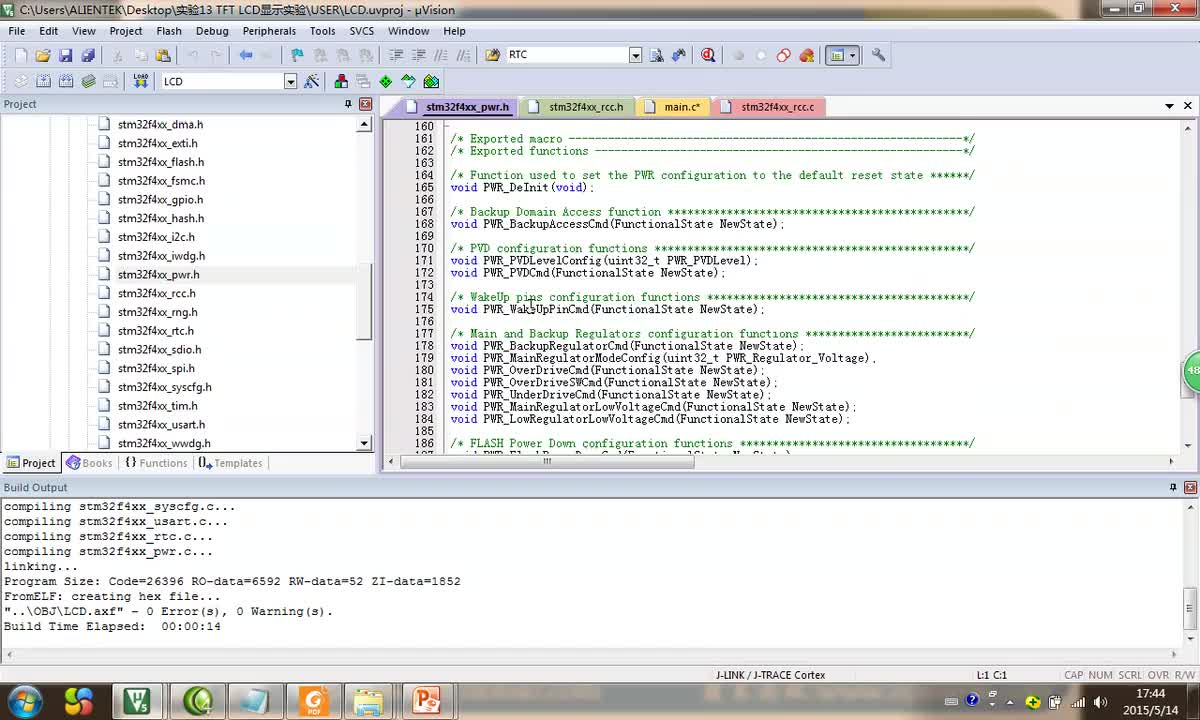

其中對PWR_CR的PDDS和LPDS的配置:

//進入停止模式

{

//的LPDS并清除PWR_CR的PDDS

u32 tmpreg tmpreg = PWR-》CR;

tmpreg &= ~(1《《1); //清除PWR_CR的PDDS

tmpreg “=(1《《0); //設置PWR_CR的LPDS

PWR-》CR = tmpreg;

SCB-》SCR|=1《《2; //使能SLEEPDEEP位(SYS-》CTRL)

WFI_SET(); //執行WFI指令

}

其中THUMB指令不支持匯編內聯,采用如下方法實現執行匯編指令WFI

__asm void __inline WFI_SET(void)

{

WFI;

}

4.3.5待機模式

待機模式可實現系統的最低功耗。該模式是在Cortex-M3深睡眠模式時關閉電壓調節器。整個1.8V供電區域被斷電。PLL、HSI和HSE振蕩器也被斷電。SRAM和寄存器內容丟失。只有備份的寄存器和待機電路維持供電。

進入待機模式

關于如何進入待機模式,詳見表12。 可以通過設置獨立的控制位,選擇以下待機模式的功能:

● 獨立看門狗(IWDG):可通過寫入看門狗的鍵寄存器或硬件選擇來啟動IWDG。一旦啟動了獨立看門狗,除了系統復位,它不能再被停止。

● 實時時鐘(RTC):通過備用區域控制寄存器(RCC_BDCR)的RTCEN位來設置。

● 內部RC振蕩器(LSI RC):通過控制/狀態寄存器(RCC_CSR)的LSION位來設置。

● 外部32.768kHz振蕩器(LSE):通過備用區域控制寄存器(RCC_BDCR)的LSEON位設置。 退出待機模式。

當一個外部復位(NRST引腳)、IWDG復位、WKUP引腳上的上升沿或RTC鬧鐘事件的上升沿發生時,微控制器從待機模式退出。從待機喚醒后,除了電源控制/狀態寄存器(PWR_CSR)(見第4.4.2節),所有寄存器被復位。

責任編輯;zl

電子發燒友App

電子發燒友App

評論