基于TMS320DM6446的H.264編碼器實現與優化

1 引言

H.264是ITU-T的視頻編碼專家組(VCEG)和ISO/IEC的活動圖像專家組(MPEG)聯合制定的視頻壓縮標準。它在H.263/H.263++的基礎上發展,在繼承所有編碼壓縮技術優點的同時引入許多全新的編碼技術和網絡適配層NAL的概念,從而擁有更高的編碼效率和更好的網絡適配性。為從低碼率的實時通信系統或無線環境到高碼率的HDTV和數字存儲系統提供一個優良的視頻壓縮編碼通用工具。但H.264標準優異的性能表現是以編碼運算復雜度和運算量大為代價,在通用的PC機平臺實現會占用較大的CPU和內存資源。隨著數字信號處理器(DSP)技術的高速發展,DSP的處理速度和能力飛速提高。DSP已滿足H.264標準的編解碼運算速度要求。因此,在穩定的媒體處理器平臺上實現H.264標準有著較好的工程意義和應用前景。

詳細介紹了以TMS320DM6446DSP為核心的視頻編碼系統的硬件設計,并重點研究了H.264編碼器在以TMS320DM 6446為目標的CCS平臺上的移植和優化工作。

2 視頻編碼系統硬件設計

2.1 DSP的選型

DSP選用TI公司的Davinci媒體處理專用器件TMS320DM6446(簡稱DM6446)。它采用ARM+DSP雙核架構,包含一個TMS320C64x+核心和一個ARM926EJ-S核心。C64x+核心采用改進的超長指令字VLIW體系結構,內部擁有8個并行的運算單元,時鐘頻率600 MHz,峰值處理能力高達4 752 MI/s。DM6446片內為兩級高速緩存(Cache)結構,設計有獨立的32位DDR2 SDRAM接口和16位異步EMIF接口。此外,DM6446還集成有多種適用于視音頻多媒體處理的片內資源和接口,如用于和外部解碼器連接的視頻處理前端模塊VPFE、和視頻顯示設備連接的視頻處理后端模塊VPBE、多通道音頻串口等。

DM6446不僅在處理性能上完全滿足H.264標準要求。而且在內部結構、片內資源和外部接口上對視頻處理應用專門優化,大大降低視頻應用的開發難度和成本。

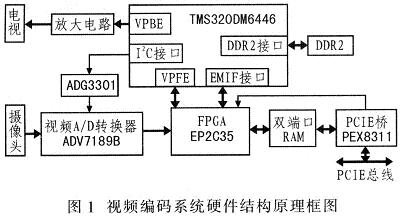

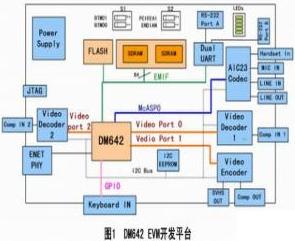

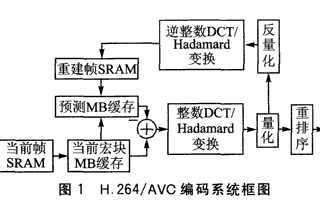

2.2 系統結構框圖

視頻編碼系統硬件結構原理框圖如圖1所示。主機通過PCIE總線對DSP進行初始化加載程序。攝像頭輸出的模擬視頻信號經視頻解碼模塊轉換為數字信號,經FPGA轉換電平。通過DM6446的VPFE模塊接口送人DSP,進行壓縮編碼處理。編碼后的視頻數據從DM6446的EMIF接口輸出通過PCIE總線送回主機進行下一步處理。DM6446的VPBE模塊可將采集的數字視頻信號再轉換為模擬信號輸出至電視進行監控。DDR2 SDRAM存儲編碼過程中的原始圖像、參考幀、編碼參數等數據。DM6446通過I2C總線配置A/D轉換器。FPGA與PCIE橋PEX8311之間加入雙端口RAM,以提高數據的傳輸效率。

2.3 視頻解碼模塊設計

模擬視頻信號的傳輸格式種類很多,而且國際上對數字視頻信號的傳輸格式有明確的標準規定,因此一般通用的A/D轉換器并不適合視頻領域應用。這里選用專用的視頻解碼器ADV7189B,它支持12路模擬視頻通道,包含3個具有防噪性能的12位54 MHz的A/D轉換器。支持CVBS、S-端子、YprPb 3種格式的模擬視頻信號輸入,能夠自動偵測NTSL/PAL/SECAM制式,輸出ITU-R BT.656標準的數字視頻信號。選用12路模擬通道中的3路,復用的支持3種模擬視頻格式。ADV7189B輸出10位數字視頻信號、獨立的垂直同步信號VD、水平同步信號HD和像素同步時鐘LLC1,電壓均為3.3 V電平,經過FPGA轉換為DM6446要求的1.8 V,然后從DM6446的VPFE模塊專用數字視頻信號接口送入DSP。壓縮編碼前,VPFE模塊將ITU-R BT.656標準的視頻數據轉換為H.264兼容的YUV4:2:O格式,存入DDR2 SDRAM中。VPFE模塊還支持對視頻數據進行白平衡、縮放等預處理操作。ADG3301實現I2C總線的電平轉換。

2.4 視頻編碼模塊設計

DM6446片內的VPBE模塊包含4個54 MHz的D/A轉換器,可在DM6446內部將數字視頻信號直接轉化為模擬視頻信號,4路輸出,并且支持CVBS、S-端子、YprPb 3種模擬視頻格式。因此,視頻編碼模塊設計較為簡單,只需對4路模擬輸出信號放大,就可直接與監視設備連接。選用TI公司的電壓反饋CMOS運算放大器OPA357進行運算放大。

2.5 控制電路設計

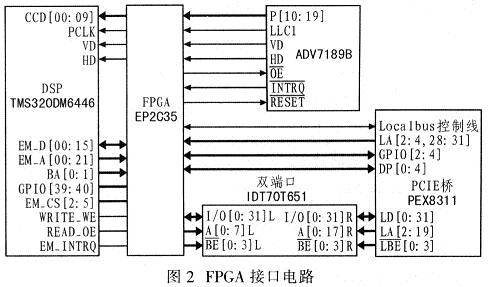

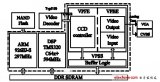

DM6446的視頻信號接口、EMIF接口為1.8 V電平,ADV7189B接口、PCIE橋接口為3.3 V電平。系統需要大量的電平轉換工作,同時還需要實現大量的邏輯控制、PCIE橋與DM6446的通信協議。FPGA器件是最適合的選擇。選用Altera公司的邏輯器件EP2C35,它可在片內實現1.8 V、2.5 V、3.3 V電平的轉換,并且能夠滿足系統對邏輯控制功能的要求。EP2C35內部集成有片內存儲器,可在ADV7189B與DM6446之間建立一個緩存區,提高數據傳輸效率。FPGA與DM6446、ADV7189B和PCIE橋接口電路如圖2所示。

3 H.264編碼器的DSP移植與優化

目前,H.264編碼器的實現版本主要有:JM、T264、X264。其中JM是H.264官方源碼,實現H.264所有特征,但其程序結構冗長,只考慮引入各種新特性以提高編碼性能,忽略編碼復雜度,其復雜度極高,不宜實用;T264編碼器編碼輸出標準的264碼流,解碼器只能解T264編碼器生成的碼流;X264是編碼器注重實用,在不明顯降低編碼性能的前提下,努力降低編碼的計算復雜度。這里,用X264編碼器對DSP平臺移植、優化。X264程序在DSP平臺上實現及優化主要有:程序簡化、代碼移植、代碼優化。

3.1 程序簡化

X264編碼器除支持H.264的基本檔次外,還包含主要檔次的某些功能選項以及其他功能模塊,代碼尺寸較大,因此需要將不必要的功能模塊刪除,以減小代碼尺寸。主要做以下刪減:刪除X264程序中的解碼部分,以及基本檔次功能之外的CABAC、B slice部分;X264程序是基于X86的PC平臺,包含了SSE、MMX等。PC平臺使用的優化技術,在DSP平臺下無效:針對DSP平臺特點,調整刪減后的代碼文件結構。

3.2 代碼移植

TI公司的DSP開發工具CCS具有自己的ANSI C編譯器和優化器,并有自己的語法規則和定義,經過上一步簡化后得到純C版本的X264編碼器需要經過修改才能夠在CCS下應用于具體的DSP。主要包括:①Visual c++、CCS對于變量和結構體的“重復定義”問題的不同處理,需更改頭文件中變量和結構體定義的位置;②用功能相同的庫函數代替CCS中沒有的庫函數,如strncasecmp();③數據格式的不同,用long代替CCS中沒有的_int64格式;④按照CCS下C語言的規則定義數組;⑤修改系統配置參數的讀取方式;⑥編寫針對TMS320DM6446存儲結構的CMD文件。如此,X264便可以在CCS下編譯通過并運行。

3.3 代碼優化

純C版本的X264程序并沒有利用DM6446的資源和并行機制,代碼運行速度極低。因此必須對代碼進行優化,提高處理性能。X264代碼優化有以下3個層次:項目級優化、算法級優化和指令級優化:

(1)項目級優化 項目級優化主要是對CCS提供的各種編譯參數進行選擇、搭配、調整,如本文使用的選項-o3、-pm等;利用CCS編譯器提供的優化功能,改善循環及多重循環體性能,進行軟件流水,提高軟件的并行性;改寫不適合編譯器優化的語句,使CCS能夠對程序進行更好的優化。

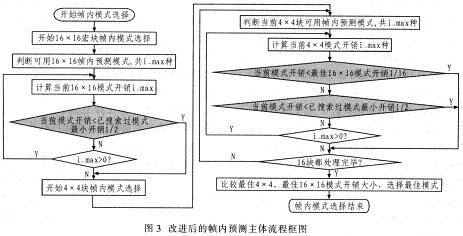

(2)算法級優化進行算法級優化時。應使VC環境下的純C版本與CCS下的版本同步更新,VC版本運行正確,既可以保證算法理論上的正確,又可以加快工作速度并減少問題的產生。該算法優化工作主要有以下幾點:①運動估算法的選擇:X264編碼器提供3種可選的整像素運動估算法:X264_ME_ESA(全搜索法)、X264_ME_HEX(六邊形搜索法)、X264_ME_DIA(小菱形搜索法)。在VC環境下使用純C版本代碼對同一視頻序列使用3種不同的搜索方法進行編碼。對比3種搜索方法在編碼速度、峰值信噪比(PSNR)、碼率方面的性能。對比之下X264_ME_ESA算法的峰值信噪比最高,X264_ME_HEX次之,X264_ME_DIA最低,但相互之間的質量差別并不大,碼率差別也很小,但編碼速度卻有明顯差距,X264_ME_DIA較前兩者在編碼速度上有明顯的優勢。經比較,選擇使用X264_ME_DIA運動估計算法。②幀內預測模式的改進:在X264的幀內預測流程中加入提前終止模式選擇的條件,改進算法的流程。進行16×16宏塊幀內模式搜索時,在當前模式的開銷小于已搜索過的模式的最小開銷的一半時,終止16×16幀內預測模式選擇,以當前模式為最佳16×16幀內預測模式。對4×4塊也加入相同的條件,并且若當前4×4塊幀內預測模式的預測開銷比相應的最佳16×16塊幀內預測模式的開銷的1/16還要小,則終止4×4塊的幀內預測模式選擇,以當前預測模式作為最佳4×4塊的幀內預測模式。改進后的幀內預測主體流程如圖3所示,灰色部分為加入的判定條件。

幀間預測模式的改進:將當前的16×16宏塊劃分為4個8×8宏塊,分別預測其運動矢量,然后以左右相鄰、上下相鄰的2個8×8塊的運動矢量的差值和閾值相比較為依據,判定是否進行16×8、8×16等分塊模式的預測,最后選擇開銷最小的劃分模式為最佳幀間劃分模式。

(3)指令級優化 DM6446一個時鐘周期內可并行運行8條指令,一次可存取64位數據,內部擁有64個32位通用寄存器,并且支持對寄存器中的4個8位字節或2個16位字節分別進行運算處理,這些使得DM6446具有很強的并行運算能力。視頻圖像的像素尺寸一般是4的倍數,X264中像素的值是用8位或16位數據按矩陣形式有規律的存儲,這種數據存儲結構與DM6446的并行處理方式很契合。因此對X264程序進行指令優化充分發揮DM6446的并行運算能力,是提高編碼器速度的關鍵。主要分為以下兩部分:①使用內聯函數優化;C6000編譯器提供了許多內聯函數intrinsics,它們是匯編指令映射的在線函數,不宜用C語言實現其功能的匯編指令都有對應的intrinsics函數。這樣就可在C語言結構中直接使用內聯函數實現對多個數據的并行運算操作。如:未使用內聯函數優化前X264程序調用一次雙線性內插函數只能計算一個亞像素點的值,而使用內聯函數_mem4()、_avgu4()等進行優化后,一次可以計算4個亞像素點的值,大大提高了運算速度。②使用線性匯編語言優化:由于線性匯編不需要考慮寄存器分配、指令延遲、并行指令安排等因素。因此可以利用CCS提供的profile分析工具將使用頻率高、耗時多的函數抽取出來,根據事先已知的數據間的相關性等信息,在程序中直接改寫函數匯編,人工優化。涉及的算法有:SAD、SSD的計算;DCT變換;反DCT變換、亞像素搜索等。

4 實驗結果

選取具有代表性的視頻序列carphone(人物運動幅度較大)、news(背景變化,人物運動幅度不大)、container(背景簡單,景物運動緩慢)進行編碼。視頻為YUV 4:2:0格式.QCIF,量化步長定為26,共50幀,采用IPPP…編碼模式。DM6446的時鐘頻率為600 MHz。表1為優化后峰值信噪比、消耗時鐘周期、碼率等實驗結果。表2為優化前后編碼時鐘周期對比,I幀編碼速度平均提高了9倍,P幀編碼速度平均提高了11倍。

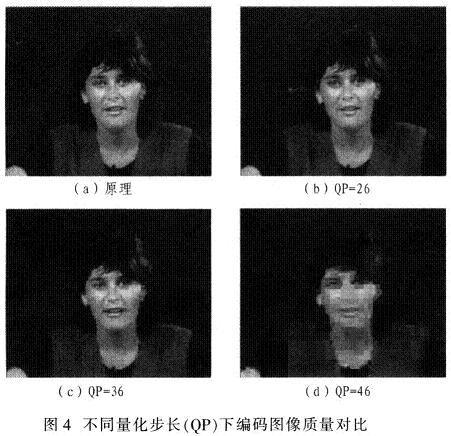

以視頻Miss-America為例,研究、對比移植優化后的編碼器在不同的量化步長值(QP)下,圖像的壓縮質量,如圖4所示。

5 結論

移植優化后的X264編碼器在CCS環境下可正確編碼,在量化步長值26下編碼圖像質量較高,優化后編碼速度較優化前有明顯提升。介紹的H.264視頻編碼系統的硬件設計,和X264編碼器針對DM6446平臺移植、優化的思路和方法,對構建高效的視頻應用平臺具有一定的參考價值。

電子發燒友App

電子發燒友App

評論