簡介

所有數模轉換器(DAC)都提供與數字設置增益和所施加基準電壓之積成比例的輸出。乘法DAC與固定基準電壓DAC不同,因為它可以將高分辨率數字設置增益應用施加到可變帶寬模擬信號上。本文將討論電阻梯乘法DAC及其對交流信號處理應用的適用性。

基本原理

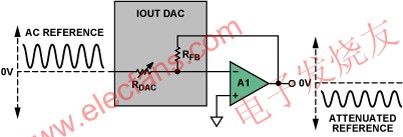

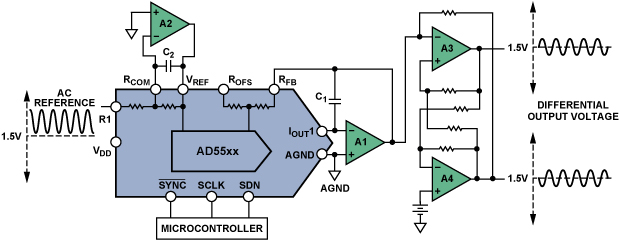

從1974年ADI公司推出世界首款(10 位)CMOS IC乘法DAC 以來,ADI公司就一直是乘法DAC設計與生產的領先者。它們采用一個具有適當帶寬的放大器,利用一個切換式R-2R梯和一個片內反饋電阻實現了調整交流增益或可變直流基準電壓輸入信號增益的簡單方法,從而用DAC取代了典型反相運算放大器級的輸入和反饋電阻(圖 1)。數字調整電阻梯和片內反饋電阻一起,提供與數字輸入成比例的增益(D/2n ),使RDAC起到了可變輸入電阻的作用。

![]()

圖 1. 反相增益配置

乘法DAC的市場發展迅速,歷經數代更新,產品的分辨率、精度和速度有了大幅提升,增加了各種數字存儲功能、串行通信選項,尺寸和成本大大降低并且每個芯片上還可以配置額外的DAC。最新一代的乘法DAC提供理想的構建模塊,用于控制可變直流或快速交流電壓信號的增益。

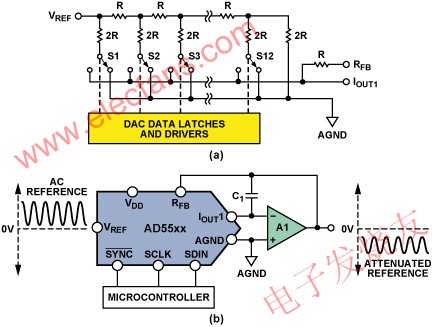

電阻(R-2R)梯用于運算放大器反饋電路,提供數字控制電流,電流經 RFB轉換成輸出電壓。放大器以低阻抗提供此輸出。基準電壓輸入具有恒定的對地電阻R。圖 2 顯示了該工作原理。圖 2a中,源電流VREF/R轉換成輸出電壓。放大器以低阻抗提供此輸出。基準電壓輸入具有恒定的對地電阻R。圖 2 顯示了該工作原理。圖 2a中,源電流IOUT1或導引至地(一般稱IOUT2)。同理,剩余電流的一半由開關S2 導引……如此類推。如果開關由一個數字字D(S1 是MSB)激活,則流經RFB (=R)的IOUT1端電流之和為 D × 2–n × VREF/R。此配置的重要優勢包括:可最大程度地降低瞬態,因為開關在地和虛地之間切換;RFB與梯形電阻片內匹配,具備出色的溫度跟蹤性能。

圖 2. a) R-2R梯原理;b) 乘法DAC,VOUT = 0 to ?VREF.

數字字D給出的數值范圍取決于所用的器件。ADI公司的部分AD545x/AD554x系列乘法DAC的D值范圍(第一象限)如下:歡迎轉載,本文來自電子發燒友網(http://www.xsypw.cn )

| 8位 AD5450 | 0 至 255 |

| 10位 AD5451 | 0 至 1,023 |

| 12位 AD5452 | 0 至 4,095 |

| 14位 AD5453 | 0 至 16,383 |

| 16位 AD5543 | 0 至 65,535 |

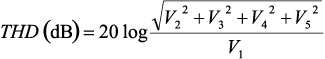

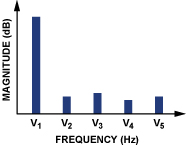

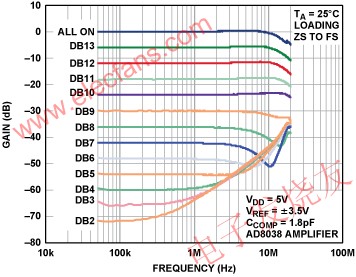

提高增益 圖 3. 提高乘法 DAC 的增益 正輸出 如果要求差分輸出,則需要兩個額外的運算放大器。Circuits from the Lab? CN-0143 查看完整的詳細信息。 圖 4. 乘法DAC, VOUT = 0 to VREF。AD5415、AD5405、AD5546/AD5556、AD5547/AD5557 內置此處所示的非專用電阻 圖 5. 單端-差分 穩定性問題 其中GBW是運算放大器的最小信號單位增益帶寬乘積,CO是 DAC的輸出電容。 信號調理的關鍵 M-DAC規格 圖 6. 乘法帶寬 模擬總諧波失真(THD):乘法波形信號中諧波成分的數學表達。它近似等于DAC輸出的前四個諧波(V2, V3, V4,和V5)之均方根和與基波值V1(如圖7所示)的對數比,計算公式如下: 圖 7. 諧波失真分量 乘法饋通誤差:DAC的數字輸入全部為0時,由基準電壓輸入至DAC輸出的容性饋通所致的誤差。理想情況下,一直到最低有效位DB0,每下降一位,增益便降低6 dB(圖 8)。不過,對于較低的位,容性饋通影響增益的頻率更高。這一點從較低位尾部上翹的平坦曲線可以看出。例如,14位DAC的DB2處,所有頻率的理想增益應為–72 dB,但由于饋通效應,1MHz時的實際增益為–66 dB。 圖 8. 乘法饋通誤差 選擇正確的運算放大器 對于基準電壓輸入為較高速信號的應用,需要一個帶寬較寬、壓擺率較高的運算放大器,以免削弱信號。一個運算放大器電路的增益-帶寬受反饋網絡的阻抗水平和增益配置限制。要確定所需的GBW,一種可行的方式是選擇–3 dB帶寬(10 倍于基準信號頻率)的運算放大器。 必須考慮運算放大器的壓擺率規格,以限制高頻大信號的失真。對于AD54xx和AD55xx系列,壓擺率為100 V/μs的運算放大器一般就夠了。 表 1 列出了可供乘法應用選擇的運算放大器。 表 1. 適用的 ADI 公司高速運算放大器 結論

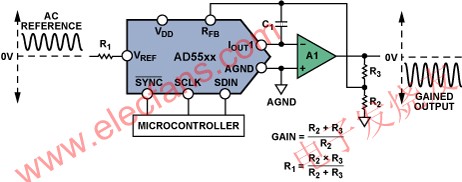

對于輸出電壓必須大于VIN的應用,可通過在DAC級后面增加外部放大器來提高增益;或者只需通過衰減反饋電壓在單級中實現,如圖 3 所示。所示近似值對R2||R3<

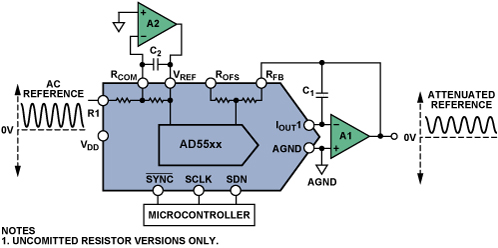

要產生正電壓輸出,可以使用一個外部反相運算放大器電路來另外反轉輸入或輸出。 一些乘法DAC內置非專用匹配電阻(具有跟蹤溫度系數),因此只需額外連接一個運算放大器(圖 4 中的 A2)即可獲得正輸出,這個額外的運算放大器可以是一個雙通道器件內的配套運算放大器。

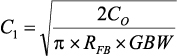

圖 2 和圖 3 中顯示的一個重要元件是補償電容(C1)。電阻梯的輸出電容加上放大器的輸入電容及任何雜散電容,會在開環響應中產生極點——這會在環路閉合時引起振鈴或不穩定。為了補償這一點,通常與DAC的內部RFB并聯連接一個外部反饋電容C1。如果C1值過小,會在輸出端產生過沖或振鈴,而值過大則會過分降低系統帶寬。DAC的內部輸出電容隨碼而變化,因此C1很難確定精確值。根據以下等式可計算出其最佳近似值:

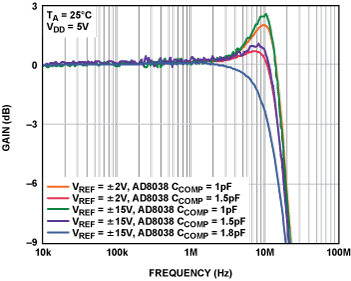

乘法帶寬:增益為–3 dB時的基準電壓輸入頻率。對于給定器件,它與幅度和選擇的補償電容呈函數關系。圖 6 所示為可以使最高12 MHz的信號相乘的電流輸出DAC AD5544、AD5554或AD545x的乘法帶寬坐標圖。配套的低功耗運算放大器 AD8038具備350 MHz帶寬, 可確保該運算放大器在此范圍內不會引起明顯的動態誤差。

乘法DAC電路性能非常依賴于所選運算放大器的能力,從而在電阻梯輸出端保持零電壓,并實現電流電壓轉換。要實現最佳的直流精度,重要的是要選擇具有低失調電壓和偏置電流的運算放大器,以保持誤差與DAC的分辨率相當。詳細的運算放大器技術規格參見器件數據手冊。

產品型號

(V)

(MHz)

(V/μs)

(μV)

(nA)封裝

AD8065

SOIC-8, SOT-23-5

AD8066

SOIC-8, MSOP-8

AD8021

SOIC-8, MSOP-8

AD8038

SOIC-8, SC70-5

ADA4899

LFCSP-8, SOIC-8

AD8057

SOT-23-5, SOIC-8

AD8058

SOIC-8, MSOP-8

AD8061

SOT-23-5, SOIC-8

AD8062

SOIC-8, MSOP-8

AD9631

SOIC-8, PDIP-8

自首款CMOS M-DAC問世以來的近40年間,相關器件不斷更新換代,許多新的功能特性層出不窮,性能持續提升,成本和尺寸則大幅縮減。我們的高分辨率、14位/16位電流輸出DAC產品系列AD55xx的最新性能改進包括:歡迎轉載,本文來自電子發燒友網(http://www.xsypw.cn )

相關推薦

高分辨率16位DS ADC LTC2439CGN-1

高分辨率、低漂移和精密稱重天平電子秤解決方案

高分辨率合成孔徑雷達圖像的直線特征多尺度提取方法

高分辨率捕獲單個脈沖

高分辨率模數轉換器的噪聲有什么影響?

高分辨率精密ADC的雜散產生原因是什么?

ADC信噪比要怎么分析?高速高分辨率ADC電路要怎么實現?

E1438C/D帶DSP存儲器提供了高分辨率的數字轉換

KAI-43140 CCD圖像傳感器提供高分辨率及圖像均勻性

LPC5528高分辨率ADC漏碼怎么解決?

LT1787高分辨率雙向電流至位轉換器

MSOX/DSOX 3000高分辨率模式

ZoomFFT算法基本原理及其應用介紹(雷達頻譜局部細化,提高分辨率)

【AD新聞】中國深圳先進院在高分辨率超聲成像領域取得重要進展

使用IEPE振動傳感器接口實現高分辨率轉換

單片機內置ADC實現高分辨率采樣的方法

單片機內置ADC實現高分辨率采樣的方法

增強高分辨率圖像捕獲的選擇

如何利用單片機內置ADC實現高分辨率采樣

如何利用單片機和LabVIEW設計出一種高分辨率的SoE系統?

如何在基于機器視覺的應用中通過單線傳輸高分辨率視頻數據

安裝程序不支持高分辨率顯示

康耐視兩款高分辨率Checker視覺傳感器

所謂“鷹眼”,即為高分辨率測量模式

投影機的最高分辨率的定義

用高分辨率示波器測量微小信號

示波器的垂直分辨率相關知識分享

請問24位的分辨率是否是所有ADC的極限?

請問哪幾個版本的Microsoft Visual Studio集成開發環境支持高分辨率?

請問如何應對高分辨率轉換器器件的噪聲挑戰?

請問怎樣根據文字和要顯示的字符設計一個較高分辨率的lcd?

調整攝像頭分辨率

采用高分辨率位置插值的Sin/Cos編碼器工業接口

非接觸式高分辨率磁性線性編碼器AS5311

鼎陽高分辨率數字示波器 SDS2000X HD系列 12-bit垂直分辨率 500 MHz

鼎陽高分辨率示波器

高分辨率示波器模擬帶寬2 GHz4通道

高分辨率示波器

超高分辨率圖像實時顯示系統設計

19

19一種高分辨率聚束SAR運動補償算法研究

13

13采用高分辨率乘法DAC處理交流信號

33

33凌華科技高分辨率動態信號采集模塊PCI-9527

3103

3103垂直分辨率與使用高分辨率示波器測量微小信號的介紹

22

22新型電阻梯乘法DAC應用于交流信號處理

3997

3997

高分辨率陣列感應測井儀的特點以及工作原理

2336

2336超高分辨率光譜儀的特點是什么

911

911

設計一個U形高分辨率網絡(U-HRNet)

1231

1231高管洞察:高分辨率音樂需要高分辨率揚聲器

41

41

電子發燒友App

電子發燒友App

評論