德州儀器 (TI) 宣布為其基于 KeyStone 的 TMS320C665x 多核數字信號處理器 (DSP) 推出兩款最新評估板 (EVM),進一步簡化高性能多核處理器的開發。

2012-07-31 09:20:20 1102

1102

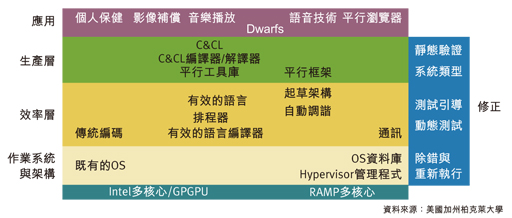

本文介紹了Enea針對多核DSP/SoC的平臺軟件解決方案。詳細介紹了方案的組成,包括面向針對多核DSP/SoC的OSEck操作系統、多核CPU的Enea Linux以及OSE操作系統、DSP陣列的管理模塊dSPEED、Enea系統級調試工具Optima以及Enea的分布式透明傳輸模塊LINX。

2013-06-14 13:50:28 2136

2136

對于多核DSP應用技術來說,BootLoad技術是一個關鍵點,也是應用難點之一。針對8核高性能DSP——TMS320C6678的根配置問題進行了研究,包括上電加載過程,單核和多核的emif

2014-03-26 11:14:32 9494

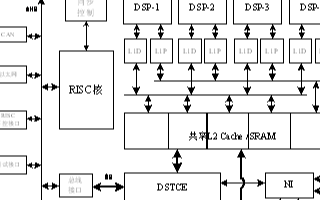

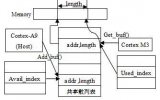

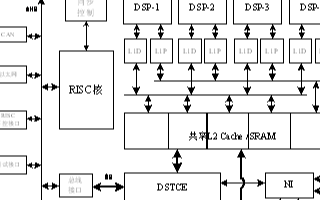

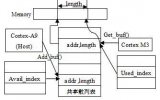

9494 多核數字信號處理器(DSP)是近年來針對高性能嵌入式應用而出現的一類多核微處理器(CMP)。相比傳統的單核處理器,多核處理器在提高并行處理能力的同時也需要更高的存儲帶寬和更靈活的存儲結構。便箋存儲器(SPM)是一種小容量的片上存儲器,具有全局地址空間,可以由訪存指令直接訪問。

2020-08-20 14:38:19 1311

1311

其實“多核”這個詞已經流行很多年了,世界上第一款商用的非嵌入式多核處理器是2002年IBM推出的POWER4。

2023-11-16 16:25:50 706

706

前言?嵌入式領域的處理器已向多核架構迅速發展,TI公司的KeyStone架構的TMS320C6678是目前市面上性能最高的多核DSP處理器。TMS320C6678集成8核C66x DSP處理器,每個

2021-01-14 17:31:12

在結構上存在差別,而且制作用的固體工藝也不盡相同。本文并不想對市場上可利用的全部DSP作詳盡比較,而更多集中在基本結構的一個重要區別及其對通信設計的影響。下面準備討論的基本結構是多核DSP與超核DSP。

2019-06-26 08:12:11

多核DSP關鍵技術有哪些?多核DSP的應用有哪些?主流多核DSP介紹

2021-04-21 06:10:10

多核處理器是最近快速發展的電子器件,單個芯片內集成了多個同構或者異構的處理器,使得其計算處理能力得到較大幅度的提高。DSP處理器由于其具有較高的數字處理能力,得到較廣泛的應用。多核DSP芯片以目前

2016-11-28 23:47:01

多核處理器是最近快速發展的電子器件,單個芯片內集成了多個同構或者異構的處理器,使得其計算處理能力得到較大幅度的提高。DSP處理器由于其具有較高的數字處理能力,得到較廣泛的應用。多核DSP芯片以目前

2016-10-15 22:43:53

的內部系統,應用處理器僅僅在一兩年時間內已從單核發展到雙核,甚至到目前的四核配置,目的是為了處理越來越多樣化和高性能的功能。一些最新的多核應用處理器系列也集成了額外的外設,如DRAM控制器及ARM

2018-09-25 14:28:58

多內核是指在一枚處理器中集成兩個或多個完整的計算引擎(內核),多核處理器是單枚芯片(也稱為“硅核”),能夠直接插入單一的處理器插槽中,但操作系統會利用所有相關的資源,將它的每個執行內核作為分立的邏輯

2019-06-20 06:47:01

采用多核技術提升 CPU 馬力,是一種通過硬件提供更高系統性能的日益常見的做法。即使對許多視成本和功耗為重要設計考慮的大量消費性應用,也是如此。但是,升級到多核系統并無法保證一定能夠提升性能或改善

2020-03-25 08:08:52

雖然光纖電纜在容量上一直優于微波,但許多通訊鏈路并不需要光纖的全部性能。隨著更低成本與可更快部署的微波技術在容量上不斷提升,微波在以往僅能 由光纖實現的應用領域變得更具優勢了。如今多核心射頻技術

2019-09-19 06:11:37

雖然光纖電纜在容量上一直優于微波,但許多通訊鏈路并不需要光纖的全部性能。隨著更低成本與可更快部署的微波技術在容量上不斷提升,微波在以往僅能由光纖實現的應用領域變得更具優勢了。如今多核心射頻技術的突破

2019-06-17 06:42:29

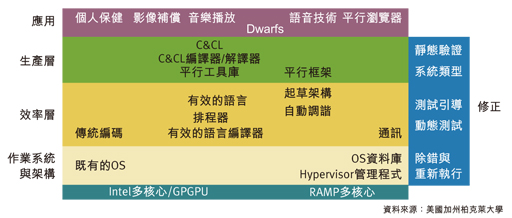

多核片上系統(SoC)架構的嵌入式DSP軟件設計Multicore a System-on-a-Chip (SoC) ArchitectureSoCs的軟件開發涉及到基于最強大的計算模型在各種處理

2021-12-14 08:18:07

本帖最后由 一只耳朵怪 于 2018-6-25 15:39 編輯

工程師們好!我現在對整個的單核能夠正常使用了,由于第一次接觸多核的DSP,對于架構,有很多的不理解。希望工程師們能給我指導指導

2018-06-25 01:50:10

請問, 目前處理器多采用多核的設計,在處理能力上肯定是有很大提升,但在能耗上是不是相對于同級的單核產品有年增加?

2018-06-21 08:58:27

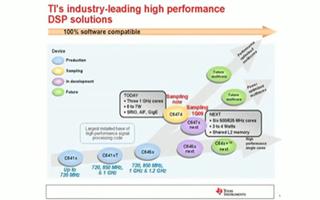

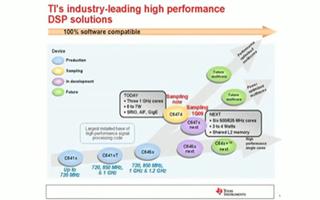

,頻率高達1.2GHz,而且總處理能力達到256GMAC,遠高于當前市面的DSP(見圖2)。該內核支持定點及浮點運算,其中的指令集完全與TI的TMS320C64x+ DSP指令集向下兼容。定點及浮點運作

2011-07-14 14:40:08

華為RNC設計文檔,有可靠性和EMC等設計章節,推薦一下。

2015-08-04 14:35:58

本節我們將運行第一個多核DSP程序,熟悉CCS開發環境,學會使用CCS調試工具,主要內容如下:(1)新建CCS項目(2)導入Target 仿真模塊(3)使用調試工具 一、新建CCS項目選擇File

2020-09-17 12:07:43

隨著信息技術和芯片技術的發展,DSP技術在航空、通信、醫療和消費類電子設備中得到廣泛應用。伴隨主頻不斷提升及多核并行工作,DSP芯片的運算能力快速增強。運用DSP芯片快速設計多類信號多路并行處理

2012-09-03 17:18:51

多核處理器是最近快速發展的電子器件,單個芯片內集成了多個同構或者異構的處理器,使得其計算處理能力得到較大幅度的提高。DSP處理器由于其具有較高的數字處理能力,得到較廣泛的應用。多核DSP芯片以目前

2021-02-02 07:53:47

如何提升CPU芯片處理事件能力?

2022-02-07 09:07:12

目標檢測的模型集成方法及實驗常見的提升模型能力的方式

2021-02-24 07:10:29

如何將DSP性能提升到極限?FPGA用做數字信號處理應用

2021-04-30 06:34:56

加速,非常必要。 多核并行如何讓仿真快起來 Linux工作站一般使用的是64bit通用的處理器。通用處理器處理的是通用的業務,在工作站上,我們會運行仿真,也會做綜合,會做布局&布線等各種

2023-03-28 11:18:49

基于TI KeyStone架構C6000系列TMS320C6678八核C66x定點/浮點高性能處理器設計的高端多核DSP評估板,由核心板與底板組成。核心板經過專業的PCB Layout和高低溫測試

2021-01-25 19:49:47

如何設計才能提升LED的驅動能力?

2021-04-09 06:57:08

使用,常見的是通用嵌入式處理器+DSP核。在目前嵌入式領域中,使用最為廣泛的為ARM 處理器,東大金智的ARM處理器可提供定制開發。目前,嵌入式多核處理器已經在嵌入式...

2021-12-14 07:47:01

程序設計方法已成為軟件人員急需掌握的主要技能之一。某宇航公司長期從事宇航電子設備的研制工作,隨著宇航裝備能力需求的提升,急需采用多核技術以增強設備的運算能力、降低功耗與體積,快速實現設備的升級與...

2021-12-14 07:05:02

SoC(系統單芯片)設計,而前段所述趨勢也使得嵌入式處理核心必須整合越來越多功能,扮演的角色也更加吃重,本文就將分析目前各類消費性電子產品中,需求的特殊運算功能有哪些?并進一步介紹如何以嵌入式微處理器取代其中最重要的 DSP功能以及如何彈性提升微處理器本身的 DSP效能。

2011-03-03 10:39:35

如題,本人在參與的一個項目,用到DSP TMS320C6472 六核處理器。準備使用其中兩個核來相關處理。每個核的代碼我已經寫好,但是本人是DSP新手,現在不知道怎么鏈接.out文件使其從Flash

2013-12-16 09:12:49

四、高性能計算驅動軟件設計師(多核DSP,含ARM+DSP) 1人 (51job網站搜索“航天晨信”)1.職位標簽:ARM+DSP 多核DSP 底層驅動 驅動軟件設計師 2.職位描述:工作內容:1

2014-05-08 14:07:29

多核方式。DSP正在開始重新采納多核架構,不過主要是針對那些處理任務可以得到妥善劃分的特殊應用。DSP應用通常只包含少量高度復雜的任務,系統性能的提升依賴于加快任務執行速度,而不是簡單地運行更多的任務

2009-04-09 23:14:41

有什么方法可以增強DSP協處理能力嗎?

2021-05-28 06:52:41

本帖最后由 冷酷の云 于 2016-1-12 10:20 編輯

有兩個項目,板級通訊軟件,DSP多核編程,有人能做嗎?

2015-12-16 11:05:32

本帖最后由 一只耳朵怪 于 2018-6-25 10:15 編輯

當dsp c6455 的PCI通過DMA收發數據時,DSP cpu的處理能力估計?

2018-06-25 06:59:40

多核DSP有幾種DMA,如EDMA3、IDMA、PKTDMA,看了EDMA3、PKTDMA,但還是感覺困惑,主要是這幾種DMA的功能有什么不同,分別面向什么應用場合?還有,如果是核間數據傳輸,是PKTDMA快還是EDMA3快?各自特點是什么?

2018-08-03 06:03:38

面向多核DSP的FSDP是如何設計并實現的?異構多核DSP總體結構快速共享數據緩沖池FSDP體系結構

2021-04-07 06:07:07

SRNS Relocation就是將某個UE的SRNC的角色由一個RNC轉到另外一個RNC的過程.SRNS Relocation前,該UE的SRNC (Serving RNC) 叫SourceRNC,即將承擔SRNC角色的目標RNC叫Target RNC.Source RNC和Target R

2009-06-06 17:00:59 6

6 插值和抽取濾波器被廣泛應用于現代通信系統中,然而基于傳統DSP 或者FPGA 的濾波器,具有數據率低和占用資源多的缺點。為了克服這些缺點,本文針對一種多核DSP 處理器, 提出

2009-11-27 15:26:57 9

9 描述 為了滿足高級音頻應用對更高內存和性能的需求,恩智浦設計了支持多種高清(HD)音頻標準的數字信號處理(DSP)芯片。Symphony音頻DSP56721是恩智浦多核24位處理器系列

2023-12-07 16:59:52

RNC的容量、處理能力和最大端口配置數量

華為RNC可支持51200個等效語音信道,支持100萬等效語音用戶。華為RNC處理能力達到2400K(BHCA)

2009-06-30 09:43:25 1603

1603 專家觀點:并行軟件須加速追趕多核處理器發展腳步

為了持續提升性能而又不至于因過熱導致故障,微處理器正朝向多核心方向發展。但主流軟件至今卻尚未能找到使

2009-08-07 07:40:31 334

334

TI推出多核片上系統架構 實現5倍性能提升

日前,德州儀器 (TI) 宣布推出一款基于 TI 多核數字信號處理器 (DSP) 的新型片上系統 (SoC) 架構,該架構在業界性能最高的 CPU

2010-02-24 09:41:14 863

863 TI推出最新多核SoC架構,實現5倍性能提升

日前,德州儀器(TI)宣布推出一款基于 TI 多核數字信號處理器(DSP)的新型片上系統(SoC)架構,該架構在業界性能最高的CPU中同時

2010-02-26 08:38:16 562

562 Octasic Inc發布了針對基站 PHY 和 MAC 的業界最高效的多核 DSP 產品。

OCT2224W 是Octasic 公司最新推出的多核DSP 產品解決方案系列的一部分OCT2224W 的功耗效率較目前市場上其它 DSP

2010-07-02 08:55:42 1477

1477 認識多核基本架構

多核處理器在同一個芯片中植入了多個處理器引擎,這就可以提供更高的CPU性能、功能特性和分區能力。一般說來,多核有兩種實現形式。

2010-08-26 18:08:00 1242

1242 多核處理器以其高性能、低功耗、設計周期短等諸多優勢成為未來高性能處理器的發展趨勢。由于應用對計算能力的需求是無限的,隨著芯片上晶體管數目的進一步增多,多核處理器將

2011-05-30 10:06:35 52

52 針對 多核處理器 計算能力和訪存速度間差異不斷增大對多核系統性能提升的制約問題,分析幾款典型多核處理器存儲系統的設計特點,探討多核處理器片上存儲系統發展的關鍵技術,

2011-07-27 15:49:57 29

29 隨著新一代數字信號處理器 (DSP) 的推出,特別是多核 DSP 的推出,開發人員將擁有高性能、低成本的低功耗備選方案,實現檢查應用的實時影像處理實施。

2012-08-08 17:08:00 639

639

關于面向SD的R應用的多核DSP低功耗設計

2016-05-19 13:41:19 3

3 基于SystemC構建多核DSP軟件仿真平臺_韋祎

2017-01-03 17:41:32 3

3 多核處理器中的超越函數協處理器設計_黃小康

2017-01-07 18:39:17 2

2 一種基于DSP的多核SOC中斷擴展設計與實現_張躍玲

2017-01-07 21:08:03 0

0 一種基于分組的多核嵌入式實時調度算法_康鵬

2017-01-07 21:39:44 0

0 繼GPU部分跑分曝光之后,高通驍龍835處理器的CPU跑分在網上流出,從成績來看,其單核跑分提升不明顯,但由于采用了八核設計,其多核成績提升較大。

2017-02-07 15:35:17 2006

2006 多核處理器基礎,介紹了嵌入式的多核的信息

2017-04-11 14:17:49 2

2 多核處理器是最近快速發展的電子器件,單個芯片內集成了多個同構或者異構的處理器,使得其計算處理能力得到較大幅度的提高。DSP 處理器由于其具有較高的數字處理能力,得到較廣泛的應用。多;核DSP芯片

2017-10-18 14:28:11 13

13 基于面向SDR應用的多核DSP低功耗設計

2017-10-19 10:40:38 3

3 ,迫使DSP廠商開始在單一矽片上集成更多的處理器內核。本文分析了多核DSP必須面臨的挑戰,介紹了一些常見的多核DSP產品。 數字信號處理器(DSP)是對數字信號進行高速實時處理的專用處理器。在當今的數字化的背景下,DSP以其高性能和軟件

2017-10-19 16:26:49 0

0 基于Costar_的異構多核DSP設計與實現

2017-10-20 08:27:46 12

12 基礎局端設備OEM廠商關注的焦點正在轉變,對解決方案的功耗要求越來越高、要求可擴展的異構網絡、對MIMO功能的需求以提升接受信號接受能力。對頻譜效率的要求使得低時延、密集計算型處理環境越來越重要

2017-10-24 11:41:32 2

2 為了滿足4G-LTE基站的需求,DSP制造商在其處理器中提供了更強大的處理能力和更大的吞吐量。這些多核處理器許多以GHz的速度運行并使用加速器來提高吞吐量。雖然這些新特性通過支持更多的通道提高了基站

2017-10-24 17:00:26 0

0 業界領先的TEMPO評估服務 高分段能力,高性能貼片保險絲 專為OEM設計師和工程師而設計的產品 Samtec連接器 完整的信號來源 每天新產品 時刻新體驗 完整的15A開關模式電源 DSP是對數

2017-10-25 14:21:36 0

0 ,已是業界共識。TI認為,通過改進無線網絡控制器(RNC)的分組處理功能,是滿足無線網絡數據及語音流量大幅增長以及應用多樣性需求的可行之道。 基站控制器(RNC)直接影響到移動用戶的通話和使用效果,為此,TI 采用多核DSP替代以

2017-11-03 10:25:25 0

0 多核DSP也許對大多數人而言并不是個陌生的概念,早在幾年前,為了提升性能、降低功耗,在處理器中增加內核已經成為計算和嵌入式處理器產業的標準作法。 然而,正當多內核技術在處理器領域發展得紅紅火火之時

2017-11-03 11:24:07 3

3 隨著無人機(UAV)、聲納、雷達、信號情報(SIGINT)以及軟件定義無線電(SDR) 等波形密集型應用中的信號處理需求不斷攀升,多個數字信號處理器(DSP)內核的使用已成為重要的實現手段。多核功能

2017-12-04 18:17:37 4

4 隨著1080P高清視頻以及4K超高清晰視頻的普及和應用,基于傳統單核DSP處理器的視頻信息處理已有些力不從心。為此TI公司推出了一款專門用于高清視頻處理的多核DSP處理器,它擁有4個不同類型的處理

2018-01-22 07:01:01 1929

1929

發展的趨勢。目前普遍高清視頻編解碼都采用異構多核處理器內的DSP進行協同處理,通過片上通信機制實現核間多媒體數據傳輸。DSP相比軟解碼在速度和性能上得到了一定的提升,如DaVinci平臺內置DSP能夠實現720P視頻實時解碼。但DSP運行

2018-07-03 10:15:00 1511

1511

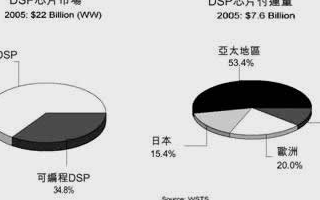

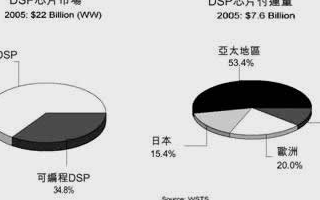

隨著語音、視頻和數據“三合一”服務成為業界潮流,下一代有線和無線基礎設施對DSP的處理能力要求越來越高。為了滿足大量并行處理能力需求,通常的做法是增加DSP數量和提高DSP頻率,同時輔以ASIC和FPGA。

2018-02-08 14:09:54 1422

1422

醫療保健正在迅速變化,基于多核DSP的成像系統有效地補充了當今的趨勢。

2018-04-16 14:39:52 10

10 Virtex-7 485T DSP處理能力

2018-06-05 02:45:00 3242

3242 探討現今TI 在高性能 DSP,多核及適應于未來發展趨勢的下一代處理器領域的研究和探索。

2018-06-13 01:13:00 3692

3692 探討現今TI 在高性能 DSP,多核及適應于未來發展趨勢的下一代處理器領域的研究和探索。

2018-06-12 01:52:00 3411

3411

“魂芯二號”是中國電科 38 所在“魂芯一號”單核 DSP 基礎上研制的首款高性能多核 DSP 產品。“魂芯二號”集成 2 個新一代處理器內核 eC104+,該內核在“魂芯一號”使用的 eC104

2020-05-15 08:00:00 12

12 德州儀器 (TI) 推出的面向開發人員的業界最高性能的高靈活型可擴展多核解決方案,其建立在 TMS320C66x 數字信號處理器 (DSP) 產品系列基礎之上,是工業自動化市場處理密集型應用的理想

2021-02-20 10:40:00 3342

3342 ,迫使DSP廠商開始在單一矽片上集成更多的處理器內核。本文分析了多核DSP必須面臨的挑戰,介紹了一些常見的多核DSP產品。

2020-08-19 15:08:42 2193

2193

多核處理器以其高性能、低功耗優勢正逐步取代傳統的單處理器成為市場的主流。隨著應用需求的擴大和技術的不斷進步,多核必將展示出其強大的性能優勢。但目前多核處理器技術還面臨著諸多挑戰,本文主要介紹了多核處理器發展的關鍵技術并對多核處理器技術的發展趨勢進行簡要分析。

2021-03-29 10:47:31 8

8 多核處理器越來越多地被采用在關鍵系統領域,特別是在關鍵任務的軍事環境中。它們為單核處理器的長期可用性問題以及促進軍事系統創新所需的處理能力增加的問題提供了解決方案。由于多核處理器既不提供確定性環境,也不提供可預測的軟件執行時間,因此需要一種新的驗證方法(一種解決多核時序分析挑戰的方法)來安全使用。

2022-11-09 15:19:37 573

573 CPU核數的增多給處理器的設計帶來了很多新的挑戰,包括我在前面文章中介紹的cache一致性,內存一致性等,既然多核的引入使系統變得如此復雜,那為什么我們還需要發展多核處理器,并且核數還越來越龐大,而不是專注于提升單核的計算能力?

2022-12-05 15:12:22 592

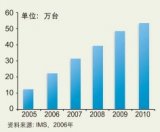

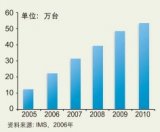

592 DSP是對數字信號進行高速實時處理的專用處理器。在當今的數字化的背景下,DSP以其高性能和軟件可編程等特點,已經成為電子工業領域增長最迅速的產品之一,人們對其性能、功耗和成本也提出了越來越高的要求,迫使DSP廠商開始在單一矽片上集成更多的處理器內核。本文分析了多核

2023-10-31 17:06:25 338

338 DSP是對數字信號進行高速實時處理的專用處理器。在當今的數字化的背景下,DSP以其高性能和軟件可編程等特點,已經成為電子工業領域增長最迅速的產品之一,人們對其性能、功耗和成本也提出了越來越高的要求,迫使DSP廠商開始在單一矽片上集成更多的處理器內核。本文分析了多核

2023-10-31 17:04:08 282

282 導讀創龍科技TL665xF-EasyEVM評估板是一款基于TIKeyStone架構C6000系列TMS320C665x多核C66x定點/浮點DSP以及XilinxArtix-7FPGA處理

2021-12-28 11:54:17 6

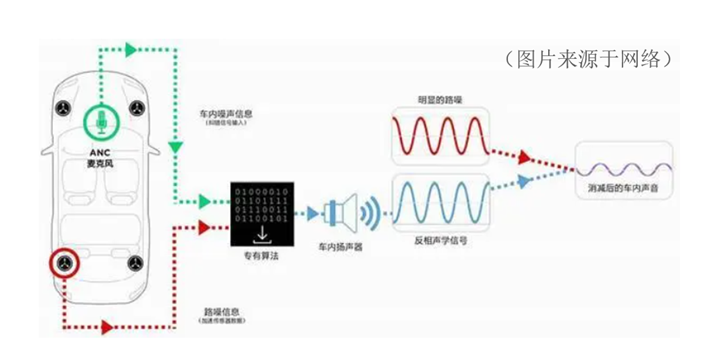

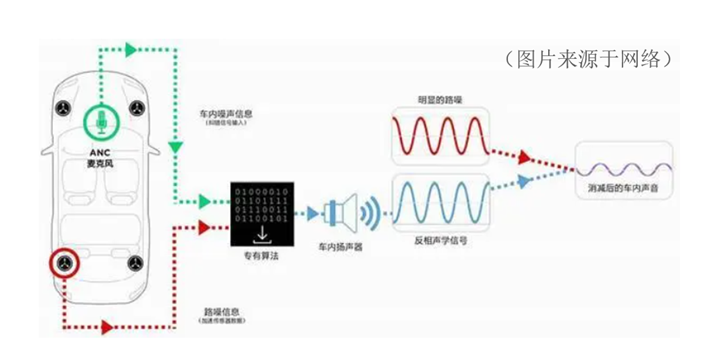

6 本文主要內容:RNC路噪主動降噪概述、RNC路噪主動降噪測試配置、RNC路噪主動降噪測試架構

2024-01-10 14:20:14 285

285

電子發燒友App

電子發燒友App

評論