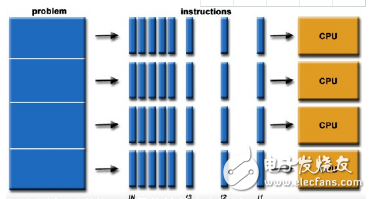

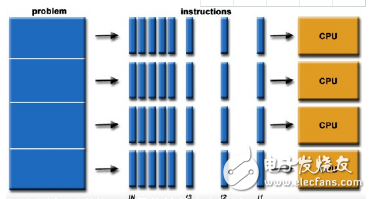

本文探究的嵌入式多核處理器采用同構(gòu)結(jié)構(gòu),實(shí)現(xiàn)同一段代碼在不同處理器上的并行執(zhí)行。##緩存優(yōu)化(Cache friendly)的目標(biāo)是減少數(shù)據(jù)在內(nèi)存和緩存之間的拷貝。

2014-12-16 14:43:44 1377

1377 常常在嵌入式領(lǐng)域使用,常見(jiàn)的是通用嵌入式處理器+DSP核。本文探究的嵌入式多核處理器采用同構(gòu)結(jié)構(gòu),實(shí)現(xiàn)同一段代碼在不同處理器上的并行執(zhí)行。

2018-10-17 07:55:00 3708

3708 介紹一款可編程語(yǔ)音處理器的設(shè)計(jì)與應(yīng)用

2021-06-03 07:16:50

本文介紹一種面向基站平臺(tái)處理單板的基于融合SoC處理器的平臺(tái)軟件解決方案。

2021-05-17 06:36:12

本文提出了一種基于FPGA的適合大規(guī)模數(shù)字信號(hào)處理的并行處理結(jié)構(gòu)。

2021-04-30 07:16:52

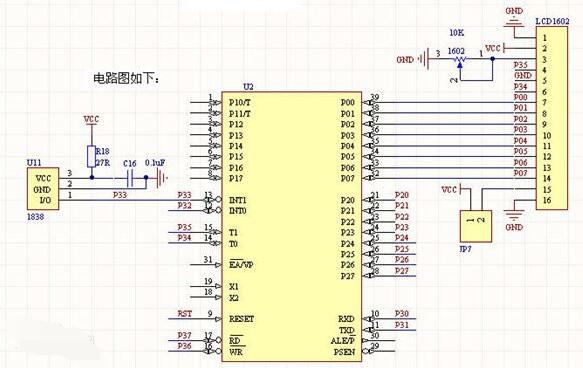

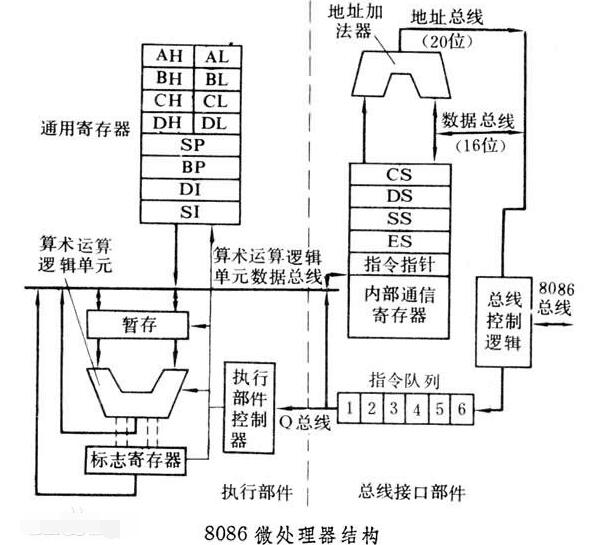

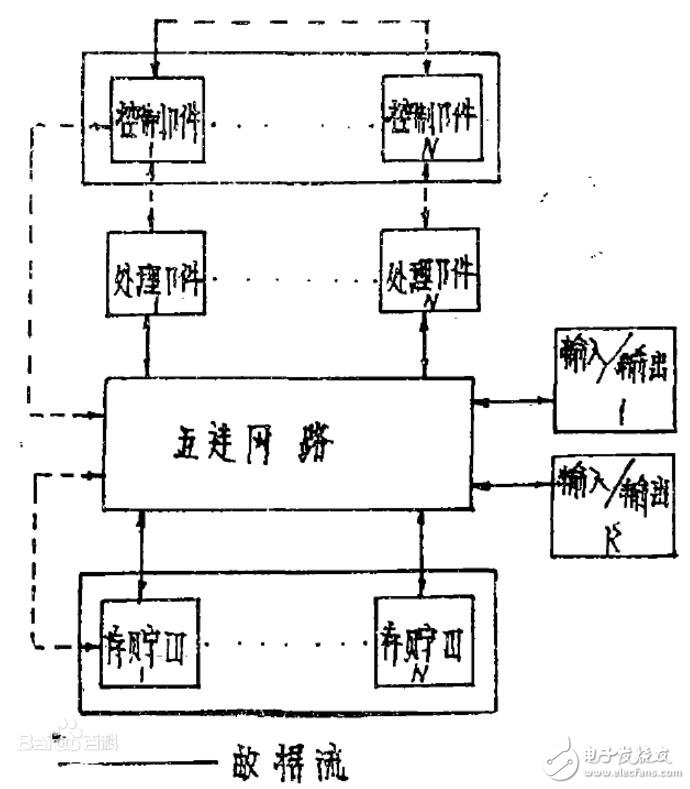

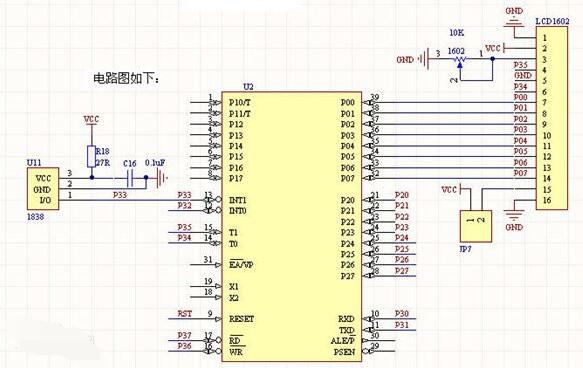

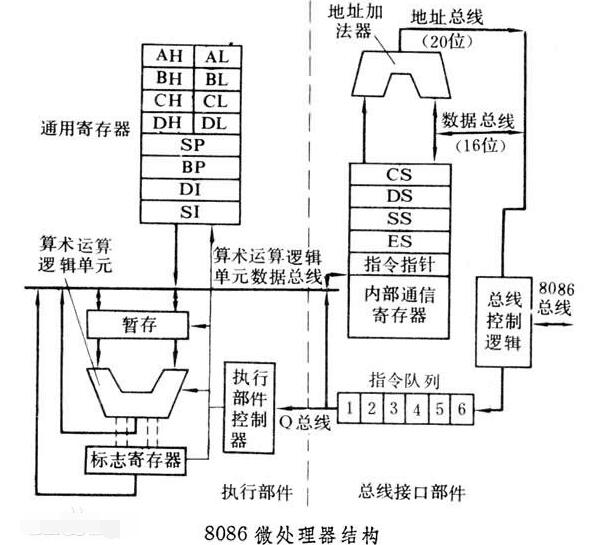

嵌入式微處理器體系結(jié)構(gòu)馮諾依曼結(jié)構(gòu):程序和數(shù)據(jù)共用一個(gè)存儲(chǔ)空間,程序指令存儲(chǔ)地址和數(shù)據(jù)存儲(chǔ)地址指向同一個(gè)存儲(chǔ)器的不同物理位置,采用單一的地址及數(shù)據(jù)總線,程序和數(shù)據(jù)的寬度相同。例如:8086、ARM7

2021-12-17 06:04:03

_處理器基本知識(shí)介紹 處理器基本知識(shí)處理器:超大規(guī)模集成電路,就是模電里說(shuō)的集成電路,不同的是它所要做的就是處理機(jī)器碼,對(duì)應(yīng)機(jī)器碼的不同做出不同的處理。比較出名的處理器廠商有inter ,AMD

2018-01-15 16:05:57

本帖最后由 fantek 于 2013-10-1 22:31 編輯

在一個(gè)主程序中使用兩個(gè)事件結(jié)構(gòu)及事件內(nèi)循環(huán)實(shí)現(xiàn)并行處理。

2013-09-16 22:04:32

ARM9系列處理器是英國(guó)ARM公司設(shè)計(jì)的主流嵌入式處理器,主要包括ARM9TDMI和ARM9E-S等系列。本文主要介紹它們與ARM7TDMI的結(jié)構(gòu)以及性能比較。

2019-10-09 07:30:25

ARM公司開發(fā)了很多系列的ARM處理器核,目前最新的系列已經(jīng)是ARM11了,而ARM6核及更早的系列已經(jīng)很罕見(jiàn)了,ARM7以后的核也不是都獲得廣泛應(yīng)用。目前,應(yīng)用比較多的是ARM7系列、ARM9系列

2019-07-23 07:08:18

RISC的概念對(duì)ARM處理器的設(shè)計(jì)有著重大的影響,最成功也是第一個(gè)商業(yè)化的RISC實(shí)例就是ARM,因此大家公認(rèn)RISC就是ARM的別名,而且ARM是當(dāng)前使用最廣、最為成功的基于RISC的處理器

2022-04-24 09:57:10

RISC的優(yōu)點(diǎn)Patterrson和Ditzel認(rèn)為處理器的設(shè)計(jì)有3個(gè)基本優(yōu)點(diǎn):基于RISC體系結(jié)構(gòu)設(shè)計(jì)的處理器管芯面積小。處理器的簡(jiǎn)單使得需要的晶體管減少和實(shí)現(xiàn)的硅片面積減小,剩下更大面積可集成

2022-04-24 10:02:29

ARM產(chǎn)品必須如何運(yùn)行的體系結(jié)構(gòu)規(guī)范。

此外,一些合作伙伴還授權(quán)實(shí)施符合架構(gòu)規(guī)范的自己的ARM處理器。

這導(dǎo)致了分層劃分為三個(gè)級(jí)別的規(guī)范,這些規(guī)范共同描述了整個(gè)SoC的行為和程序員模型

2023-08-21 07:28:01

在這里,我提供了3篇相當(dāng)于掃盲的文章,帶大家了解下ARM的歷史、概念、和體系結(jié)構(gòu):一文看懂ARM公司淺談ARM處理器架構(gòu)我對(duì)ARM結(jié)構(gòu)的理解簡(jiǎn)單介紹ARM的指令集

2020-09-21 15:57:35

數(shù)據(jù)處理指令尋址方式和內(nèi)存訪問(wèn)指令尋址方式。本章主要介紹ARM匯編語(yǔ)言。主要內(nèi)容如下:ARM處理器的尋址方式。ARM處理器的指令集。ARM處理器尋址方式ARM指令的尋址方式分為數(shù)據(jù)處理指令尋址方式和內(nèi)存訪問(wèn)指令尋址方式。數(shù)據(jù)處理指令尋址方式數(shù)據(jù)處理指令的基本語(yǔ)法格式如下: {} {S} ,,

2022-04-26 10:30:57

STM32單片機(jī)STM32的核心Cortex-M3處理器是一個(gè)標(biāo)準(zhǔn)化的微控制器結(jié)構(gòu),希望思考一下,何為標(biāo)準(zhǔn)化?簡(jiǎn)言之,Cortex-M3處理器擁有32位CPU,并行總線結(jié)構(gòu),嵌套中斷向量

2021-07-16 06:33:15

DSP并行處理的方法摘 要:TI公司的TMS320C6x和AD公司的ADSP2106x是目前業(yè)界使用廣泛的數(shù)字信號(hào)處理器(DSP)。

2009-11-03 15:16:47

ADSP2106x的Link口組成多DSP互連并行系統(tǒng) 首先對(duì)ADSP2106x做一簡(jiǎn)單介紹。ADSP2106x是一種高性能的32 b數(shù)字信號(hào)處理器,采用超級(jí)哈佛結(jié)構(gòu)。內(nèi)有3條片內(nèi)總線,他們是PM總線(程序存貯器

2019-04-08 09:36:19

FPGA實(shí)現(xiàn)高速FFT處理器的設(shè)計(jì)介紹了采用Xilinx公司的Virtex - II系列FPGA設(shè)計(jì)高速FFT處理器的實(shí)現(xiàn)方法及技巧。充分利用Virtex - II芯片的硬件資源,減少?gòu)?fù)雜邏輯,采用

2012-08-12 11:49:01

Freescale處理器家族之i.MX

2021-03-04 06:58:04

本帖最后由 yongwoozzang 于 2015-4-7 02:34 編輯

Scan:1.嵌入式系統(tǒng)的概念2.嵌入式系統(tǒng)的組成部分(處理器,io,操作系統(tǒng)等)3.嵌入式微處理器體系結(jié)構(gòu)(馮諾

2015-04-07 02:32:27

STM32的核心Cortex-M3 處理器是一個(gè)標(biāo)準(zhǔn)化的微控制器結(jié)構(gòu),希望思考一下,何為標(biāo)準(zhǔn)化?簡(jiǎn)言之,Cortex-M3 處理器擁有32 位CPU,并行總線結(jié)構(gòu),嵌套中斷向量控制單元,調(diào)試系統(tǒng)以及

2021-07-23 08:35:05

arm為什么是32位微處理器呢?所以ARM體系結(jié)構(gòu)所支持的最大尋址空間為4GB嘍?

2023-03-15 10:27:53

本指南介紹了在調(diào)試Armv8-A處理器之前了解的有用概念。

為了說(shuō)明這些概念,我們提到了調(diào)試器,例如GDB,GNU項(xiàng)目調(diào)試器

以及Arm Debugger,它是Arm Development

2023-08-02 06:40:30

概述盡管多核處理器比單核處理器提供更強(qiáng)大的處理能力,當(dāng)時(shí)多核處理器存在難以檢測(cè)和并發(fā)相關(guān)的錯(cuò)誤。本文介紹了一種對(duì)多核處理器架構(gòu)上程序時(shí)間測(cè)量的全新技術(shù),這種技術(shù)通過(guò)在目標(biāo)系統(tǒng)上運(yùn)行,實(shí)現(xiàn)覆蓋率的實(shí)時(shí)

2021-12-14 07:07:22

一種高速并行FFT處理器的VLSI結(jié)構(gòu)設(shè)計(jì)摘要:在OFDM系統(tǒng)的實(shí)現(xiàn)中,高速FFT處理器是關(guān)鍵。在分析了基4按時(shí)域抽取快速傅立葉變換(FFT)算法特別的基礎(chǔ)上,研究了一種高性能的FFT處理器的硬件

2008-10-15 22:41:48

1.主要學(xué)習(xí)嵌入式系統(tǒng)概述了解微處理器的基本操作。理解微處理器體系結(jié)構(gòu)的基本概念。機(jī)器語(yǔ)言程序的基礎(chǔ)知識(shí)。用匯編語(yǔ)言設(shè)計(jì)和編寫程序2.嵌入式系統(tǒng)包括軟件和硬件 硬件部分需要微處理器和微控制器還有其他

2021-12-17 07:50:05

ARM 處理器是一種低功耗高性能的 32 位 RISC(精簡(jiǎn)指令系統(tǒng))處理器。從結(jié)構(gòu) 入手對(duì)其進(jìn)行分析,并針對(duì)目前流行的 ARM920T 核詳細(xì)描述其硬件結(jié)構(gòu)和編程。ARM 處理器共有 31 個(gè)

2019-09-24 17:47:38

先理清楚一些概念,然后我們?cè)僬f(shuō)下區(qū)別。什么是處理器?常常說(shuō)的處理器,指的是CPU,擅長(zhǎng)做計(jì)算,一般主頻用Ghz來(lái)計(jì)算,因?yàn)轭l率很高,適合跑系統(tǒng),比如Linux。市面上常用的處理器有Intel AMD

2021-11-24 07:05:38

本文以Intel IXF2400網(wǎng)絡(luò)處理器為例,討論了網(wǎng)絡(luò)處理器硬件結(jié)構(gòu)和軟件開發(fā)技術(shù),并在此基礎(chǔ)上提出了一種基于網(wǎng)絡(luò)處理器的路由器體系結(jié)構(gòu)和軟件開發(fā)流程。

2021-05-27 07:07:53

單片機(jī)處理器的結(jié)構(gòu)體系有哪幾種呢?單片機(jī)程序是如何運(yùn)行起來(lái)的?

2022-01-24 06:04:41

傳統(tǒng)數(shù)字濾波器硬件的實(shí)現(xiàn)主要采用專用集成電路(ASIC)和數(shù)字信號(hào)處理器(DSP)來(lái)實(shí)現(xiàn)。FPGA內(nèi)部的功能塊中采用了SRAM的查找表(lo-ok up table,LUT)結(jié)構(gòu),這種結(jié)構(gòu)特別適用于并行處理結(jié)構(gòu),相對(duì)于傳統(tǒng)方法來(lái)說(shuō),其并行度和擴(kuò)展性都很好,它逐漸成為構(gòu)造可編程高性能算法結(jié)構(gòu)的新選擇。

2019-10-22 07:14:04

本文提出了一種基于TMS320C6701信號(hào)處理器的高性能信號(hào)處理模塊的設(shè)計(jì)方案,設(shè)計(jì)了具有一定通用性的并行信號(hào)處理模塊,該模塊具有高速互連接口,可以根據(jù)應(yīng)用系統(tǒng)的需求構(gòu)成不同的并行系統(tǒng),完成各種信號(hào)處理任務(wù)。

2021-04-02 07:30:14

處理器。通過(guò)在兩個(gè)執(zhí)行內(nèi)核之間劃分任務(wù),多核處理器可在特定的時(shí)鐘周期內(nèi)執(zhí)行更多任務(wù)。 多核技術(shù)能夠使服務(wù)器并行處理任務(wù),多核系統(tǒng)更易于擴(kuò)充,并且能夠在更纖巧的外形中融入更強(qiáng)大的處理性能,這種外形所用

2019-06-20 06:47:01

機(jī))節(jié)點(diǎn)集成到同一芯片內(nèi),各個(gè)處理器并行執(zhí)行不同的線程或進(jìn)程。在基于SMP結(jié)構(gòu)的單芯片多處理機(jī)中,處理器之間通過(guò)片外Cache或者是片外的共享存儲(chǔ)器來(lái)進(jìn)行通信。而基于DSM結(jié)構(gòu)的單芯片多處理器中,處理器間

2011-04-13 09:48:17

本文以4G無(wú)線通信這一學(xué)術(shù)熱點(diǎn)為研究對(duì)象,結(jié)合4G無(wú)線通信協(xié)議和高清視頻中所使用的算法,研究和設(shè)計(jì)了基于SDR的變寬度SIMD處理器體系結(jié)構(gòu),包括處理器的工作模式、PE核標(biāo)量流水線。仿真結(jié)果驗(yàn)證了該處理器體系結(jié)構(gòu)設(shè)計(jì)的正確性。

2021-05-20 06:18:53

如何實(shí)現(xiàn)在Linux操作系統(tǒng)下ARM體系結(jié)構(gòu)的處理器與DSP的數(shù)據(jù)通信?

2021-05-28 06:11:36

本文設(shè)計(jì)的FFT處理器,基于FPGA技術(shù),由于采用移位寄存器流水線結(jié)構(gòu),實(shí)現(xiàn)了兩路數(shù)據(jù)的同時(shí)輸入,相比傳統(tǒng)的級(jí)聯(lián)結(jié)構(gòu),提高了蝶形運(yùn)算單元的運(yùn)算效率,減小了輸出延時(shí),降低了芯片資源的使用。

2021-04-28 06:32:30

,也可支持其他片上協(xié)處理器。ARM體系結(jié)構(gòu)支持通過(guò)增加協(xié)處理器來(lái)擴(kuò)展指令集的機(jī)制。1. 協(xié)處理器的體系結(jié)構(gòu)協(xié)處理器的體系結(jié)構(gòu)最重要的特征如下:支持多達(dá)16個(gè)邏輯協(xié)處理器每個(gè)協(xié)處理器可使用的專用寄存器多達(dá)

2022-04-24 09:36:47

嵌入式多核處理器結(jié)構(gòu)OpenMP并行化優(yōu)化

2021-03-02 06:59:00

包括同構(gòu)(Symmetric)和異構(gòu)(Asymmetric)兩種。同構(gòu)是指內(nèi)部核的結(jié)構(gòu)是相同的,這種結(jié)構(gòu)目前廣泛應(yīng)用在PC多核處理器;而異構(gòu)是指內(nèi)部核的結(jié)構(gòu)是不同的,這種結(jié)構(gòu)常常在嵌入式領(lǐng)域

2021-12-14 07:47:01

文中介紹了MOTOROLA公司的嵌入式微處理器MCF5249的原理、特點(diǎn)和引腳功能,說(shuō)明了基于該處理器和嵌入式操作系統(tǒng)UCLINUX的網(wǎng)絡(luò)相機(jī)結(jié)構(gòu),給出了用MCF5249進(jìn)行網(wǎng)絡(luò)相機(jī)設(shè)計(jì)時(shí)的資源分配情況及電路設(shè)計(jì)注意事項(xiàng)。

2019-09-05 06:02:00

目錄一、嵌入式微處理器體系結(jié)構(gòu)1、馮諾依曼體系結(jié)構(gòu)2、哈弗體系結(jié)構(gòu)二、嵌入式系統(tǒng)的硬件結(jié)構(gòu)1、嵌入式微控制器MCU(CPU+片內(nèi)內(nèi)存+片內(nèi)外設(shè))2、嵌入式微處理器MPU(CPU)3、嵌入式數(shù)字信號(hào)

2021-11-08 06:57:02

`嵌入式微處理器和接口詳技術(shù)詳解 本文小編為學(xué)員介紹嵌入式微處理器和接口的相關(guān)技術(shù)概念。關(guān)于嵌入式系統(tǒng)的微處理器與接口,主要應(yīng)當(dāng)熟悉下列相關(guān)的知識(shí)點(diǎn)。 嵌入式微處理器和接口詳技術(shù)詳解: 1

2017-10-30 14:33:10

本文創(chuàng)客學(xué)院嵌入式培訓(xùn)講師為學(xué)員介紹嵌入式微處理器和接口的相關(guān)技術(shù)概念。關(guān)于嵌入式系統(tǒng)的微處理器與接口,主要應(yīng)當(dāng)熟悉下列相關(guān)的知識(shí)點(diǎn)。 嵌入式微處理器和接口詳技術(shù)詳解: 1、嵌入式微處理器

2017-06-28 13:55:53

文章目錄嵌入式系統(tǒng)概述基本概念嵌入式系統(tǒng)的發(fā)展發(fā)展歷史發(fā)展趨勢(shì)組成結(jié)構(gòu)設(shè)備驅(qū)動(dòng)層硬件抽象層HAL板級(jí)支持包BSP設(shè)備驅(qū)動(dòng)程序?qū)崟r(shí)操作系統(tǒng)RTOSOS的應(yīng)用程序接口API應(yīng)用程序APP嵌入式處理器

2021-07-16 08:15:30

給大家介紹的是微處理器CPU性能測(cè)試基準(zhǔn)Dhrystone。 在嵌入式系統(tǒng)行業(yè)用于評(píng)價(jià)CPU性能指標(biāo)的標(biāo)準(zhǔn)主要有三種:Dhrystone、MIPS、CoreMark,其中Dhrystone是一種

2021-12-15 08:44:56

微控制器和微處理器概念和實(shí)際應(yīng)用,怎么區(qū)分?

2023-10-23 06:25:51

微處理器的結(jié)構(gòu)是由哪些部分組成的?微處理器的代碼是如何執(zhí)行的呢?

2022-02-28 09:25:10

結(jié)構(gòu)1微處理器的外部結(jié)構(gòu)總線的功能微處理器的內(nèi)部結(jié)構(gòu)典型的CPU內(nèi)部結(jié)構(gòu)圖堆棧指針SP微處理器的外部結(jié)構(gòu)8086CPU有40個(gè)管腳,稱為微處理器的總線總線的功能微處理器的內(nèi)部結(jié)構(gòu)典型的CPU內(nèi)部結(jié)構(gòu)

2022-02-14 07:40:41

FPGA的嵌入式應(yīng)用。某人工神經(jīng)網(wǎng)絡(luò)的FPGA處理器能夠?qū)?shù)據(jù)進(jìn)行運(yùn)算處理,為了實(shí)現(xiàn)集數(shù)據(jù)通信、操作控制和數(shù)據(jù)處理于一體的便攜式神經(jīng)網(wǎng)絡(luò)處理器,需要設(shè)計(jì)一種基于嵌入式ARM內(nèi)核及現(xiàn)場(chǎng)可編程門陣列FPGA的主從結(jié)構(gòu)處理系統(tǒng)滿足要求。

2019-09-20 06:15:20

快速傅里葉變換(FFT)在雷達(dá)、通信和電子對(duì)抗等領(lǐng)域有廣泛應(yīng)用。近年來(lái)現(xiàn)場(chǎng)可編程門陣列(FPGA)的飛速發(fā)展,與DSP技術(shù)相比,由于其并行信號(hào)處理結(jié)構(gòu),使得FPGA能夠很好地適用于高速信號(hào)處理

2019-08-28 06:10:15

1、ARM微處理器及編程模式計(jì)算機(jī)體系結(jié)構(gòu):馮/哈馮·諾依曼結(jié)構(gòu)核心思想:將程序(指令序列的集合)和數(shù)據(jù)存放在同一存儲(chǔ)器的不同地址;順序執(zhí)行指令;執(zhí)行過(guò)程:取指令(or數(shù)據(jù))→分析指令→執(zhí)行指令哈佛

2022-05-11 17:18:11

求一種多處理器并行計(jì)算機(jī)系統(tǒng)的設(shè)計(jì)方案

2021-04-27 06:58:57

求大神分享一種基于FPGA的級(jí)聯(lián)結(jié)構(gòu)FFT處理器的優(yōu)化設(shè)計(jì)

2021-05-06 07:34:53

的修改方面缺乏靈活性。本文介紹一種嶄新的基于Matlab與QuartusII的DSP處理器的設(shè)計(jì)軟件DSP Builder,詳細(xì)介紹了其設(shè)計(jì)流程與優(yōu)點(diǎn),并以DDS直接數(shù)字合成器的實(shí)現(xiàn)為例說(shuō)明用該軟件來(lái)設(shè)計(jì)DSP處理器的方法以及與Matlab、QuartusÊ之間的關(guān)系。

2011-03-03 10:05:43

怎樣去設(shè)計(jì)可擴(kuò)展FFT處理器?可擴(kuò)展FFT處理器的結(jié)構(gòu)是如何構(gòu)成的?

2021-05-06 07:52:19

怎樣設(shè)計(jì)FIR濾波器結(jié)構(gòu)?怎樣設(shè)計(jì)級(jí)聯(lián)型信號(hào)處理器?如何對(duì)級(jí)聯(lián)型信號(hào)處理器進(jìn)行仿真測(cè)試?

2021-04-28 07:04:01

急求一份各種嵌入式處理器資料介紹文檔,包含處理器各項(xiàng)應(yīng)用及原理介紹,越詳細(xì)越好!謝謝!

2019-08-09 04:59:34

微處理器體系結(jié)構(gòu)由哪幾部分組成?超標(biāo)量處理器的微體系結(jié)構(gòu)由哪幾部分組成?

2022-02-28 07:31:47

面向多核處理器的低級(jí)并行程序驗(yàn)證要 隨著多核處理器的廣泛使用以及人們對(duì)軟件提出了更高的可靠性要求,多核并行程序驗(yàn)證的重要性日益凸顯。本文提出了一個(gè)完整的基于多核的并行程序驗(yàn)證框架,該驗(yàn)證框架包括抽象

2009-10-06 09:56:26

采用軟硬件結(jié)合的方法,給出一種基于VLIW 的并行可配置橢圓曲線密碼體制(ECC)專用指令協(xié)處理器架構(gòu)。該協(xié)處理器采用點(diǎn)加、倍點(diǎn)并行調(diào)度算法,功能單元微結(jié)構(gòu)采

2009-03-20 16:14:02 25

25 從網(wǎng)絡(luò)處理器的體系結(jié)構(gòu)入手,在線程和微引擎層次上對(duì)IXP系列網(wǎng)絡(luò)處理器的并行環(huán)境進(jìn)行抽象分析,在線程方面闡述了順序和非順序情況下不同的編程方法及其對(duì)應(yīng)的效率和吞吐

2009-04-20 09:20:04 13

13 ARM/THUMB微處理器結(jié)構(gòu)及指令系統(tǒng) : 本章簡(jiǎn)要介紹了ARM/THUMB微處理器的一些基本概念、應(yīng)用領(lǐng)域及特點(diǎn),以引導(dǎo)讀者進(jìn)入ARM/THUMB的殿堂。本章主要內(nèi)容有: ARM/THUMB

2009-06-17 00:22:29 33

33 提出了一種由6片ADSP-21161構(gòu)成的新型的多DSP并行處理結(jié)構(gòu),它具有運(yùn)算能力強(qiáng)、I/O帶寬寬、通信手段多樣、能靈活地改變拓?fù)?b class="flag-6" style="color: red">結(jié)構(gòu)、可擴(kuò)展性和通用性強(qiáng)等特點(diǎn),并且以此并行計(jì)算結(jié)

2009-11-26 15:18:05 6

6 在OFDM系統(tǒng)的實(shí)現(xiàn)中,高速FFT處理器是關(guān)鍵。在分析了基4按時(shí)域抽取快速傅立葉變換(FFT)算法特點(diǎn)的基礎(chǔ)上,研究了一種高性能FFT處理器的硬件結(jié)構(gòu)。此結(jié)構(gòu)能同時(shí)從四個(gè)并行存

2010-07-02 16:51:15 11

11 一種具有功耗管理特性的DSP處理器的結(jié)構(gòu)設(shè)計(jì)。該處理器采用4級(jí)流水線和增強(qiáng)型的哈佛并行系統(tǒng)結(jié)構(gòu)及完善的時(shí)鐘管理模塊,提供了一種DSP處理器的集成設(shè)計(jì)。

2010-11-19 14:45:37 21

21 通過(guò)對(duì)目前國(guó)內(nèi)外主流嵌入式處理器體系結(jié)構(gòu)創(chuàng)新與發(fā)展的研究,著重從處理器體系結(jié)構(gòu)中 RISC 規(guī)則的突破、數(shù)據(jù)處理、多線程、多核處理器的構(gòu)成等多種并行技術(shù)的應(yīng)用,對(duì)提高系統(tǒng)

2011-08-18 14:36:46 30

30 基于FPGA的嵌入式多核處理器及SUSAN算法并行化

2016-08-30 18:11:47 24

24 目前,嵌入式多核處理器已經(jīng)在嵌入式設(shè)備領(lǐng)域得到廣泛運(yùn)用,但嵌人式系統(tǒng)軟件開發(fā)技術(shù)還停留在傳統(tǒng)單核模式,并沒(méi)有充分發(fā)揮多核處理器的性能。程序并行化優(yōu)化目前在PC平臺(tái)上有一定運(yùn)用,但在嵌入式平臺(tái)上還很

2017-10-16 10:01:55 1

1 基于FPGA和多DSP的多總線并行處理器設(shè)計(jì)

2017-10-19 13:40:31 4

4 。并行計(jì)算是提高處理速度最有效的技術(shù)之一,圖像并行處理技術(shù)為提高圖像處理效率提供了廣闊的空間。圖像并行處理包括并行算法和多處理器并行硬件系統(tǒng),圖像處理并行算法的執(zhí)行效率依賴于多處理器系統(tǒng)的硬件結(jié)構(gòu)。通常,一種并行

2017-10-24 11:39:15 0

0 機(jī))節(jié)點(diǎn)集成到同一芯片內(nèi),各個(gè)處理器并行執(zhí)行不同的線程或進(jìn)程。在基于SMP結(jié)構(gòu)的單芯片多處理機(jī)中,處理器之間通過(guò)片外Cache或者是片外的共享存儲(chǔ)器來(lái)進(jìn)行通信。而基于DSM結(jié)構(gòu)的單芯片多處理器中,處理器間通過(guò)連接分布式存儲(chǔ)器的片內(nèi)高速交叉開關(guān)網(wǎng)絡(luò)

2017-10-26 16:24:14 0

0 。并行計(jì)算是提高處理速度最有效的技術(shù)之一,圖像并行處理技術(shù)為提高圖像處理效率提供了廣闊的空間。圖像并行處理包括并行算法和多處理器并行硬件系統(tǒng),圖像處理并行算法的執(zhí)行效率依賴于多處理器系統(tǒng)的硬件結(jié)構(gòu)。通常,一種并行

2017-11-03 10:47:48 0

0 TMS320C55x DSP是一種高性能的數(shù)字信號(hào)處理器,其強(qiáng)大的并行處理能力能夠進(jìn)一步提高其運(yùn)算能力。本文介紹了C55xDSP的內(nèi)核結(jié)構(gòu)以及用戶自定義并行指令時(shí)必須遵守如下3條并行處理基本規(guī)則

2017-11-03 16:19:47 2

2 SoC的概念提出之后,隨著并行計(jì)算技術(shù)與深亞微米技術(shù)進(jìn)步,出現(xiàn)了以網(wǎng)絡(luò)互連的大規(guī)模并行處理系統(tǒng)芯片( MPP SoC),即陣列處理器系統(tǒng)芯片( Array Processor SoC),目前系統(tǒng)芯片

2017-11-16 16:05:57 12

12 ,可以完成并行化的測(cè)試構(gòu)架。具有此結(jié)構(gòu)的測(cè)試系統(tǒng)利用PCI Express提高了數(shù)據(jù)吞吐量,使用LabVIEW、多核處理器和FPGA增強(qiáng)了處理能力,最后利用NI TestStand軟件降低了每個(gè)待測(cè)單元的總體測(cè)試時(shí)間和費(fèi)用。

2017-11-16 20:31:57 8828

8828

Vviado-HLS基于Xilinx FPGA對(duì)C的解析,綜合原理。Vivado-HLS FPGA并行與處理器架構(gòu) 與處理器架構(gòu)相比,F(xiàn)PGA結(jié)構(gòu)具有更高的并行。Vivado-HLS對(duì)軟件C程序編譯時(shí)與處理器編譯是不一樣的執(zhí)行機(jī)制。

2017-11-18 12:23:09 2377

2377

摘要:并發(fā)與并行是兩個(gè)既相似而又不相同的概念:并發(fā)性,又稱共行性,是指能處理多個(gè)同時(shí)性活動(dòng)的能力;并行是指同時(shí)發(fā)生的兩個(gè)并發(fā)事件,具有并發(fā)的含義,而并發(fā)則不一定并行,也亦是說(shuō)并發(fā)事件之間不一定要同一時(shí)刻發(fā)生。

2017-12-08 09:12:33 65331

65331

異構(gòu)并行計(jì)算包含兩個(gè)子概念:異構(gòu)和并行。

1異構(gòu)是指異構(gòu)并行計(jì)算需要同時(shí)處理多個(gè)不同架構(gòu)的計(jì)算平臺(tái)的問(wèn)題。

2并行是指異構(gòu)并行計(jì)算主要采用并行的編程方式,所有的處理器都是多核向量處理器,要發(fā)揮多種處理器混合平臺(tái)的性能必須要采用并行的編程方式。

2018-01-25 16:37:58 6230

6230

本文對(duì)處理器、內(nèi)核和芯片的這三個(gè)概念分別進(jìn)行了介紹,最后總結(jié)了處理器,內(nèi)核,芯片這三個(gè)概念的區(qū)別。

2018-04-23 15:42:36 72009

72009

本文首先介紹了微處理器內(nèi)部結(jié)構(gòu)與分類,其次介紹了cpu的概念與CPU物理結(jié)構(gòu),最后分析了微處理器是否就是cpu以及它們兩者之間的區(qū)別。

2018-04-24 08:59:27 65624

65624

本文首先介紹了協(xié)處理器概念,其次介紹了協(xié)處理器內(nèi)部結(jié)構(gòu)與手機(jī)協(xié)處理器的作用,最后介紹了蘋果的M8協(xié)處理器的作用。

2018-04-24 09:27:14 20732

20732 本文首先介紹了協(xié)處理器的相關(guān)概念,其次分析了驍龍835里是否有協(xié)處理器,最后闡述了驍龍835的性能參數(shù)。

2018-04-24 15:14:39 6124

6124 常常在嵌入式領(lǐng)域使用,常見(jiàn)的是通用嵌入式處理器+DSP核。本文探究的嵌入式多核處理器采用同構(gòu)結(jié)構(gòu),實(shí)現(xiàn)同一段代碼在不同處理器上的并行執(zhí)行。

2018-11-19 09:57:00 2394

2394

本文主要介紹Xilinx公司的MicroBlaze處理器的結(jié)構(gòu)及其原理。

該介紹MicroBlaze處理器時(shí),重點(diǎn)介紹了MicroBlaze處理器結(jié)構(gòu),MicroBlaze處理器信號(hào)接口,MicroBlaze處理器應(yīng)用二進(jìn)制接口和MicroBlaze指令集結(jié)構(gòu)。

2018-09-05 08:00:00 282

282 4分鐘的FPGA簡(jiǎn)單入門介紹,主要介紹了邏輯塊、相對(duì)于處理器的并行操作。搬運(yùn)于YouTube,字幕自制。

2019-08-29 06:05:00 2341

2341 本書詳盡、系統(tǒng)的介紹了ARM微處理器的教材。它不僅僅具體說(shuō)明了微處理器的結(jié)構(gòu)和原理,還介紹了設(shè)計(jì)微處理器和嵌入微處理器核心的片上系統(tǒng)(SOC)概念和方法。

2020-01-02 17:00:30 28

28 經(jīng)常能夠聽到專業(yè)人員在談處理器,那么處理器是什么?

2020-06-13 10:23:47 14401

14401 出了四核心嵌入式并行處理器FPEP的結(jié)構(gòu)設(shè)計(jì)并建立了FPGA驗(yàn)證平臺(tái).為了對(duì)多核處理器平臺(tái)性能進(jìn)行評(píng)測(cè),提出了基于OpenMP的3種可行的圖像處理領(lǐng)域的經(jīng)典算法SUSAN算法的并行化方法:直接并行

2021-02-03 16:26:00 8

8 《微處理器體系結(jié)構(gòu)》適合作為高等院校集成電路設(shè)計(jì)相關(guān)專業(yè)工程碩士的教材,并可以作為微處理器硬件與軟件設(shè)計(jì)相關(guān)專業(yè)高年級(jí)本科生和研究生的教材。

《微處理器體系結(jié)構(gòu)》是一本系統(tǒng)介紹各種類型微處理器

2021-04-14 10:29:03 0

0 EE-263:在TigerSHARC?處理器上并行實(shí)現(xiàn)定點(diǎn)FFT

2021-05-16 08:53:56 2

2 WOLA 濾波器組協(xié)處理器:介紹性概念和技術(shù)

2022-11-15 19:48:19 1

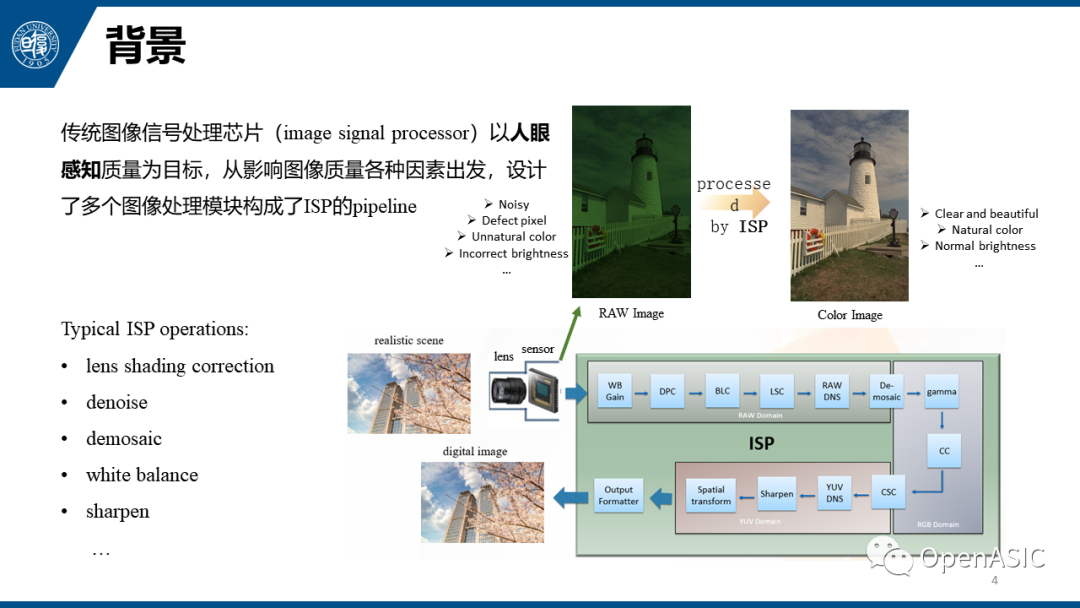

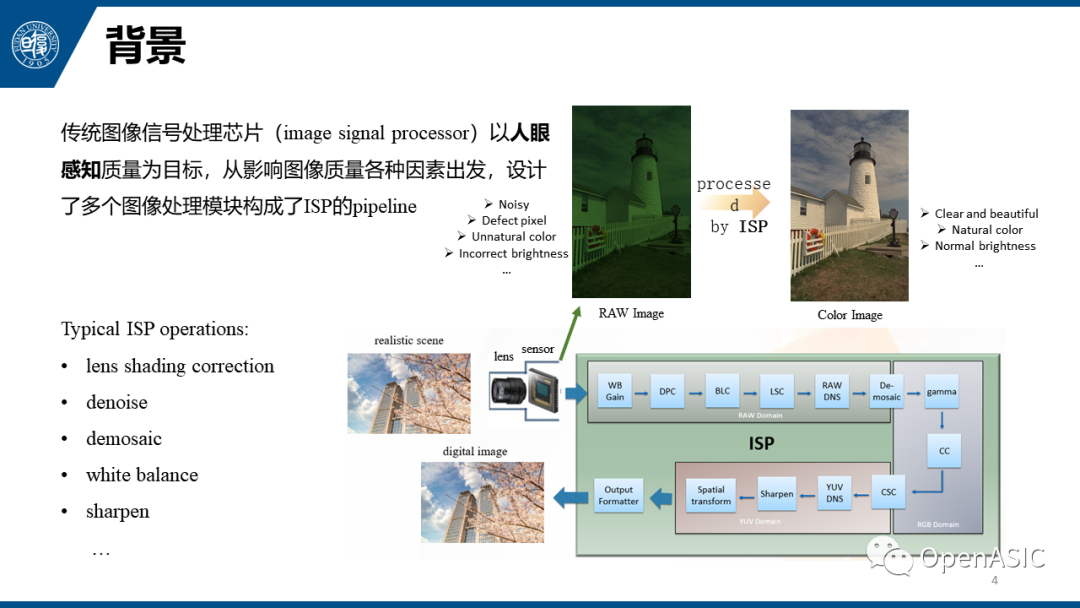

1 本文介紹了ISP(圖像處理器)的基本概念,從缺陷、顏色、噪聲、清晰度、動(dòng)態(tài)范圍等5個(gè)影響圖像質(zhì)量的關(guān)鍵因素出發(fā),詳細(xì)介紹ISP中與這些因素相關(guān)聯(lián)的功能模塊。

2023-02-08 16:12:31 1305

1305

在嵌入式系統(tǒng)開發(fā)中,C預(yù)處理器是非常重要的一部分,可以在編譯之前對(duì)源代碼進(jìn)行宏替換、條件編譯和包含等處理。在本文中,我們將介紹嵌入式C預(yù)處理器的基本概念和常用指令。

2023-04-13 16:11:06 644

644

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論