?作者:蔣華,賈永興,楊亞濤,楊建喜

當前,IP網絡百兆甚至千兆的速率已經成為可能,帶寬的提升為、在IP網絡上傳輸語音、視頻提供了有力的前提條件。IP視頻電話越來越多地得到廣泛應用并將引領現代通信的潮流。但由于IP網絡的開放性,敏感信息可能被輕易地竊取、篡改、非法復制和傳播,因此對IP視頻通信的保密性和可靠性提出了更高的要求。為了確保IP視頻電話端到端的通信安全,必須對SIP信令和RTP音視頻數據進行加密處理。

全球最大IP電話提供商Skype在其軟件中內嵌了加密系統,安全專家Phil Zimmermann提出了ZRTP密鑰協商協議并開發了IP電話安全軟件Zfone,這些均采用軟件方式實現加密,當處理器性能較低時,這種方式必然會影響到通話質量。為此本文設計了一種適合于IP視頻電話的高速硬件加密引擎。

IP視頻電話通信具有以下特點:

(1) 占用帶寬大。目前常用音頻算法編碼速率約為10 Kb/s,視頻算法編碼速率約為1 Mb/s(視不同圖像質量和算法而有不同)。

(2)實時性要求高。人的聽覺對時延超過400 ms的語音信號比較敏感。

(3) SIP信令和RTP音視頻數據采用UDP方式傳輸,UDP協議是面向非連接的協議,數據包在網絡繁忙的情況下可能被丟棄。

針對這些特點,設計加密引擎協助IP視頻電話終端完成各類數據加密功能,密鑰協商和密鑰管理由IP視頻電話終端處理,兩者之間通過SPI總線通信。

1 硬件設計

1.1 處理器選擇

針對IP視頻電話通信的特點處理器可以選擇專用密碼算法芯片,但在使用上缺乏靈活性,如果需要更改密碼算法或者相關參數,需重新設計,因此本系統選用TI公司的DSP處理器TMS320C6416T。TMS320C6416T是基于VelociTI.2TM構架的32位定點高性能DSP處理器,主頻高達1GHz,處理能力可達8 000 MIPS。它采用超長指令字結構(VLIW),每個時鐘周期可以執行8條指令。TMS320C6416T內部集成大容量存儲器,采用兩級緩存結構,即一級緩存(L1)和二級緩存(L2)。

TMS320C6416T強大的計算、數據存儲能力大大縮短了實現各種算法的時間,迎合了IP視頻電話通信的實時性要求。它既可用于IP視頻電話終端加密,也可擴展用于其他大流量數據加密(如流媒體服務器)。在處理更改加密算法、系統參數和通信接口方面,相對于專用處理器,DSP更具靈活性和可擴展性。

1.2 硬件結構及注意事項

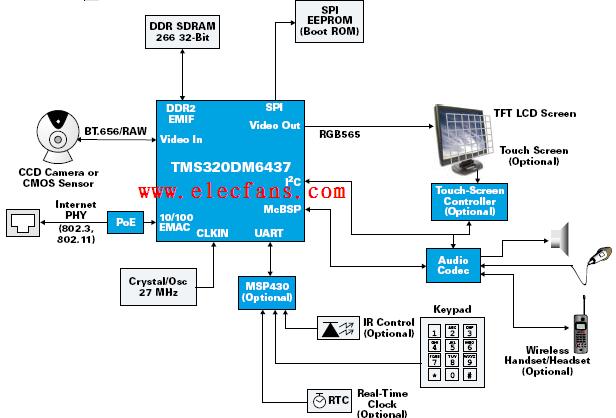

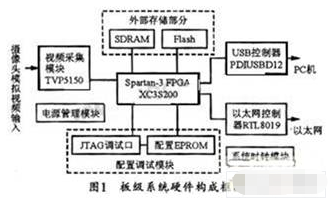

加密引擎以TMS320C6416T為核心,包括SDRAM、Flash、電源、JTAG接口、看門狗等。加密引擎和IP視頻電話終端通過SPI總線通信,硬件總體結構如圖1所示。

DSP作為系統的核心,在完成數據加解密運算的同時,還要與IP視頻電話終端實時通信,交互SIP信令、音視頻數據、種子密鑰及控制命令等。

SDRAM采用HY57V283220T(4 M×32 bit),工作時鐘為133 MHz,用于數據存儲。Flash采用39VF800A(8 M×16 bit),存取速度為70 ns,100 000次可擦寫,用于程序存儲和DSP上電自舉。電源為整個系統供電,看門狗用于監視系統的正常運行,JTAG接口用于DSP仿真調試。

IP視頻電話終端除了向加密引擎發送待處理數據和命令外,還需具備密鑰協商和管理、用戶權限控制、網絡傳輸等多種功能。在設計過程中,應重點注意以下問題:

(1) DSP、SDRAM等芯片的功耗較大,需根據具體功耗參數設置合理的電源和地線的布線寬度,注意電路板在物理空間的散熱問題;考慮DSP為BGA封裝,PCB應采用多層板設計(8層或更多層),設置單獨的電源層和地層,以提高系統的可靠性。

(2) DSP工作在1 GHz主頻下、SDRAM工作在133 MHz時鐘頻率下,布局布線時要充分考慮信號的完整性。在實際設計中采用合適的總線拓撲結構、合理的疊層結構,對高速數字信號線在仿真的基礎上加入適當的端接消除信號反射,以解決高速信號完整性問題。

2 軟件設計

2.1 算法選擇及加密方式

2.1.1 AES算法和工作模式

IP視頻電話數據流量大,SIP信令和音視頻數據采用UDP方式傳輸,不可避免地存在數據丟包問題,因而使用分組密碼算法較為合適。考慮密碼算法的速度和安全性等因素,本系統采用AES分組密碼算法實現各種數據端到端加密。

AES算法作為迭代分組密碼算法其分組長度和密鑰長度均可改變,在使用上更加靈活安全。論證表明,它能夠抵抗所有目前技術水平下的已知和潛在的密碼攻擊,是更加安全可靠的加密算法。AES使用長為32×Nk(Nk=4、6、8)的比特流作為密鑰,每次對長為32×Nb(Nb=4、6、8)比特的明文組進行加密,得到的密文組長為32×Nb比特,迭代輪數Nr=Max(Nb,Nk)+6。

AES算法有5種基本工作模式:ECB、CBC、OFB、CFB、CTR。考慮到IP數據包丟失問題,如采用反饋模式需考慮數據同步問題,因而降低了數據處理效率。而ECB模式簡單易操作,不存在數據丟失產生的通信同步問題SIP信令中的會話描述符SDP和音視頻數據都沒有固定的格式,攻擊者也難以通過統計特性分析密文,因而采用ECB模式是安全易行的。

2.1.2 數據加密方式

在IP網絡中,視頻和音頻數據是分類打包、分段傳輸的,因而對它們的加密處理也需單獨進行。目前針對視頻數據主要有選擇性加密和完全加密2種方式[4]。選擇性加密利用視頻數據的數據結構,對視頻流中的部分數據(如I幀)加密,這有利于減小系統開銷,但安全性較差。而完全加密不考慮視頻數據結構,加密所有視頻碼流,雖然系統開銷較大,但安全性較高。本系統對視頻、音頻數據、SIP信令均采用完全加密方式。

2.2 通信機制和數據格式

2.2.1 通信機制

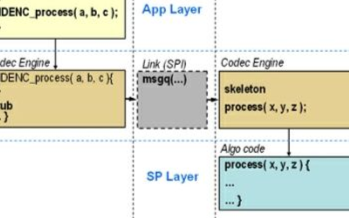

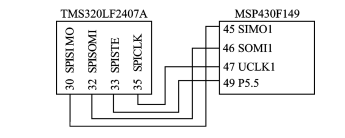

DSP和IP視頻電話終端通過SPI總線通信,SPI作為一種串行同步通信方式,通信速率可達到4 Mb/s或者更高,適合音視頻數據傳輸。在本系統中,將DSP的多通道緩沖串行口McBSP[2]配置為SPI模式,IP視頻電話終端配置為主設備,DSP配置為從設備。

采用中斷方式接收或發送數據會增加CPU的負擔。將增強型存儲器直接訪問EDMA[3]與McBSP結合使用,使得CPU加解密數據與EDMA數據接收或發送并行進行,將大大提高DSP的運行效率。具體流程為:(1)DSP通過McBSP接收待處理數據,將數據保存在指定映射的存儲器中,隨后EDMA通道搬運數據至片內L2緩存以供CPU提取并處理;(2)CPU加解密處理完成后,通過相反的路徑發送給IP視頻電話終端。為確保CPU數據處理和EDMA數據傳輸同步,在L2緩存開辟一對乒乓緩存(Ping-Pong Buffer),分別用于接收和發送數據。

2.2.2 數據格式

為了便于處理器之間的數據交互,定義通信數據格式如下:

數據頭標志:長度為2 B,表示一個數據包的起始。

數據類型:長度為2 B,定義0x0001為IP視頻電話終端發送的待加密數據,0x0010表示IP視頻電話終端發送的待解密數據,0x0100表示DSP回送給IP視頻電話終端的已加密數據,0x1000表示DSP回送給IP視頻電話終端的已解密數據,0x0101表示IP視頻電話終端發送的種子密鑰,0x1010表示其他控制數據。

數據長度:長度為2 B,表示待處理數據的有效字節數。以太網幀的最大長度是1 500 B,因此不能超過這個長度。

數據頭校驗和:長度為2 B,防止頭部因傳輸錯誤而執行誤操作。

RTP數據載荷:小于1 500 B,表示加/解密數據、種子密鑰、控制數據等。

2.3 軟件設計要點

根據DSP系統架構,考慮AES算法和通信數據的特點,充分發揮DSP的數據處理能力是軟件設計的重點。

2.3.1 AES算法優化設計

AES的輪函數由字節變換、行位移、列混合、密鑰加4個部件組成。(1)字節變換是非線性變換,獨立地對狀態的每個字節進行變換,可用代換表(S盒)的方式實現;(2)行移位是將狀態陣列的各行進行循環移位;(3)列混合使用有限域上的矩陣乘法,可以用查表操作實現;(4)密鑰加可以通過執行一個32位“異或”運算來實現。通過算法優化,可將有限域矩陣乘法和S盒簡化為查表和“異或”兩種基本運算,并充分利用DSP處理器32位總線結構特點,大大降低了算法復雜度。

2.3.2 使用軟件流水技術

AES是迭代分組密碼,共Nr輪迭代,一般采用C循環程序實現,循環是影響系統實時性的一個重要因素。軟件流水技術用于設置循環內指令的運行方式,使循環的多次迭代能夠并行執行。程序應該考慮合理的循環迭代次數,以保證軟件流水能夠順利進行。將循環展開可以增加及并行執行指令數,從而改進流水編排,提升循環性能。同時應該正確使用pragma指示和-ms、-mh等編譯選項。

2.3.3 合理設置CCS編譯器選項

使用const關鍵字定義變量可提高代碼性能和穩定性;聯合使用-pm與-o3選項可進行程序級優化并有效地消除相關性;-mt選項有利于消除存儲器相關性;這些選項都能大大提升代碼的執行速度[6]。測試表明,選擇C代碼優化選項,可使AES算法的執行速度提高近一倍。

系統關鍵代碼如下:

void main()

{ //初始化CSL

CSL_init();

//SPI配置

McBSP_config(&McBSPConfig);

//乒乓方式EDMA配置

EDMA_config(hEDMAPing, &EDMAConfigRcv);

EDMA_config(hEDMAPong, &EDMAConfigSnd);

//密鑰擴展

KeyExpansion(CipherKey,ExpandedKey);

while(1)

{ //EDMA傳輸完成后對數據加解密密處理

if(EDMAFlag)

DataProcessing();

}

}

3 測試結果

3.1 加密速率

表1是CCS軟件Profile對各函數指令開銷的評估結果。

在該測試中,取Nb=Nk=4,Nr=10。經過DataProcessing運算加密1 536字節數據,總指令開銷128600。取DSP速率8 000 MIPS,則運行時間為128 600/8 000=16.075 μs,加密運算速率為1 536×8/16.075=765.41 Mb/s。該數據吞吐量完全滿足了IP視頻電話的實時性要求。

3.2 效率對比

參考文獻[5]在TMS320C54x DSP上實現了AES算法,表2給出兩種實現方式的對比。

兩種處理器的架構和處理速度是不同的,在軟件設計上會有不同的處理方法,若僅考慮DSP速率對算法速率的影響,本系統加密效率更高。另外,本測試僅考慮了AES加密算法代碼的指令開銷,實際中還要考慮DSP存取數據、中斷處理等其他任務。

系統首次采用DSP TMS320C6416T處理器,合理的硬件設計確保了系統的可靠性,EDMA與McBSP相結合的通信機制提高了通信效率,優化的軟件設計提升了加解密速率。本系統已成功應用于IP視頻電話保密通信,經擴展設計,也可以應用于多媒體服務器,實現多通道數據加密。本方案對VOIP、視頻監控、視頻會議等領域具有很高的參考價值。

責任編輯:gt

電子發燒友App

電子發燒友App

評論