引言

頻率是指某周期現象在單位時間內所重復的次數,它與時間在數學上互為倒數。時間頻率的精確測量促進了科學的發展,而科學的發展又反過來把時間頻率的測量提高到新的高度。特別在最近的幾十年里,頻率和時間的測量精度已達到非常高的水平,即已遠遠超過其他所有物理量的測量精度。它主要的應用領域有導航和通信兩大類,以及空間技術、工業生產、交通、科學研究及天文學與計量學方面。

為了適應現代技術發展的要求,新型的頻率計中都使用了單片機進行數據處理,這樣,由軟件代替了復雜的硬件電路,使儀器的結構簡化,功能增強。本文給出一種基于TMS320F2812(簡稱F2812)DSP的一種簡易測頻方法。該方法有效利用F2812的片內外設事件管理器的捕獲功能,在被測信號的有效電平跳變沿捕獲計數,電路實現多靠軟件設置,運算簡單,實時性好,測量精度高。

1 測量方法

常用的測頻方法主要有直接測頻法、直接測周法以及多周期測量法。直接測頻法雖在高頻段的精度較高,但在低頻段的精度較低,直接測周法則恰恰相反。多周期測量法是將被測信號和標準信號分別輸入到兩個計數器,其實際閘門時間不是固定值,而是被測信號周期的整數倍,因此消除了對被測信號計數時產生的±1 Hz的計數誤差,其精度僅與閘門時間和標準頻率有關。因此本設計采用多周期測量法作為具體的實施方案。

2 系統的設計

2.1 系統的硬件設計

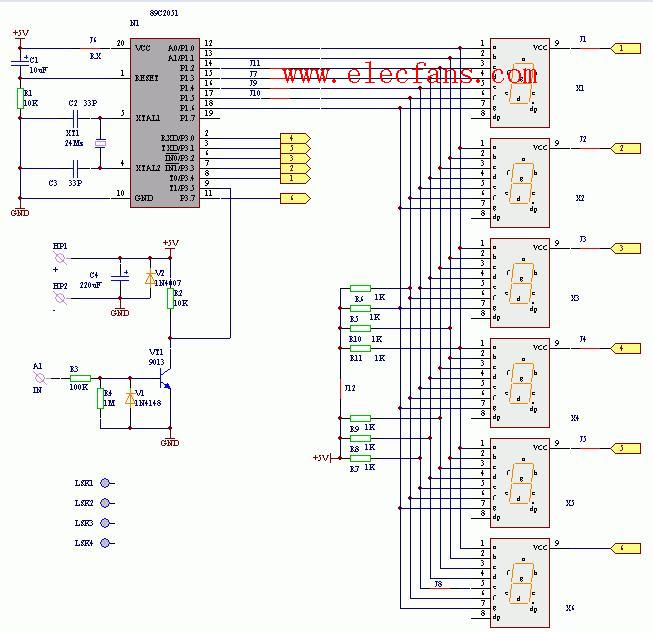

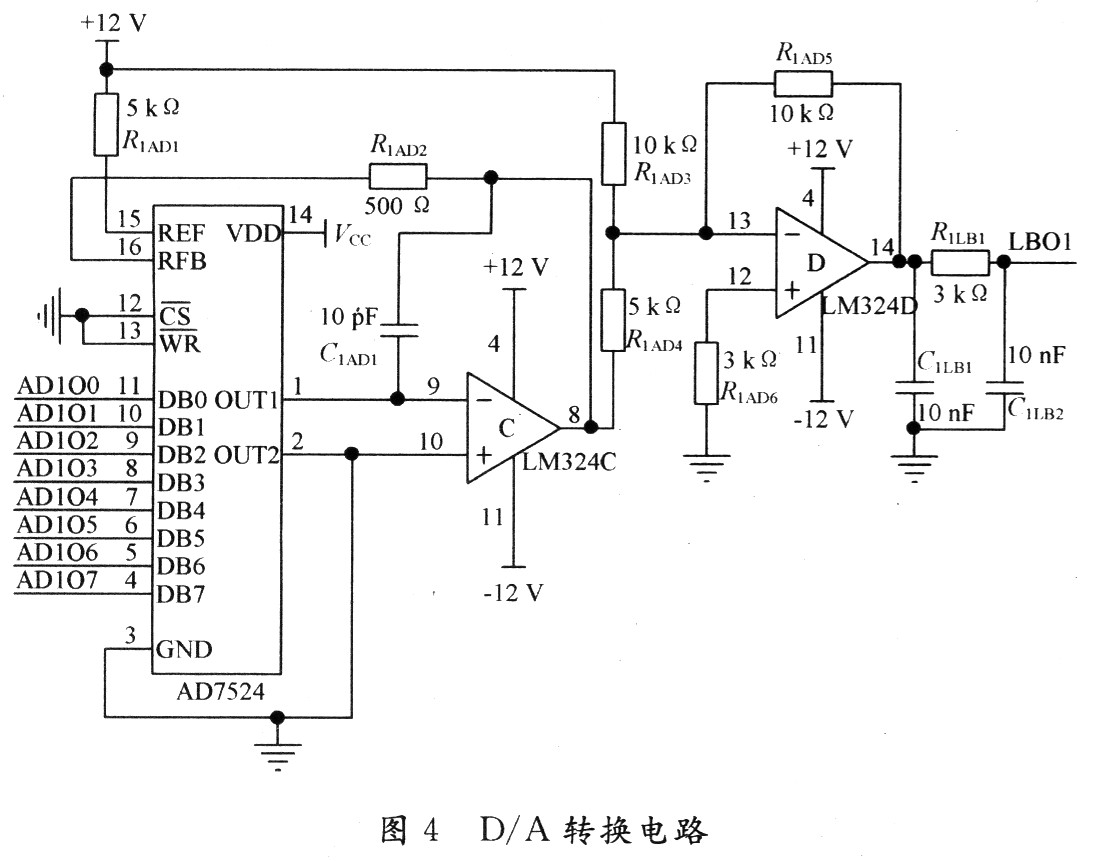

硬件系統總體框圖如圖1所示。被測信號首先經過限幅放大、直流偏置、整形電路,變換為0~3.3 V的方波信號,然后再進入DSP,利用其定時器和捕獲單元實現頻率的測量。測量完成后,一方面可由鍵盤設置相關參數通過LCD顯示測量結果,另一方面可通過RS一232傳送給PC機顯示測量結果。另外,為了提高系統的可靠性,增加了一個自我校準電路,即在測量之前,可通過軟件設置產生1 MHz的標準脈沖信號,送到信號調理模塊的輸入端,檢測測量結果是否正確,從而達到自我校準的目的。

本設計選用美國德州儀器公司(TI)的F2812 DSP作為核心處理單元。F2812是TI公司近幾年推出的高速、高精度的工業控制DSP芯片。它運算速度快,工作時鐘頻率達150 MHz,指令周期可以達到6.67 ns以內,低功耗(核心電壓1.8 V,I/O口電壓3.3 V)。它采用哈佛總線結構,具有強大的操作能力;外圍設備包括3個32位的CPU定時器,16通道的12位A/D轉換器,串行外圍接口(SPI),2個串行通信接口(SCI)等。其片內外設時間管理器含有2個模塊(EVA和EVB),每個模塊都包括2個通用定時器,3個全比較/PWM單元,3個捕獲單元和 1個正交編碼脈沖電路。本設計主要利用EVA中的2個通用定時器(T1和T2),2個捕獲單元(CAPl和CAP3),EVB中的1個通用定時器 (T3)。具體測量原理如圖2所示。

首先設定T3比較值(預置閘門時間為0.012 8 s),設定T1的比較值為1,使能CAPl。然后使能T1,當其接收到一個整周期的被測信號時即可產生比較輸出,同時產生比較中斷,讀取CAPl的棧值 (即T2的初值t2_1),清T1、T2上溢次數,使能CAP3和T3。最后當T3定時結束,借助于D觸發器在被測信號的下一個上升沿到來時,切斷T1的比較輸出,同時PDPINTA將被置位,然后記錄T1和T2的上溢次數tlofcount、t2ofcount,讀取CAPl的棧值(即T2的末值 t2_2)和CAP3的棧值(即T1的末值tl_2)。由所得數據計算頻率,禁止T1、T2、CAPl和CAP3。頻率計算公式為:

注意:CAPl的捕獲時基為T2,CAP3的捕獲時基為T1,標準頻率信號為150 MHz時鐘頻率的8分頻。

2.2 系統的軟件設計

主監控程序是整個軟件系統的總調度程序,它控制著程序的有序運行。系統在上電或復位后,主程序先調用各模塊的初始化子程序,主要包括GPIO初始化、PIE初始化、EV初始化和SCI初始化。系統初始化完成之后,主程序啟動CPU_Timer0,使能 T1、T2的上溢中斷,啟動CAPl,設置T1的比較值為1,等待T1CINT置位,開始測量頻率。為減小測量過程中產生的隨機誤差,所測結果均取平均值。利用CPU_Timer0產生一定的時間段(O.6s)。該時段結束后(CPU_TimerO中斷標志位置位),即對該段時間段內記錄的測量結果求均值。此時,如果查詢到上位機發出接收請求,則傳送相應數據至PC顯示。然,后,重新初始化定時器和捕獲單元,進入下一輪測量。主監控程序流程如圖3所示。

測頻的部分源代碼如下:

3 誤差分析及測試結果

3.1 量化誤差

設被測信號的頻率為Fx,其真實值為Fxe,標準頻率為Fs,在一次測量中,預置閘門時間為T′,Tpr為實際閘門時間,被測信號計數值為Nx,標準頻率信號計數值為Ns。

Fx計數的起停時間是由該信號的上升沿觸發的,在T′時間內對Fx的計數Nx無誤差,對Fs的計數Ns假設相差N個脈沖,即|△et|≤n。

由于Fx/Nx=Fs/Ns,Fxe/Nx=Fs/(Ns+△et),根據相對誤差公式有:

因此可以得到以下結論:

①相對測量誤差與被測信號的頻率無關。

②增大T′或者提高Fs,可以增大Ns,減少測量誤差,提高測量精度。本設計方案中,預置閘門時間限定了最低的測量精度。

③誤差分析中的n,主要由硬件切斷T1PWM所需要的時間決定,為一個小整型常數。若預置閘門時間Tpr=O.012 8 s,則

即使n取不為l的小整型常數,仍可以使得精度維持在十萬分之一以內,并且可以隨著預置閘門時間的適當延長,得到進一步的提高。

3.2 測量的原理誤差和標準頻率誤差

本測量原理類似多周期同步測量原理,主要的原理誤差來自測量即將結束時,由D觸發器產生低電平跳變來切斷T1PWM,從而使其產生由CAPl和CAP3同時捕獲上升沿的跳變。這段時間主要是由D觸發器的反應時間決定。在測量過程中,針對這部分誤差,可以通過適當增加預置閘門的時間來克服,同時考慮到DSP 內部高速的時鐘頻率,這并不會明顯地增加測量耗時,但卻達到了弱化此誤差的影響、增加測量精度的目的。

標準頻率誤差為△Fs/Fs。因為晶體的穩定度很高,標準頻率誤差可以進行校準,并且已將DSP內部的高速時鐘頻率進行了適當的分頻,所以相對于量化誤差,校準后的標準頻率誤差可以忽略不計。

3.3 測試結果

用函數信號發生器(型號為Tektronix AFG3010;精度為O.000 1%)產生方波信號,用設計的頻率計測出頻率,求出誤差。本測頻系統的測量精度可達到O.01%。根據誤差分析可知,系統的最大誤差發生在預置閘門時間正好填充了整數個被測信號時,即頻率為78.125 Hz或者其整數倍時,所以選擇這些點進行測試。實際的測試數據如表1所列。

4 結論

本文著重分析了數字頻率計的設計方案、硬件組成,以及采用Modbus協議實現上位機與下位機通信的軟件設計。特點有:

①在頻率測量原理方面,由于采用了多周期測量原理,消除了對被測信號計數時產生的±1個計數誤差,其精度僅與閘門時間和標準頻率有關,克服了傳統的測頻法或測周法的不足,實現了寬量程、高精度的頻率測量。同時由于預置閘門時間的存在,保證了當被測頻率在各頻段之間來回切換時,系統反應靈敏,跟隨性能好。

②在系統的總體設計方面,充分利用了F2812 DSP的內部資源,即使用事件管理器中的定時器、捕獲單元完成頻率的測量;使用PWM的輸出實現自檢電路的設計;使用串口通信模塊完成上位機和下位機的通信。在測量結果的顯示方面利用RS232,通信協議采用Modbus協議,實現下位機和上位機的通信,將測量結果在上位機中顯示出來。

本文只探討了如何對單路信號進行頻率測量,而對于多路信號,可先使其經過一個與門,通過軟件判斷哪一路信號,然后再運用本設計方法進行測量。針對這種情況所產生的誤差問題還需作進一步的探討,本文只給出初步的探索。

責任編輯:gt

電子發燒友App

電子發燒友App

評論