本文提出了一種基于FPGA的多路光柵信號采集方案,該方案使用I/O口相對較少的低端FPGA,配合多路選擇開關,通過內部處理,實現了多路光柵信號的采集,結果表明,該方案成本低廉且能滿足精度的要求。

2013-12-30 13:35:40 2174

2174

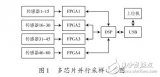

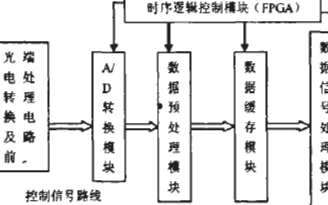

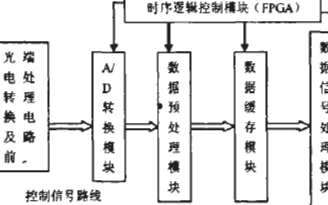

在光纖傳感信號處理系統中,需要處理的是水聽器陣列的海量信號,對處理速度要求高。用FPGA來實現多路高速數據采集、數字信號存取的同步時鐘控制,可使時序關系整齊,延遲一致、易于修改。同時利用FPGA

2020-10-23 10:50:04 1813

1813

本帖最后由 maochengquan 于 2019-12-16 09:32 編輯

用示波器探針接A線,另一端接B線,觀察發送及接收的信號,接收信號呈差分信號波形,但是發送信號是非差分信號,why?電路圖中的二極管均未接。

2019-12-16 08:46:16

比較器將網線傳輸過來的差分信號轉為單端信號,該信號時鐘頻率為100M,電平標準能滿足FPGA的輸入電平標準,波形質量尚可。單端信號直接連接到FPGA,現在如果想用FPGA直接采集,應該怎么處理呢,是當作異步信號直接打拍嗎,過采樣的話時鐘頻率不夠。時鐘恢復目前來不及實現。

2020-03-07 16:01:37

該電路的目的是用3.3VFPGA芯片采集編碼器的光柵信號,而編碼器信號為5v電平故需要電平轉換:5V轉3.3V,采用的電平轉換芯片為SN74LVC4245A。編碼器發出的信號為四路差分信號,需將這四

2015-07-13 21:26:17

號的CPLD也開始支持差分信號了。那么在FPGA中如何正確定義和使用差分信號呢?在這篇文章里,我們基于ALTERA公司的CYCLONE III系列的FPGA芯片,做一些討論。

一,差分信號輸出我們先在設計中

2018-09-03 11:08:41

求大師請教,差分信號在PCB布線中應該注意什么?加什么保護措施?公司用的是DS8921做通信!

2012-08-18 10:20:27

什么是差分信號差分信號與單端信號的區別差分信號的優點差分信號在做pcb設計時的處理方法

2021-03-03 07:09:27

什么是差分信號差分信號與單端信號的區別差分信號的優點差分信號在做pcb設計時的處理方法

2021-01-28 06:01:01

AM26C31差分信號的輸出,需要在差分信號之間接電容嗎?

2018-04-18 09:08:42

一個差分信號是用一個數值來表示兩個物理量之間的差異。從嚴格意義上來講,所有電壓信號都是差分的,因為一個電壓只能是相對于另一個電壓而言的。在某些系統里,系統“地”(GND)被用作電壓基準點。當

2016-11-15 10:39:47

對差分信(VDS)號而言,對其影響最大的因素是它們的對地阻抗是否一致,也就是對地平衡度,它們之間相對的阻抗影響并不特別重要,之間分布電容大了只會衰落信號強度,不會引入噪聲和干擾,也就是對信噪比不會

2019-05-31 08:23:03

差分信號布線時信號完整性問題;影響SI的因素;解決問題的設計辦法;

2016-09-07 11:25:46

差分信號布線誤區

2015-08-27 22:09:50

AM26LS32 按照正常接法輸出端接示波器,按AUTO之后頻率在跳變,是不是說AM26LS32沒有工作,或者輸入不正常。我是按照datasheet說明接線的。看到別人都說能在示波器上看到方波,差分信號來源是松下伺服電機A相反饋,電機轉動的情況下測的

2013-03-01 16:45:15

以下部分來源野火教程、普中教程和百度的內容,后期有時間再整理。1.差分信號1.概述差分信號,又叫差模信號,通過兩根信號線上的電壓差值來表示邏輯0和邏輯1。表示邏輯時,這兩個信號線的振幅相等,相位

2021-08-19 08:11:10

數字和模擬信號都可以定義。 一個差分信號是用一個數值來表示兩個物理量之間的差異。從嚴格意義上來講,所有電壓信號都是差分的,因為一個電壓只能是相對于另一個電壓而言的。在某些系統里,系統“地”(GND)被用作電壓基準點。當“地”當作電壓測量基準時,這種信號規劃被稱之為單端的。我們使用...

2022-01-20 08:19:47

誤區一: 認為差分信號不需要地平面作為回流路徑,或者認為差分走線彼此為對方提供回流途徑。造成這種誤區的原因是被表面現象迷惑,或者對高速信號傳輸的機理認識還不夠深入。雖然差分電路對于類似地彈以及

2016-09-29 11:27:50

各種負載的電流 (I = CΔV/Δt)。因此,軌至軌信號(大 ΔV)的局限性就顯而易見了:需要更多的電源來實現更短的轉換時間(更小的 Δt)。那么我們應如何圍繞數字設計獲得高速信號,并避免單端信號的損耗呢?實施差分信號! 圖 1:單端信號拓撲(左)/差分信號拓撲(右)差分系統一般是三導線系統…

2022-11-22 06:07:48

的信號發送速率、高共模噪聲抗擾度以及更低的功耗等。采用差分信號,升降時間大體會比單端信號短,因此在當前通信系統中 10 Gbps 以上數據速率已成為一個可實現的標準。更小的信號擺幅可使系統整體功率預算

2018-09-17 16:34:43

在高速 PCB 設計中,差分信號的應用越來越廣泛,這主要是因為和普通的單端信號走線相比,差分信號具有抗干擾能力強、能有效抑制EMI、時序定位精確的優勢。作為一名(準)PCB 設計工程師,我們當然需要充分理解差分信號!

2021-02-05 07:27:44

一個差分信號是用一個數值來表示兩個物理量之間的差異。從嚴格意義上來講,所有電壓信號都是差分的,因為一個電壓只能是相對于另一個電壓而言的。在 某些系統里,系統\'地\'被用作電壓基準點。當

2023-11-22 08:30:38

一個差分信號是用一個數值來表示兩個物理量之間的差異。從嚴格意義上來講,所有電壓信號都是差分的,因為一個電壓只能是相對于另一個電壓而言的。在某些系統里,系統'地'被用作電壓基準點。當'地'當作電壓測量

2015-01-07 14:22:17

如果接一路差分信號是不是用信號源雙路信號分別接差分的IQ端,然后剩下的黑線都接地線,并且信號源設置雙端信號輸出,并且信號反向?那如果接雙路差分信號呢?一個信號源夠用嗎?

2017-03-01 12:06:47

差分信號詳細介紹 一個差分信號是用一個數值來表示兩個物理量之間的差異。從嚴格意義上來講,所有電壓信號都是差分的,因為一個電壓只能是相對于另一個電壓而言的。在某些系統里,系統'地'被

2009-09-06 08:58:06

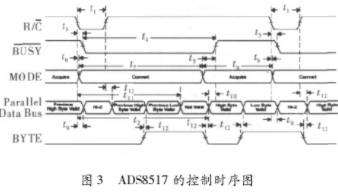

差分信號的讀寫數據問題時序圖高手幫我分析下怎么傳數據的 萬分感謝!

2014-08-04 18:56:49

板卡有四對差分信號,現想要通過FPGA調試下看看是否通路。我用的FPGA中的原語來實現差分信號的收發,可是編譯的時候總出錯,不知道大家有沒有好辦法,怎么調試差分口。

2018-09-21 10:48:41

新系列,專門用于實現多點電纜或背板應用。它不同于標準的LVDS,提供增強的驅動電流,以處理多點應用中所需的雙重傳輸。BLVDS具備大約250mV的低壓差分信號以及快速的過渡時間。這可以讓產品達到自

2016-04-15 16:13:33

差分信號,什么是差分信號一個差分信號是用一個數值來表示兩個物理量之間的差異。從嚴格意義上來講,所有電壓信號都是差分的,因為一個電壓只能是相對于另一個電壓而言的。在某些系統里,系統’地’被用作電壓

2019-05-31 08:01:24

差分信號差分傳輸是一種信號傳輸的技術,區別于傳統的一根信號線一根地線的做法(單端信號),差分傳輸在這兩根線上都傳輸信號,這兩個信號的振幅相等,相位相反。在這兩根線上傳輸的信號就是差分信號。

2019-05-29 06:52:45

請教各位,請問SPWM波是差分信號還是單端信號?

2015-06-10 11:43:14

。 2實現 Xilinx 7系列的差分信號的實現主要通過IBUFDS、OBUFDS、IOBUFDS等原語的調用,在程序中直接進行原語的例化,以IBUFDS和OBUFDS為例: 2.1IBUFDS

2020-12-23 17:17:47

Ping Pang操作,FIFO滿、半滿信號作為使能信號與數字信號處理器TMS320C6713B對接。利用TMS320C6713B的地址數據線與異步雙端口完美對接,實現模擬到數字到數字信號處理整個流程。

2012-06-14 00:11:59

什么是差分信號?為什么要用差分信號?差分放大電路的基本結構和作用差分放大電路的應用電路

2021-03-11 08:21:01

一個差分信號是用一個數值來表示兩個物理量之間的差異。從嚴格意義上來講,所有電壓信號都是差分的,因為一個電壓只能是相對于另一個電壓而言的。在某些系統里,系統'地'被用作電壓基準點。當'地'當作電壓測量

2016-07-14 14:56:43

一個差分信號是用一個數值來表示兩個物理量之間的差異。從嚴格意義上來講,所有電壓信號都是差分的,因為一個電壓只能是相對于另一個電壓而言的。在某些系統里,系統'地'被用作電壓基準點。當'地'當作電壓測量

2016-07-14 09:48:32

你知道什么是差分信號嗎?一個差分信號是用一個數值來表示兩個物理量之間的差異。從嚴格意義上來講,所有電壓信號都是差分的,因為一個電壓只能是相對于另一個電壓而言的。在某些系統里,系統'地'被用作電壓

2016-08-19 11:35:46

如題,請問下,我想用DAQ采集多路信號,現在想把多路信號在不同的波形圖上顯示,每一個波形圖顯示一路信號,如果用拆分信號拆分,我如何確定每一個波形圖顯示的哪一路信號?在下剛學習LV,望各位不吝賜教,多謝多謝!

2013-04-09 10:21:45

選項,而沒有出現“TMS3206713”或者“TMS3206713b”的選項(我們以前做C6455的板子時,在改下拉框內都可以找到“TMS320C6455”的選項)。我想問一下,這個會對仿真器連接芯片

2018-08-02 08:46:30

各位大神,小弟求助:如何實現SPI與差分信號的互相轉換?

2013-03-29 09:26:40

(1)單端信號 以共同的地線為基準。適用于傳感器有共同地線,信號幅值大,傳輸距離近,不易受干擾的場合。 (2)差分信號 每路信號有自己的基準地線,兩根信號極性相反,共模噪聲被抑制。適用于小幅值

2019-01-12 12:18:12

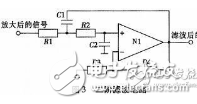

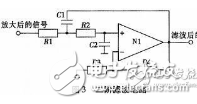

如圖中所示,前級運放輸出一對差分信號,經過處理器切換到二階低通濾波器上,最后傳輸到串行AD進行數據轉換。這里不太明白濾波器前對差分信號的切換如何處理,切換頻率是多大?理論上說AD轉換周期一定需要小于切換周期,對嗎?

2017-03-03 10:53:27

FPGA+DSP構成的光纖傳感信號實時處理系統的硬件及軟件設計.并針對載波相位延遲造成的解調信號幅度衰減提出了解決方法。本系統具有高速實時數據運算能力。可廣泛應用于多路數據采集處理等領域,可升級能力強,應用前景

2021-07-05 11:23:33

時間。針對上述研究現狀和分布式采集場景分析,本文介紹了一種基于FPGA和TOE架構,實現TCP/IP協議數據傳輸的多路采集與切換系統。該系統涉及并行數據采集、多路通道切換、TCP/IP協議通信等模塊

2021-07-12 08:30:00

的信號量特別多時(特別是各種信號量、狀態量),僅僅靠用普通MCU的資源就往往難以完成任務。電子論壇所提出的一種基于FPGA的模擬量、數字量采集與處理系統,利用FPGA的I/O端口多,并且可以自由編程支配

2011-08-23 10:15:34

我們可以將LvCmos 2.5 i / o轉換為Fpga內的差分信令(Lvds)嗎?因為我想使用GTx收發器,收發器只接受差分信號..我可以這樣做嗎?你可以幫忙嗎?/

2020-06-16 14:27:26

正在做一個電壓采集的項目,輸入信號的共模信號,而28377S,16位ADC需要輸入差分信號,我利用下圖的方式將共模信號轉換成差分信號,請教TI工程師,能否這樣做。輸入的共模信號是0—2.5V的直流信號,在輸入之前已經做了濾波處理。ADC的采樣時間是320ns,ADC時鐘頻率是40M。

2020-07-24 12:21:54

來源:互聯網在高速PCB設計中,差分信號的應用越來越廣泛,這主要原因是和普通的單端信號走線相比,差分信號具有抗干擾能力強、能有效抑制EMI、時序定位精確的優勢。作為一名(準)PCB設計工程師,我們必須搞定差分信號,接下來我們了解下相關內容吧!

2020-10-23 08:36:50

如題,需要一個差分信號輸入仿真,不知道怎么產生差分信號。。。。

2012-11-28 14:48:55

分對組成。我選擇其中一個并在AB7引腳上設置輸出。我收到的信號不是差分信號,而是單端信號。我該怎么做才能產生差分信號?

2020-08-07 06:27:32

您好。如果您方便請加我QQ。我們有6路0-5V的模擬信號,想通過一款芯片轉為差分信號,再通過AD采集卡采集,請問有合適的產品推薦嗎?附件是我們采集卡的資料。另外請問“全差分放大器”是什么?我們這里的設計需要考慮嗎?附件AD芯片參數.png196.5 KB

2018-08-24 07:37:34

本系統實現了在以TI公司的TMS320DM643為核心的嵌入式系統中,對數字電視傳輸流(TS)信號進行采集并在以太網中傳輸。利用本系統可輕松地實現在局域網中對數字電視傳輸流信號的傳輸、調度。數字電視

2019-10-24 07:43:21

“原始的輸入信號經過倒相器和緩沖器之后形成一對大小相等而極性相反的差分信號。對模擬信號,倒相器可以用運算放大器的反相比例放大電路來實現,緩沖器可以用運算放大器的同相跟隨電路來實現。對數字信號,可以

2012-11-16 19:59:22

的,為啥說差不多呢,后面再詳細說。差分信號指的是用兩根線傳輸的信號,傳輸的是兩根信號之間的電平差。當你把信號從A點傳遞到B點的時候,A點和B點的地電勢可以一樣也可以不一樣,但是A點和B點的地電勢差有一個

2017-03-02 10:58:00

描述全差分運算放大器(Rev. A for TEST!)用于測試差分信號的CMRR。PCB

2022-08-08 07:30:58

分信號對于數字和模擬信號都可以定義。 一個差分信號是用一個數值來表示兩個物理量之間的差異。從嚴格意義上來講,所有電壓信號都是差分的,因為一個電壓只能是相對于另一個電壓而言的。在某些系統里,系統

2019-05-29 07:19:25

是一樣的,為啥說差不多呢,后面再詳細說。差分信號指的是用兩根線傳輸的信號,傳輸的是兩根信號之間的電平差。當你把信號從A點傳遞到B點的時候,A點和B點的地電勢可以一樣也可以不一樣,但是A點和B點的地電勢差

2017-11-19 13:45:25

對處于惡劣環境中的外部接口需要予以電流隔離,以增強安全性、功能性或是抗擾能力。這包括工業測量和控制所用數據采集模塊當中的模擬前端,以及處理節點之間的數字接口。低壓差分信號傳輸(LVDS)是一種在更高

2019-07-23 07:27:54

由于差分信號在一組特定電源電壓下使用較大信號,提高了對共模噪聲的抑制能力,降低了二次諧波失真,因而實現了更高的信噪比。由于這一需求,我們需要可將大多數信號鏈中的單端信號轉換為差分信號的電路模塊。

2021-04-09 06:56:19

請問,ad7626數據手冊顯示,只有cnv信號支持單端,而clk不支持單端工作?因為目前fpga配置出現問題,不能提供clk、cnv的差分信號。

2018-09-10 11:02:55

親愛的先生我嘗試在Artix-7 FPGA之間進行像LVDS這樣的DDR差分信號傳輸。但是我不能在Artix-7中使用SelectIO IP。有人能告訴我示例設計嗎?謝謝。

2020-08-18 09:34:09

你知道什么是差分信號嗎?一個差分信號是用一個數值來表示兩個物理量之間的差異。從嚴格意義上來講,所有電壓信號都是差分的,因為一個電壓只能是相對于另一個電壓而言的。在某些系統里,系統'地'被用作電壓

2016-08-19 12:35:47

針對遙感系統的工作環境特點、待處理信號的頻譜特征以及系統信噪比等要求,綜合比較多種信號采集系統方案的優缺點,本文提出了一種基于FPGA的激光多普勒測振計信號采集與處理系統的設計方案,該方案可以實現光

2019-06-24 07:16:30

摘要:在某綜合控制計算機系統中為了實現對多路AD信號實時高精度采集,采用了以TMS320C6713B為核心,與AD7656芯片相組合的高精度、實時A/D數據采集砹計實現方案。重點分析硬件接口電路

2019-06-19 05:00:06

本節繼續講解PCB設計中差分信號的規則設置。差分信號的規則可以在電氣規則下面建立,也可以在物理規則下面建立;電氣規則下建立的差分信號規則是全局性的,不受區域規則的約束,在BGA等需要密集出線的地方

2017-08-15 10:27:49

根據電力監控系統的要求,提出一種基于FPGA技術的多路交流信號采集與處理系統的設計方法。分析整個系統的結構,并討論FPGA內部硬件資源的劃分和軟件的設計方案,以及各個功能

2009-05-16 14:47:58 27

27 本文介紹了一種基于FPGA 的高速多路數據采集系統的設計方案,描述了系統的主要組成及FPGA 的實現方法。在硬件上FPGA 采用ACEX1K100 器件,用于實現A/D 轉換器的控制電路、多路

2009-12-19 16:02:33 50

50 為了節約PCB板空間,充分靈活利用FPGA內部資源,對FPGA內置差分信號匹配終端進行研究。根據差分信號阻抗匹配的基礎理論,在自制的PCB電路板上利用差分信號線傳遞時鐘和圖像數據

2011-01-04 17:07:13 40

40 本文提供的方式有效地解決了這個問題,既簡化了前端信號調理電路的復雜度,又充分利用了A/D轉換器的輸入電壓動態范圍和量化位數優勢,實現了對多路模擬信號的自適應采集,對其他信號采集系統也具有一定的借鑒意義。

2011-01-14 23:27:55 1366

1366

摘要:本文介紹了一種基于TMS320VC5416的多路加速采集與處理系統的設計方法。該系統采用AD73360作為數據采集前端,通過DSP的MCBSP和AD73360級聯,可實現多路模擬加速信號的實時采集和處理。 關鍵詞:TMS320VC5416;AD73360;加速度;數據處理

2011-03-02 00:03:32 107

107 研究了能夠同時對多路 光電編碼器 脈沖信號進行細分、計數以及傳輸的數據采集處理系統。提出了以高度集成的FPGA芯片為核心的設計方式,實現6路光電編碼器信號的同步實時處理。坐

2011-08-18 16:33:15 90

90 本課題基于關節臂式坐標測量機的研制需要,研究了 光柵傳感器 輸出信號的特點和FPGA開發技術,以FPGA為載體,設計了一個基于FPGA的多路光柵數據采集系統。 本文主要介紹了光柵傳感

2011-08-18 16:34:55 78

78 本文提出的基于FPGA的空間電場信號采集系統應用于探空火箭有效載荷——箭載電場儀探頭后端信號采集與處理部分,也可以為地面電場儀處理電場信號提供服務。該方案解決了電場信號

2012-12-27 11:39:42 3342

3342 基于TMS320LF2407的電力暫態信號采集系統

2016-05-06 16:43:39 9

9 于FPGA的高速多路數據采集系統的設計。

2016-05-10 13:45:28 41

41 基于FPGA的多路數據實時采集與傳輸系統_馮希辰

2017-01-08 10:30:29 3

3 針對機械設備運行中的振動監控,設計振動信號采集系統,提出了一種基于FPGA的振動信號采集系統的設計方案。重點闡述了系統硬件結構組成、信號調理電路和數據采集模塊的設計,同時對A/D采樣的控制邏輯進行了討論。經試驗驗證表明,該系統可達到采樣率10 K每秒、采集精度16位,能夠滿足實時性和精度要求。

2017-11-17 11:04:38 5990

5990

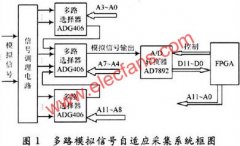

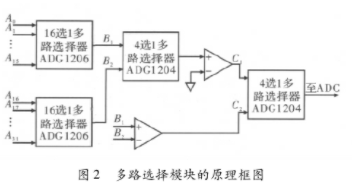

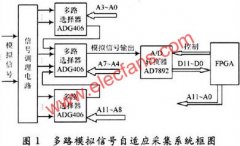

為了實現對58路模擬信號進行不同頻率的采集,設計了一種以現場可編程門陣列(FPGA)為核心的多路模擬信號采集模塊。該模塊采用FPGA芯片XC2S30作為系統的核心控制器件來實現對A/D轉換器的控制

2018-10-12 16:15:21 24

24 設計了一種基于 TI DSP TMS320C6713B 和ALtera Cyclone 系列FPGA 的數據采集模塊,使用FPGA 做多路串行AD 器件的信號采集控制和數據緩沖,同時利用DSP

2019-03-05 16:30:29 16

16 提出了一種基于FPGA+ARM的多路視頻采集系統的設計與實現方法。該視頻采集系統不僅能對多路快速變化的視頻信號進行采集和處理,而且能應用為系統信號發生設備.系統采用FPGA為核心高速時序邏輯控制

2019-11-19 15:51:42 21

21 主要介紹基于FPGA實現多路模擬信號自適應采集系統的設計。該系統主要包括軟件和硬件兩部分:硬件主要采用FPGA芯片,AD7982—1,ADG406和運放AD824來搭建硬件平臺;軟件包括FPGA程序

2021-02-02 15:52:34 5

5

電子發燒友App

電子發燒友App

評論