二次雷達(Secondary Surveillance Radar,SSR)目標識別系統能夠通過發射特定的射頻脈沖序列對裝有應答機的目標進行“一問一答”式的詢問,由應答機的應答脈沖碼獲得目標的高度、編號等信息。航管二次雷達常用的基本工作模式為傳統的A/C模式和新近的S模式。

A模式提供飛機的代碼,C模式提供飛機的高度碼。但是,傳統的A/C 模式存在一些技術缺陷,如多目標代碼交織、重疊、多徑反射,同步竄擾,異步干擾等。這在大型航空港等飛機非常密集的地方,時間不同步和混淆信號已經越來越嚴重,同時單脈沖二次雷達無法提供數據鏈路的服務。

針對上述情況出現了一種新式的二次雷達--S模式二次雷達。S模式是一種先進的雷達詢問系統,它建立在獨立編址和選擇性詢問的基礎上,能夠解決在模式A/C中具有的信號干擾、有限的信息編碼、幻影(garble)和異步應答(fruit)等問題,同時在數據鏈路方面也具有巨大的潛力。

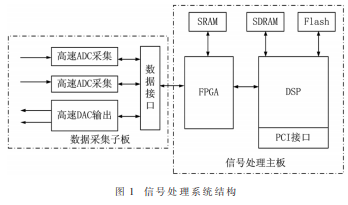

本文采用通行的FPGA+DSP 結構,結構簡單清晰,功能強大,成本相對較低,實現了3/A、C、二級S模式碼發射;接收并處理三路射頻信號,檢測并正確提取AC碼、S碼及相應參數,;輸出航管的A模式,C模式和S模式編碼信號,并有較強的抗干擾能力。

1 二次雷達處理機基本性能要求

二次雷達指標為:工作模式3/A、二級S模式功能,處理能力≥10 000 點/幀,同時≥900 批/幀。抗異步串擾密度10 000 fruits/s;檢測概率≥99%,虛警率1個/幀,解碼有效率≥99%;具有接收旁瓣抑制和詢問旁瓣抑制能力,可自適應反串擾和他站應答干擾;具有抑制反射假目標的能力。

根據上面基本要求,二次雷達可以按任務分解為:

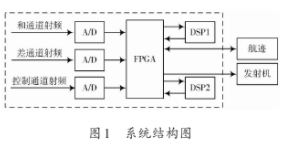

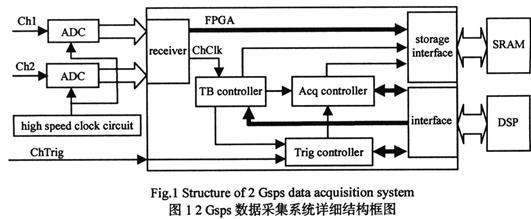

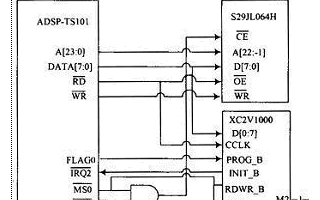

解碼、發射時序、點跡處理、通信四種功能。相對而言,FPGA易于處理大數據量的流水數據,不適于復雜算法的事務處理,開發調試困難。DSP功能強大、運算速度快、尋址靈活、通信能力強,易于開發;但有些功能僅DSP 無法完成,必須有FPGA 配合。這就要在FPGA 和DSP 之間合理分配任務。因此這里除了點跡由DSP 處理外,其他都由FPGA來完成。系統結構如圖1所示。

FPGA完成三通道采樣、下變頻、AC碼、S碼檢測提取,兩片DSP 分別完成AC 碼、S 碼點跡處理。FPGA 同時完成與航跡管理機雙向通信,及控制發射機的發射時序。

系統接口一般有FIFO和雙口RAM,前者適于順序事務處理,但速度慢,而且需要加同步頭,不適于DMA處理。這里全部采用FPGA內部的雙口RAM,并且置為乒乓結構,這樣可利用DMA 高速處理大量數據。同時為了加快處理速度,DSP外總線全部采用同步方式。

根據性能要求,為了同時裝配4路AC碼,專門設計了接口同時捕獲4路信號,并順序處理捕獲的信號。

2 系統軟件流程及功能

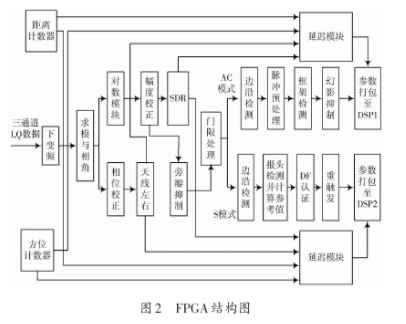

從系統的性能及硬件結構可以看出,FPGA的任務相當復雜,要完成解碼、發射及相應的通信功能。解碼框圖如圖2所示,基本過程是下變頻,幅度、相位校正,門限處理,再分別AC通道和S通道處理。

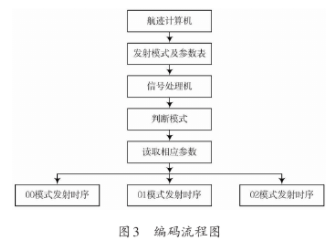

FPGA除了完成解碼、還要完成編碼和時序控制功能,編碼框圖如3所示。由于航跡管理機有空中飛機的歷史航跡,因此發射模式是由航跡管理機來配置的。航跡管理機根據歷史航跡來確定某一方位的詢問是全呼叫還是點名,并確定回答概率等參數。然后并將這些參數傳入發射模式表。編解碼根據方位讀取相應參數,并產生相應編碼脈沖。

2.1 編碼主要系統軟件流程及功能

2.1.1 下變頻模塊

二次雷達要求和、差、控制三通道同步,因此系統中頻放到了信號處理機,這樣便于同步。系統中頻是60 MHz,采樣80 MHz,采樣后,必須濾波并抽取。下變頻一般用DDS模塊,但DDS占用資源較大,這里I,Q通道各自只用了4個預置值。一般預置值I通道采用[1,0,-1,0],Q通道采用[0,1,0,-1]。但這樣遇到采樣值是[1,0,-1,0]或[0,1,0,-1]時,一個通道輸出是0.因此這里采用[ 2 2, - 2 2, - 2 2, 2 2],[ 2 2,2 2, - 2 2, - 2 2],這樣保證每一個通道都有輸出值。但這樣做會擴大了數據位數,直接截位會影響小信號檢測。為了不影響小信號處理,必須在抽取濾波時加大數據位數,最后再截位處理。

2.1.2 求模與相角

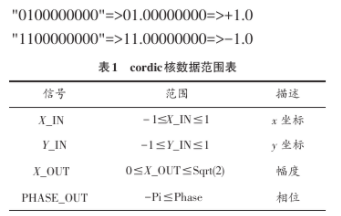

求模與相角采用cordic核,這樣將I,Q數據轉化為模與相角。表1 是cordic 核數據范圍表,輸入的I,Q的范圍是[-1,1]。在cordic 核中模與相角分別采用1QN、2QN 表示形式,例如在幅度是用1QN 表示的。假設cordic 核的數據長度是10 位,即幅度用1Q8 表示中,因此1和-1表示為:

同時來自AD的I,Q數據也是用補碼表示的。假定AD 數據長度也是10 位,那么正數最大是29-1,即0111111111.這樣就超過了cordic核的表示范圍,因此cordic核的位數必須正確設置才能不損失動態范圍。并且相位的范圍是[-π,π],補償后相位必須歸算到[-π,π]。

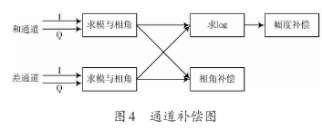

2.1.3 幅度與相角補償

一般通道校正可以在射頻補償,也可在I,Q通道補償,但都是復數乘法補償,必然有舍入損失。這里插入了log模塊,將乘法簡化為加法,因此直接在求模與相角后補償相角,并在求log后補償幅度。這樣將乘性誤差轉化為加性誤差,補償精度比直接在I,Q通道補償高很多,如圖4所示。

2.1.4 AC通道處理

AC通道在邊沿檢測、脈沖預處理、框架檢測后提取AC碼參數,并且進行去除幻影處理。幻影框架是因為不同框架脈沖交疊在一起,產生多個虛假的框架,從而產生多個虛假的應答,必須去除。

單脈沖二次雷達目標信號處理去除幻影的基本思路是利用單脈沖二次雷達和、差通道的信號幅度信息來去除幻影框架。屬于同一框架脈沖的AMP 值應具有一致性,不具有AMP 一致性的兩個脈沖很可能屬于不同的框架。并且通過以下步驟去除幻影:

(1)可能的幻影框架判定

根據完全重疊的定義,對所有收到框架中的F1和F2脈沖進行完全重疊判定。通過判斷該F1,F2脈沖是否在另一個框架的F1后n ×29±3( n = 0,1,…,14)的位置上(系統時鐘選20 MHz)。即計算兩個脈沖的距離值差,如果等于n ×29±3(n = 0,1,…,14),即為可能的幻影框架。

(2)構成交疊關系的框架

根據構成交疊關系的框架的定義,對于上步找到的n 個可能的幻影框架,找出與每個框架Ai(1≤ i n )構成交疊關系的所有框架,即計算兩個框架的距離值差,如果等于n ×29±3( n =0,1,…,14),就是構成交疊關系的框架,假定有m 個構成交疊的框架。

(3)去除幻影

根據判定幻影框架充分必要條件中的Σ,Δ值均具有一致性的原則,分別計算出每一個可能幻影框架Ai(1≤ i ≤ n )的參考信號的Σ 值,跟每個與之構成交疊關系的框架Bi((1≤ i ≤ m )的參考信號的Σ 值之差,同時也計算出兩者的Δ 值之差。只要其中有一組的Σ 值之差具有一致性,且Δ 值之差也具有一致性,就將該框架作為幻影刪除。

這里去幻影是流水處理,為了處理方便將此算法放在FPGA內處理。

2.1.5 S通道處理

S通道經過邊沿檢測,報頭檢測,計算參考值,DF認證,重觸發,參數提取模塊完成S模式應答信號的檢測與提取[6-7]。

S 模式信號報頭為8 μs,并且數據可長達112 μs,提取電路相對復雜。這里采用移位寄存器來提取碼值。即檢測到有效報頭后,等數據脈沖部分到來后,再啟動數據提取,將數據逐次打入。

2.2 編碼主要流程及功能

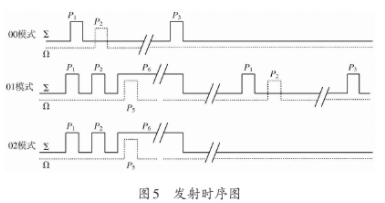

信號處理機還須進行編碼發射時序處理,發射時序如圖5 所示。根據圖3 流程,航跡計算機來配置每一SCAN 的發射模式及參數表。信號處理機來順序讀取每個脈沖的模式及相應參數,并據此來控制發射波形。

這里模式僅分為三種,分別是00、01、02.如圖5所示,00 模式是AC 模式,即AC 交替模式,用于發射AC碼。01 模式是S 和AC 聯合全呼叫模式,這樣裝有S 模式和只裝AC 模式的飛機都能應答。02 模式是點名呼叫模式,這樣地址一致的S模式飛機才響應并應答。

2.3 點跡處理

信號處理機同時完成點跡處理,即將飛機的多個應答處理為一個點跡報告,并傳送到航跡計算機,這部分任務由DSP完成。

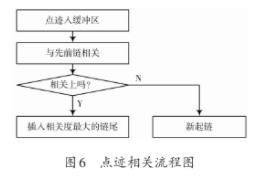

點跡處理處理分點跡相關和點跡凝聚的兩個過程。其中點跡相關的基本流程如圖6所示。

相關上的點跡形成一個鏈,碼值的凝聚則根據鏈上所有應答的置信度來凝聚碼值,生成距離、方位、點跡質量、緊急/識別標注等,然后生成點跡報告送至航跡計算機。

3 結論

本系統采用FPGA+DSP的方式設計、實現了單脈沖二次監視雷達實時信號處理機,結構清晰簡單,功能強大,成本相對較低。經測試SSR信號處理機,可以達到≤15 m級的距離分辨率。并且根據二次雷達設備規范[8],每個SCAN 可以達到約600個目標,或每個扇區可處理64批目標,檢測概率大于99%,測角精度優于0.05°。同時系統有BIT 功能,可以離線或在線檢測,可靠性很高。另外,系統簡單擴展既可以實現1、2、B、D、IFF等功能。綜上所述,本二次雷達信號處理機具有較高的性價比,市場前景廣闊。

責任編輯:gt

電子發燒友App

電子發燒友App

評論