飛思卡爾半導體QorIQ通信處理器多年來一直作為業界通信處理器的主力軍,為應對信息大爆炸和物聯網的發展,QorIQ也在不斷革新。本文詳解QorIQ T1040和T1042通信處理器內部架構,并展示其如何應對物聯網浪潮的侵襲...

2013-11-26 10:13:12 3782

3782

本系統采用基于FPGA與DSP協同工作進行視頻處理的方案,實現視頻采集、處理到傳輸的整個過程。

2014-10-23 15:35:49 6040

6040

DSP+FPGA架構的最大特點是結構靈活、有較強的通用性、適合于模塊化設計,從而能夠提高算法效率,同時其開發周期短、系統易于維護和升級,適合于實時視頻圖像處理。

2015-02-03 15:20:47 1166

1166

于電子產品,并且在技術方面要始終處于領先地位。根據TechNavio公司的全球測試與測量設備市場2011-2015年報告,測試與測量設備廠商正在朝著最小化方向而努力。最小化將會在盡可能提高便攜性的同時

2018-09-03 15:02:35

DSP處理器與通用處理器的比較1 對密集的乘法運算的支持GPP不是設計來做密集乘法任務的,即使是一些現代的GPP,也要求多個指令周期來做一次乘法。而DSP處理器使用專門的硬件來實現單周期乘法。DSP

2021-09-03 08:12:55

和DSP走向融合。DSP和FPGA都在利用自身的優勢開發新的產品,以滿足新應用的需求。在一些復雜的應用中,由于需要兼顧硬件連接、處理效率、軟件兼容性和開發難度等各方面因素,FPGA加DSP和其他處理器

2019-06-27 07:06:16

現狀是:1.信號處理板的架構是FPGA+DSP,DSP上掛網口,與電腦可正常通信2.數據處理板的架構是FPGA掛網口,與電腦可正常通信現在問題:兩塊板子網口無法正常通信,且拔插網口后不能自啟動。聯系方式:shang_lg2011@163.com/***尚

2020-05-27 08:28:44

DSP無線通信處理培訓班邀請函課程簡介:您將在這個為期 3 天的DSP培訓課程中學到 DSP設計的技巧和竅門。 此DSP培訓課程涉及的芯片涵蓋了兩大廠商的主流芯片TI c6000和 ADI

2012-09-06 10:55:46

本人剛入門FPGA,不知道如何實現FPGA+DSP,FPGA+ARM接口設計,網上查詢有的說FPGA+DSP可以通過EMIF,IP核實現,FPGA+ARM可以通過SPI,有沒有具體硬件參考的?

2016-08-27 11:30:26

.FPGA+DSP的導引頭信號處理結構成為當前以及未來一段時間的主流。FPGA和DSP處理器具有截然不同的架構,在一種器件上非常有效的算法.在另一種器件上可能效率會非常低。如果目標要求大量的并行處理或者最大

2019-08-30 06:31:29

FPGA實現高速FFT處理器的設計介紹了采用Xilinx公司的Virtex - II系列FPGA設計高速FFT處理器的實現方法及技巧。充分利用Virtex - II芯片的硬件資源,減少復雜邏輯,采用

2012-08-12 11:49:01

和比較,并給出了FPGA與這兩種DSP芯片進行鏈路口通倍的具體方法。在FPGA內部實現了DSP鏈路口的設計,同時給出了DSP進行鏈路口通信的具體設置方法。由于實時處理中數據的重發會嚴重影響處理的實時性

2019-06-19 05:00:08

和比較,并給出了FPGA與這兩種DSP芯片進行鏈路口通倍的具體方法。在FPGA內部實現了DSP鏈路口的設計,同時給出了DSP進行鏈路口通信的具體設置方法。由于實時處理中數據的重發會嚴重影響處理的實時性,故

2018-12-04 10:39:29

、課程介紹在通信和圖像處理應用中,需要強大的數字信號處理(Digital Signal Processing,DSP)能力。當最快的數字信號處理器(DSP)仍無法達到速度要求時,其選擇除了增加處理器

2009-07-21 09:22:42

驗證 基于FPGA的片上可編程系統(SOPC)設計 FPGA系統設計原則和技巧 利用FPGA實現外設通信接口 FPGA與DSP協同處理系統設計 數字圖像倍焦系統設計與實現綜合實例 高速

2012-02-09 15:45:32

領域通常是高速網絡處理器(NP)+FPGA的典型架構。 (3)4G等通信設備,對于新一代通信基站的信號處理,FPGA+DSP陣列的架構就是絕配。特別是在專用處理芯片面世之前,這樣的架構可以保證新一代通信

2018-08-06 11:45:27

最小化SEPIC轉換器的排放

2021-03-09 06:15:04

本帖最后由 lrb0730 于 2017-3-21 11:33 編輯

LabVIEW的vi在運行時如何最小化到系統通知欄,不知道怎么實現?

2017-03-21 10:59:05

現狀是:1.信號處理板的架構是FPGA+DSP,DSP上掛網口,與電腦可正常通信2.數據處理板的架構是FPGA掛網口,與電腦可正常通信現在問題:兩塊板子網口無法正常通信?

2020-05-27 08:43:57

處理器的數目之外,就是采用可編程邏輯器件,主要是FPGA芯片來實現。本課程以DSP設計在FPGA芯片上的開發為主線,遵照由淺入深的基本步驟和思路進行詳細講解,每一個知識點都給出了基于ISE(HDL語言

2009-07-21 09:20:11

分享VI程序 代碼名稱:LabVIEW實現窗口最大化和最小化 適用平臺:LabVIEW8.2.x LabVIEW8.5代碼作者:LaRisa_S 版權所有:LaRisa_S 原創/轉載:轉載代碼

2013-03-08 14:56:15

,界面輸入外設操作等操作,FPGA負責大數據量運算,可以看做CPU的專用協處理器來使用,也常會用于擴展外部接口。常用的有ARM+FPGA,DSP+FPGA,或者網絡處理器+FPGA等種種架構形式,這些架構

2017-06-07 13:12:54

處理器的數目之外,就是采用可編程邏輯器件,主要是FPGA芯片來實現。本課程以DSP設計在FPGA芯片上的開發為主線,遵照由淺入深的基本步驟和思路進行詳細講解,每一個知識點都給出了基于ISE(HDL語言

2009-07-24 13:07:08

好的浮點數參數數據進行補償運算,消除零偏及溫漂。這其中要用到一定量的浮點運算,原本計劃采用FPGA+DSP的架構,但板子面積有限。以前用過斯巴達3系列芯片的核,故決定浮點運算部分采用軟核來實現,可以省掉一片DSP。

2016-10-12 09:52:40

FPGA進行硬件實現,這樣能兼顧速度及靈活性。高層的處理算法結構復雜,適用于運算速度高、尋址方式靈活、通信機制強的DSP芯片宋實現。DSP+FPGA架構的最大特點是結構靈活、有較強的通用性、適合于模塊化

2019-07-01 07:38:06

串口通信處理數據的思路是什么

2022-02-18 07:52:58

代碼加速和代碼轉換到硬件協處理器的方法如何采用FPGA協處理器實現算法加速?

2021-04-13 06:39:25

乘法器、乘加器、乘累加器,并運用在絕大多數DSP算法上。顯然,這里的DSP塊,只是一個可配置的乘加單元,并非前面所說的DSP處理器。其實FPGA內部并沒有DSP處理器。五、STM32中的DSP是什么東西

2020-09-04 10:31:13

/13通信處理器就是眾多新品之一,這些新處理器采用28 nm技術,將性能領先的Power Architecture e5500處理器內核與運行頻率高達1.4 GHz的先進緩存架構、應用領先的卸載引擎和面

2019-07-30 06:47:33

,數字信號處理與數字圖像處理沒有太大區別),就意味著可以用FPGA做硬件設計來實現DSP芯片的功能,當然,相比較專業的DSP芯片 成本太高,因此你也沒必要選擇FPGA+DSP,就選擇DSP芯片,算法...

2021-07-28 09:16:02

的重點是以DSP+FPGA為核心的視頻處理模塊的設計與實現,可以完成多路視頻的切換選擇輸出控制和視頻縮放顯示的功能,同時具備通信控制等功能。

2019-06-20 06:34:25

基于DSP的圖像處理系統的應用研究摘要 本文介紹了一種基于FPGA+DSP結構的具有通用性、可擴充性的高速數字圖像處理系統硬件平臺。重點介紹了以高速數字信號處理器TMS320DM642

2012-12-19 11:05:08

的軟件,變得更加重要。為滿足需求,文中提出一種基于DSP/ BIOS的軟件架構,可提高軟件的可維護性和可重用性,方便算法的裁減添加及程序的跨平臺移植,實現多類信號多路并行處理的軟件快速開發設計。1 DSP

2012-09-03 17:18:51

用FPGA進行硬件實現,這樣能兼顧速度及靈活性。高層的處理算法結構復雜,適用于運算速度高、尋址方式靈活、通信機制強的DSP芯片宋實現。 DSP+FPGA架構的最大特點是結構靈活、有較強的通用性

2019-06-28 08:10:26

圖像數據處理的工作原理是什么?基于FPGA+DSP的圖像處理系統待如何去設計?

2021-06-02 06:54:28

基于FPGA+DSP的高速數據采集系統設計

2012-06-27 17:23:53

用FPGA進行硬件實現,這樣能兼顧速度及靈活性。高層的處理算法結構復雜,適用于運算速度高、尋址方式靈活、通信機制強的DSP芯片宋實現。 DSP+FPGA架構的最大特點是結構靈活、有較強的通用性

2019-06-19 06:12:05

信號,調制無線信號以便實現同通信網絡系統前端基站的無線通信。文章設計了一種基于先進微處理器(ARM)、數字信號處理(DSP)和現場可編程門陣列(FPGA)體系結構的3G移動終端基帶信號處理器。這種

2019-07-03 06:18:48

TMS320C6657處理器,FPGA端采用Xilinx Artix-7處理器,實現異構多核處理器架構,DSP與FPGA內部通過uPP、EMIF16、SRIO連接;底板接口資源豐富,支持uPP

2018-10-31 14:27:30

如何實現在Linux操作系統下ARM體系結構的處理器與DSP的數據通信?

2021-05-28 06:11:36

減小動態和靜態功耗的方法有哪些?如何使FPGA設計中的功耗最小化?

2021-05-08 07:54:07

,生命周期縮短。實現功能強、性能指標高、抗干擾能力強、工作穩定可靠、體積小、功耗低、結構緊湊合理符合彈載要求的導引頭信號處理器已經勢在必行。過去單一采用DSP處理器搭建信號處理器已經不能滿足要求.FPGA+DSP的導引頭信號處理結構成為當前以及未來一段時間的主流。

2019-11-06 08:34:27

我想使用 STM32F7 通過 SPI 從外部 ADC 檢索 ADC 測量值(16 位讀取操作以檢索測量值)。理論上應該是可以的。我的問題是:如何檢索最小化主機處理器負載的測量值?我的想法

2022-12-22 08:30:25

,生命周期縮短。實現功能強、性能指標高、抗干擾能力強、工作穩定可靠、體積小、功耗低、結構緊湊合理符合彈載要求的導引頭信號處理器已經勢在必行。過去單一采用DSP處理器搭建信號處理器已經不能滿足要求.FPGA+DSP的導引頭信號處理結構成為當前以及未來一段時間的主流。

2019-08-19 06:38:12

自己做了一個小秒表,想最小化到托盤,怎樣實現!求助!

2014-03-14 22:44:03

雖說FPGA+DSP的數字硬件系統正好結合了兩者的優點,但有什么方法去證明FPGA+DSP系統中FPGA的關鍵技術是存在的呢?

2021-04-08 06:54:33

我想用FPGA+DSP做個聲相儀,有感興趣的小伙伴嗎?一起開發,在上海最好啦。先做原型機出來,然后再考慮產品化。私聊:QQ 4010087

2017-04-25 14:53:48

想用自己設置的最小化,但是找不到這個函數,不知道這個函數是否存在,請有經驗的幫忙提個醒。

2013-07-26 09:01:43

P1014-RDB,QorIQ P1014參考設計板,用于具有信任架構的P1014低功耗通信處理器。 P1014 RDB是一款高度集成的參考設計板,可幫助縮短產品上市時間。該參考設計針對低成本網絡應用(有或沒有信任架構),有線和無線接入,工業和智能能源應用

2019-04-18 09:28:52

蘇州上門大量求購全新CP443-1通信處理器卡件/回收西門子通信處理器、6GK7 243-2AX01-0XA0、6GK7 443-1EX30-0XE0、6GK7 343-1GX30-0XE0

2021-06-12 20:47:28

,與單獨的數字信號處理器相比,FPGA 技術能夠為高難度的 DSP 問題提供大為簡化的解決方案。要明白其中的緣由,需要回顧一下 DSP 的肇始和發展。用于實現專門目的的微處理器在過去二十年里,傳統

2018-08-15 09:46:21

,最高可提供256 GMAC的DSP性能。將需要高速并行處理的工作卸載給FPGA,而將需要高速串行處理的工作留給處理器,這樣即可在降低系統要求的同時優化整體系統的性價比。

2019-07-15 06:18:56

甚至互聯網公司都推出了極富競爭力的智能路由器,而物聯網時代必將有更多五花八門的智能設備孕育而生,這都離不開強大的智能芯片作為技術支撐,特別是通信處理器。集成的誘惑。可以說從計算機發明開始,人類就在謀求

2019-07-31 07:38:13

描述TIDA-01512 采用 TPS53681 多相控制器和 CSD95490Q5MC 智能功率級,可實現適合為 NXP QorIQ 通信處理器供電的高性能設計。該控制器的雙路輸出分別面向具有四相

2018-10-10 09:18:38

介紹了一種基于FPGA+DSP 的數據采集與處理平臺,給出了系統實現的總體方案,并闡述了各部分硬件電路的設計。重點對FPGA 內部各主要功能模塊做了詳細闡述,對各個模塊的設計方法

2009-12-19 15:59:16 34

34 設計一種基于DSP和FPGA架構的通用圖像處理平臺,運用FPGA實現微處理器接口設計,并對圖像數據進行簡單預處理,利用DSP進行復雜圖像處理算法和邏輯控制,實現圖像數據的高速傳輸

2010-12-25 17:06:54 60

60 QorIQ 通信處理器飛思卡爾

飛思卡爾半導體推出第一款基于其QorIQ 通信平臺,并且融入 QUICC Engine多協議技術的處理器。QorIQ P1012/P1021 產品系列為使用

2009-12-09 09:38:52 658

658 基于DSP和FPGA的通用圖像處理平臺設計

摘要:設計一種基于DSP和FPGA架構的通用圖像處理平臺,運用FPGA實現微處理器接口設計,并對圖像數據進行簡單預處理,利用DSP

2010-02-01 11:10:21 1379

1379

LSI推出的最新Axxia通信處理器

LSI 公司日前宣布推出專為無線基礎設施應用設計的 Axxia™ 系列通信處理器。Axxia 通信處理器采用突破性 LSI™ Virtual Pipeline™ 消

2010-02-22 10:19:07 845

845 LSI推出Axxia 系列通信處理器

LSI 公司宣布推出專為無線基礎設施應用設計的 Axxia 系列通信處理器。Axxia 通信處理器采用突破性 LSI™ Virtual Pipeline™ 消息傳遞技術

2010-02-23 09:30:24 892

892 LSI推出無需外部存儲器的多核通信處理器APP3100

LSI公司日前宣布面向企業及服務提供商推出LSI APP3100多核通信處理器。LSI APP3100基于獲獎的LSI APP3300通信處理器之上,能夠為

2010-04-27 10:08:02 526

526 NetLogic Microsystems,宣布推出創新的XLP8128S多核通信處理器解決方案。該方案集成了128個nxCPUs和160個以上可編程處理引擎,可為下一代3G/4G移動無線基礎設施、企業、存儲、安全

2010-09-11 09:10:57 655

655 摘要:在FPGA+DSP構建的便件平臺上,以鏈路口(LINKPORT)通信協議為根據,實現紅外圖像數據采集與顯示。重點描述紅外圖像數據采集與經過LINKPORT傳入DSP,圖像壓縮與經過LINKPORT傳出DSP以及圖像數據緩存與顯示,最后介紹了程序高度過程中的方法。樣機在實

2011-03-01 00:11:12 87

87 TranSwitch(傳威)公司最新推出的Atlanta 2000通信處理器計算性能登上業界最高峰,可同時處理一千個語音和數據通道,且總的功率損耗只有3W,也即每通道功耗只有3mW

2011-03-25 09:33:23 1027

1027 飛思卡爾半導體在1989年推出業界首款多協議微處理器,確立了通信處理器市場之后,長期位居這一市場的領導地位,其產品線的覆蓋廣度及深度均鮮有競爭者企及。

2011-08-31 09:25:28 829

829 在雷達信號處理、數字圖像處理等領域中,信號處理的實時性至關重要。由于FPGA芯片在大數據量的底層算法處理上的優勢及DSP芯片在復雜算法處理上的優勢,DSP+FPGA的實時信號處理系統

2012-07-05 15:01:40 7272

7272

基于FPGA+DSP實時圖像采集處理系統設計

2017-01-03 11:41:35 9

9 基于FPGA和多DSP的多總線并行處理器設計

2017-10-19 13:40:31 4

4 所處理的數據量少,算法結構復雜,適于運算速度快,尋址靈活的DSP數字信號處理器進行處理。這里提出了一種FPGA+DSP相結合的實時圖像處理系統,并應用于傳像光線束傳遞圖像。CMOS實際采集的是光線束的出端圖像,FPGA將CMOS采集的Bayer格式的

2017-10-26 15:44:56 2

2 摘要 利用異步FIFO實現FPGA與DSP進行數據通信的方案。FPGA在寫時鐘的控制下將數據寫入FIFO,再與DSP進行握手后,DSP通過EMIFA接口將數據讀入。文中給出了異步FIFO的實現

2017-10-30 11:48:44 1

1 所處理的數據量少,算法結構復雜,適于運算速度快,尋址靈活的DSP數字信號處理器進行處理。這里提出了一種FPGA+DSP相結合的實時圖像處理系統,并應用于傳像光線束傳遞圖像。CMOS實際采集的是光線束的出端圖像,FPGA將CMOS采集的Bayer格式的

2017-10-31 17:00:34 12

12 本文主要介紹了一種基于FPGA+DSP的視頻控制的智能交通燈設計。該交通燈由視頻采集、圖像處理和控制模塊組成,使用FPGA核心搭建專用高速視頻采集模塊,使用DSP處理器進行實時圖像運算,通過圖像算法提取車流量信息,最終結合模糊算法實現智能控制。

2018-01-09 14:15:41 1853

1853

FPGA+DSP的數字硬件系統正好結合了兩者的優點,兼顧了速度和靈活性。本文以導引頭信號處理系統為例說明FPGA+DSP系統中FPGA的關鍵技術。

2019-01-08 08:36:00 2449

2449

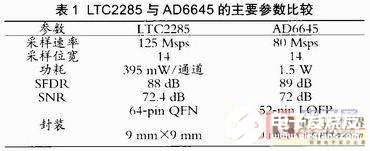

高速中頻采樣信號處理平臺在實際應用中有很大的前景,提出采用FPGA+DSP的處理結構,結合高性能A/D和D/A處理芯片,設計了一個通用處理平臺,并對其主要性能進行了測試。

2018-10-18 16:36:48 4637

4637

大,運算簡單,但是要求運算速率高,可以用FPGA硬件來處理,上層所處理的數據量少,算法結構復雜,適于運算速度快,尋址靈活的DSP數字信號處理器進行處理。這里提出了一種FPGA+DSP相結合的實時圖像處理系統,并應用于傳像光線束傳遞圖像。CMOS實際采集的是光線束

2018-10-22 22:00:01 392

392 C-Port的C-5數字通信處理器(DCP)面向各種通信應用 - 從高功能以太網交換機和多業務接入平臺到太比特路由器和光邊緣交換機。憑借其通用和通信專用處理能力,C-5取代了制造商通常與轉發ASIC

2019-08-13 16:04:12 2289

2289 從模擬制式手機到2G、3G、4G甚至是未來的5G,每到轉折期就有一些人被技術牽絆而不知何去何從,飛思卡爾半導體總是能應景推出相應的通信處理器等創新產品,為通信時代的跨越保駕護航。在物聯網時代,通信處理器

2020-09-29 10:44:00 0

0 PROFIBUS通信處理器(CP)用于將SIMATIC plc連接到PROFIBUS網絡,可以提供S7通信、S5兼容通信(FDL)和PG/OP(編程器/操作員面板)通信,實現SYNC/FREEZE

2021-12-15 10:37:43 740

740 基于FPGA+DSP彈載SAR信號處理系統設計

2021-12-27 18:58:51 21

21 隨著高性能信號處理系統對運算速度、通信速率等要求的不斷提高,單獨的處理器(如FPGA或DSP)無法滿足高速實時信號處理的需求。

2023-02-27 16:27:55 4762

4762

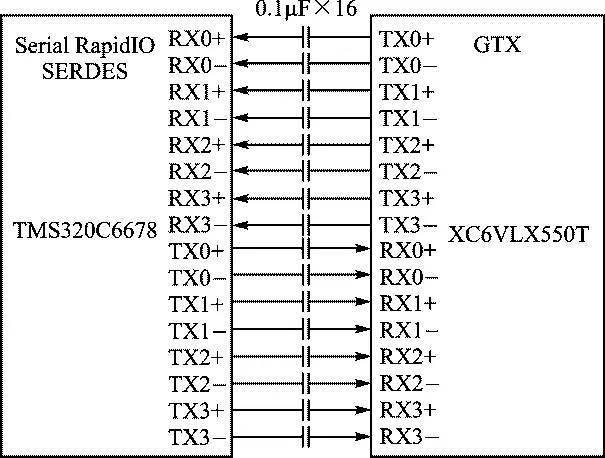

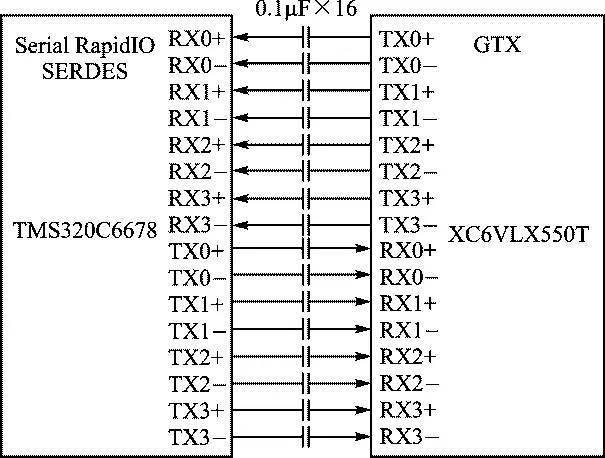

摘要: 現代 信號 處理系統通常需要在不同處理器之間實現高速數據 通信 ,SRIO協議由于高效率、低延時的特性被廣泛使用。本文研究了在 FPGA 和 DSP 兩種處理器之間實現SRIO協議的方法

2023-03-20 15:00:01 1324

1324 電子發燒友網站提供《基于FPGA+DSP模式的智能相機設計.pdf》資料免費下載

2023-10-08 10:37:16 0

0

電子發燒友App

電子發燒友App

評論