隋金雪 1,季永輝 1,2,3,張 霞 2,朱智林 1

(1.山東工商學院 電子與信息工程學院,山東 煙臺 264026;2.北京大學信息技術高等研究院,浙江 杭州 311215;3.煙臺中科網絡技術研究所,山東 煙臺 264026)

摘??要:針對物聯網應用中SOC平臺多需求決策問題,以處理器CV32E40P 和 Ibex 作為內核,選用改進片上總線架構(AMBA)協議以及通用型外設搭建SOC平臺;然后根據資源利用報告分析其面積、功耗和性能;最后在 FPGA上驗證SOC平臺可行性。結果表明,在同一SOC平臺下,CV32E40P的面積相較于Ibex增加了26.07%,在25 MHz、40 MHz與50 MHz頻率下,功耗分別提高了31.58%、29.03%以及25.64%,在運行邏輯控制與卷積運算代碼時,速度分別提高了27.66%和108.75%。綜上,Ibex更適用于智能家居領域中低帶寬數據獲取的場景,而 CV32E40P則適用于智慧城市領域中視頻、圖像數據采集處理的場景。

中圖分類號:TN02?34;TP303? ?文獻標識碼:A

文章編號:1004?373X(2022)03?0039?04

0 引 言

物聯網技術從萌芽導入期到技術沉淀期,再到如今的市場驗證期,被廣泛應用于各行各業,如智能家居、智能工業、智慧城市等。不同應用場景下的物聯網終端設備也被賦予了不同的職能,例如,智能家居中對溫度、濕度、煙霧等低帶寬信息的監控[1],智能工業中對震動、音頻等高頻信號的監控[2],智慧城市中對低功率成像儀、攝像機等高密度信息的監控[3]。為了應對不同應用場景下的多種情況,終端設備除了是完全可編程的,還必須包含必要的硬件設備,從而形成一個完整的系統,如傳感器、執行器、微處理器、無線通信器等,具備完全獨立運行的能力[4]。

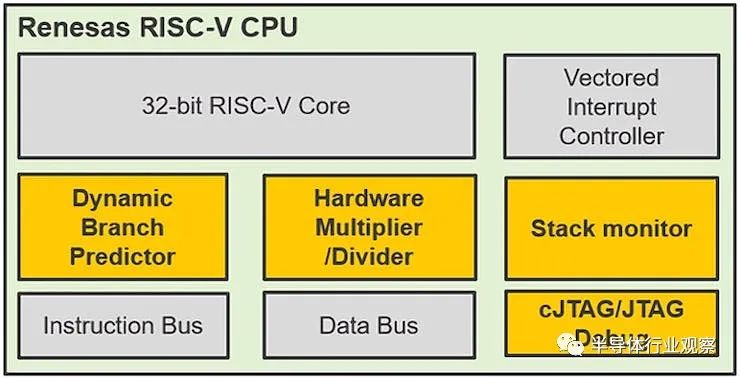

目前,物聯網領域常用的SOC平臺設計方案有三種,分別為單核心SOC平臺、異構SOC平臺以及多核與硬件加速器混合SOC平臺[5]。單核心SOC平臺設計的特點在于其核心針對特定領域優化,例如ARM公司的Cortex?M4平臺以及意法半導體的MSP430平臺[6?7],單核SOC平臺設計在各方面表現都差強人意,但在多任務情況下就略顯不足。異構SOC平臺為解決物聯網領域任務多樣性提供了解決方案,例如意法半導體的CC2650 平臺以及恩智浦的LPC54100平臺[8?9],異構平臺解決了任務多樣性問題,但是在功耗、面積等方面不盡人意。因此,多核與硬件加速器混合的SOC平臺設計方案被提出,例如Fulmine 平臺以及GAP?8平臺[10?11]。混合型SOC平臺雖然在性能與能效方面都很優異,但是專用型硬件加速器限制了平臺的使用,除了特定應用場景下,平臺無法發揮特長。本文采用常見的單核設計,通過討論基于 RISC?V指令集架構的異構性內核,從內核微架構設計到SOC平臺架構設計,分析其功耗、面積、性能等方面的指標,為解決不同應用場景下搭建SOC平臺提供方案。

1 RISC?V 處理器

1.1 CV32E40P處理器

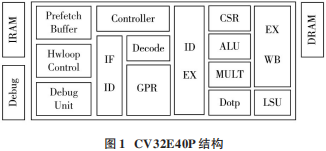

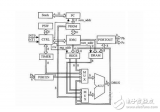

CV32E40P 是一款高效的32位有序RISC?V處理器,具有4級流水線,支持基本整數指令集(I)、壓縮指令集(C)和乘法除法指令集(M),處理器的基本結構如圖1所示。

CV32E40P的流水線分為取指(IF)、譯碼(ID)、執行(EX)、回寫(WB)四個過程。在取指過程中,指令先從存儲器(IRAM)進入對齊預取指緩沖區(Prefetch Buffer)中等待,當指令端存儲系統控制器(Controller)發送確認信號時指令獲取成功,除了獲取指令,取指階段還需要將壓縮指令預解碼成基本整數指令。在譯碼階段,基本整數指令進行更進一步的解碼(Decode)操作,除此之外,該階段還需提前獲取對應的數據放入到普通目的寄存器(GPR)中以便之后使用。在執行階段中存在著三個執行單元,分別是算數邏輯單元(ALU)、乘法器(MULT)和除法器(DIV)。在回寫階段中,計算結果將按照目的操作數寫入對應位置,這里還包含一個加載存儲單元(LSU),用于將數據存儲器中的數據讀取至譯碼階段。

1.2 Ibex處理器

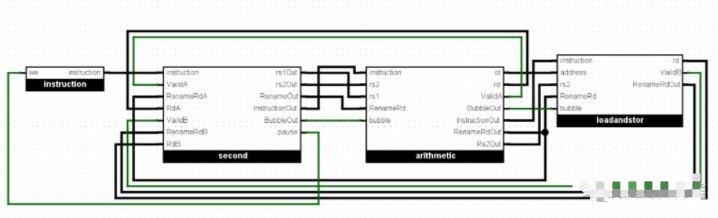

Ibex是一款設計小巧而高效的32位有序RISC?V處理器,具有2級流水線,支持基本整數指令集(I)、壓縮指令集(C),具有可選的乘法除法指令集(M)與比特操作指令集(B),處理器的基本結構如圖2所示。

Ibex的流水線分為取指(IF)、譯碼與執行(ID/EX)兩個階段。在取指階段中,數據從存儲器中進入預取指緩沖區(Prefetch Buffer),當指令端存儲系統控制器(Controller)發送確認信號時,指令便獲取成功。在譯碼與執行階段中,獲取到的指令將被解碼(Decode)并立即執行,普通目的寄存器(GPR)的讀寫也發生在該階段,當遇到多周期指令時,數據通過分支回傳到執行階段的起始位置再次執行直到完成為止。

2 SOC 平臺搭建

2.1 SOC平臺設計

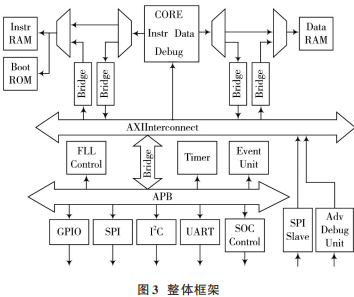

該平臺具有內核、數據存儲器、指令存儲器、事件單元,以及諸如GPIO、UART、I2C、SPI和計時器等通用外設,該SOC平臺如圖 3所示。

由于系統采用哈弗結構,所以具有單端口的32 KB指令存儲器和數據存儲器,且系統包含一個用于引導程序的Boot ROM,能將程序從FLASH中加載并進行初始化。直接掛載到AXI總線上的SPI Slave 接口則能夠讓用戶讀取或寫入內存數據而無需內核幫助,Adv DebugUnit模塊則用于對系統進行調試。

2.2 總線設計

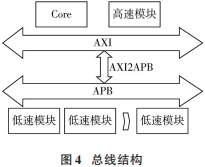

本系統設計采用IP核復用的方式,通過為IP核設定一個共同的總線接口,提高了IP核的可重用性,簡化了芯片的設計工作,為芯片開發節約了大量的時間。本系統采用的總線標準是由ARM公司推出的高級可擴展接口AXI以及高級外設總線APB。相較于內核的數據處理能力而言,外設模塊如UART、GPIO、SPI等的數據吞吐率不高,嚴重影響整個系統的流暢運行,為了解決該問題,本系統將高速模塊通過AXI總線組成高速子系統,將低速模塊通過APB總線組成低速子系統,然后通過AXI2APB橋實現AXI總線與APB總線之間的通信,整個低速子系統作為高速子系統的從機,與其他高速模塊進行通信,因此能夠在一次數據傳輸的過程中與多個低速模塊進行通信,最大化地利用總線資源。本系統采用的總線結構如圖4所示。

3 驗證結果

3.1 面積比較

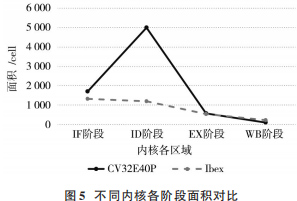

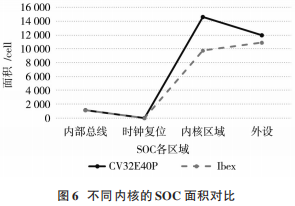

圖5展示了以邏輯單元(Logic Cell)為單位的內核面積分布情況。CV32E40P實例化區域面積為7372單元,Ibex實例化區域面積為3271單元,其中,CV32E40P與Ibex的取值部分面積比為1.28∶1,譯碼部分面積比為4.21∶1,執行部分的面積比為1.06∶1,回寫部分的面積比為1∶1.95。

圖6展示了兩個SOC的面積分布,可以看出除了內核區域外,其余如內部總線模塊、時鐘與復位模塊和外設模塊所占用的面積基本相似。

實驗結果表明,CV32E40P內核相較于Ibex內核在面積上增加了125.37%,CV32E40P SOC平臺相較于Ibex SOC平臺在面積上增加了26.07%,雖然就內核而言,CV32E40P 的面積明顯大于Ibex,但是當嵌入進同一SOC平臺后,面積差異并不明顯。

3.2 功耗比較

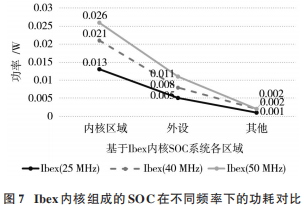

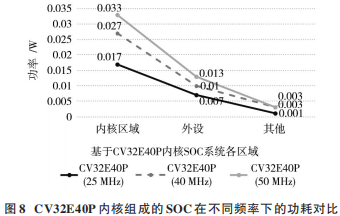

圖7、圖8分別展示了在不同頻率下,由Ibex內核組成的SOC系統與由CV32E40P內核組成的SOC系統在功耗上的性能表現。

結果表明,在相同頻率下,CV32E40P各模塊的功耗明顯大于Ibex各模塊的功耗,隨著頻率的增加,各模塊的功耗也隨之增加,但是CV32E40P功耗增加的幅度要小于Ibex功耗增加的幅度,由此可以說明,CV32E40P相較于Ibex在同頻率下能源利用率更高,即能效更高。因此,在面對需要高算力、高性能的任務時,CV32E40P要比 Ibex更加節能,計算能力也更好,而在面對簡單、無需復雜計算的邏輯控制任務時,Ibex 的整體功耗要明顯優于CV32E40P,性能也完全足夠。

3.3 性能比較

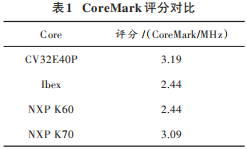

通過表1可以看出,在性能方面,CV32E40P略高于NXP K70芯片 ,而Ibex則對標于 NXP K60芯片 ,CV32E40P僅就跑分而言相較于Ibex提升了 30.74%。

通過Questasim 10.7C仿真軟件對搭建好的SOC平臺進行實驗,在時鐘頻率為25 MHz 下運行邏輯控制代碼,控制串口發送指定字符串,由于CV32E40P具有增強的ISA和更復雜的流水線,因此 CV32E40P 更快地完成 了 數 據 傳 輸 ,CV32E40P相較Ibex速度提升了27.66%。同樣地,在運行卷積運算代碼時,CV32E40P相較Ibex速度提升了 108.75%。

結果表明 ,在處理簡單的邏輯控制代碼時 ,CV32E40P雖然結構更復雜,計算能力更出眾,但是相較于Ibex而言無明顯優勢,但是在針對復雜的卷積代碼進行運算時CV32E40P具有良好的表現,而僅具備簡單乘除運算器的Ibex則捉襟見肘。

4 結 語

本文基于RISC?V指令集架構的異構性內核,提出以RISC?V開源處理器CV32E40P和Ibex作為內核并選用AMBA(Advanced Microcontroller Bus Architecture)協議以及通用型外設搭建SOC平臺的設計方案。由實驗結果可知,面積方面,CV32E40P內核相較于 Ibex內核增加了125.37%,CV32E40P SOC平臺相較于Ibex SOC平臺增加了 26.07%,雖然就內核而言,CV32E40P的面積明顯大了?Ibex,但是當嵌入同一SOC平臺后,面積差異并不明顯。功耗方面,在25 MHz、40 MHz 以及 50 MHz頻率下,CV32E40P SOC平臺的功耗相較?Ibex SOC?平臺的功耗分別增加了31.58%、29.03%以及 25.64%,CV32E40P的功耗要大于Ibex,但是能效比更高。性能方面,CV32E40P的 CoreMark評分相較于Ibex提高了30.74%,在運行邏輯控制與卷積運算代碼時,CV32E40P相較于Ibex速度分別提高了27.66% 和108.75%,CV32E40P更適用于數據運算,而Ibex更適用于邏輯控制。綜上所述,Ibex更適用于智能家居領域低帶寬數據獲取的場景,而CV32E40P則適用于智慧城市領域視頻、圖像數據采集處理的場景。

注:本文通訊作者為季永輝。

參 考 文 獻

[1] HAMAMREH J M,FURQAN H M,ARSLAN H. Classifica?tions and applications of physical layer security techniques forconfidentiality:a comprehensive survey [J]. IEEE communica?tions surveys & tutorials,2019,21(2):1773?1828.

[2] VAKALOUDIS A,O′LEARY C. A framework for rapid integra?tion of IoT systems with industrial environments [C]// 2019IEEE 5th World Forum on Internet of Things(WF?IoT). Limerick,Ireland:IEEE,2019:601?605.

[3] LIU Y,YANG C,JIANG L,et al. Intelligent edge computinfor IoT?based energy management in smart cities [J]. IEEE net?work,2019,33(2):111?117.

[4] WANG J S,XUE C X,LIU C T,et al. A 0.23 V 40 nm OAI?ROM with low active and standby power for AI?based IoT edgedevices [C]// 2020 International Conference on Electronics,In?formation, and Communication (ICEIC). Barcelona, Spain:IEEE,2020:1?4.

[5] KIM N S. A digital intensive extended range dual mode BLE5.0and IEEE 802.15.4 transceiver SoC [J]. IEEE transactions onmicrowave theory and techniques,2020,68(6):2020?2029.

[6] BENATTI S,CASAMASSIMA F,MILOSEVIC B,et al. A versa?tile embedded platform for EMG acquisition and gesture recog?nition [J]. IEEE transactions on biomedical circuits and sys?tems,2015,9(5):620?630.

[7] Texas Instruments. MSP430 ultra ?low ? power sensing & mea?surement MCUs [EB/OL]. [2020?09?11]. https://www.ti.com/mi?crocontrollers/msp430?ultra?low?power?mcus/overview.html.

[8] Texas Instruments. SimpleLink CC2650 wireless MCU Launch?Pad development kit [EB/OL]. [2020 ?09 ?11]. https://www.ti.com/tool/LAUNCHXL?CC2650.

[9] DANIEL G. UM10850 LPC5410x datasheet unclear [EB / OL].[2020 ? 09 ? 13]. https://community.nxp.com/t5/LPC?Microcon?trollers/UM10850?LPC5410x?Datasheet?unclear/m?p/660962.

[10] CONTI F,SCHILLING R,SCHIAVONE P D,et al. An IoTendpoint system ?on ?chip for secure and energy ?efficient near?sensor analytics [J]. IEEE transactions on circuits and systemsⅠ:regular papers,2017,64(9):2481?2494.

[11] Anon. GAP8 hardware reference manual [EB/OL]. [2020?09?18].https://greenwaves?technologies.com/sdk?manuals.

作者簡介:

隋金雪(1977—),男,博士,副教授,碩士研究生導師,主要研究方向為控制理論與控制工程。

季永輝(1995—),男,碩士研究生,主要研究方向為 FPGA 驗證與嵌入式系統。

張?霞(1980—),女,博士,高級工程師,主要研究方向為半導體微電子設計與微電子封裝。

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論