近年來,在服務器和數據中心等企業級市場,AMD憑借持續更新的“Zen”架構,其EPYC(霄龍)系列處理器的市場占有率上升勢頭非常迅猛。2022年11月,AMD推出全新第四代EPYC處理器。新處理器將單插槽處理器核心數量提升到最多96核,并且采用了最新的“Zen 4”架構,帶來大量全新特性。接下來,本文就對第四代EPYC處理器進行詳細解讀。

第四代EPYC處理器:EPYC 9004系列登場

在解析AMD第四代EPYC處理器的架構之前,我們先來梳理一下它的型號定義,因為在這方面它與上代產品存在顯著差異。

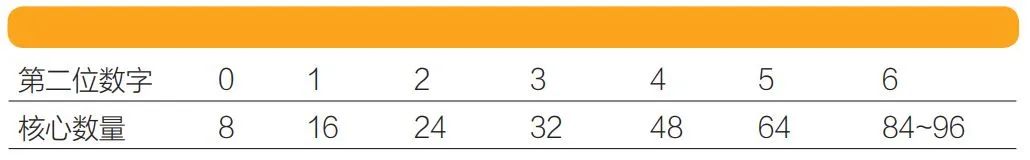

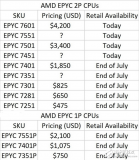

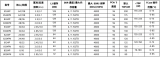

此前,AMD采用EPYC 7000系列作為原始命名。最后一位數代表不同代次,比如EPYC 7001、EPYC 7002和EPYC 7003就分別代表三代不同的產品,其中又包含大量細分型號。在第四代EPYC處理器上,AMD改用了EPYC 9004作為產品基礎代號,這可能是考慮到本代產品具備極為顯著的性能提升。同時,在大多數人的概念中,“9”相比“7”顯得定位更高、性能更強。第二位數字代表處理器核心數量,其基本對應關系如下表:

第三位數字代表性能情況,數字越大則性能越強,目前由2~7的不同數字組成。如果AMD愿意,未來還可能進一步擴展到9。最后一位數字則固定為“4”,代表第四代EPYC處理器。

▲AMD詳細解讀了EPYC 9004產品命名情況

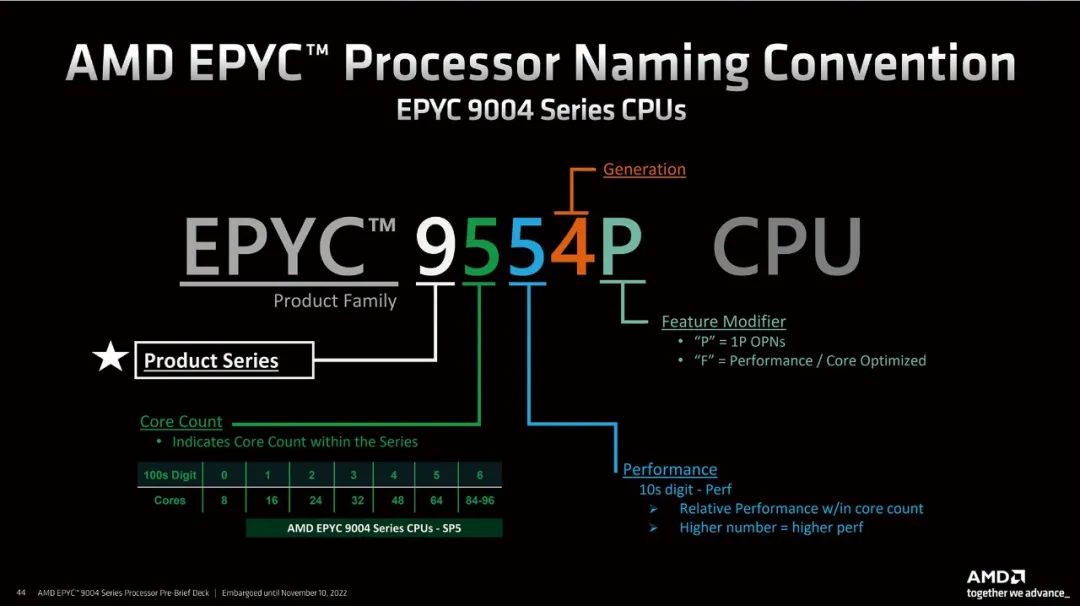

▲AMD將EPYC 9004產品分為了三類:追求核心密度的產品、追求平衡和優化的性能的產品以及追求核心性能的產品。

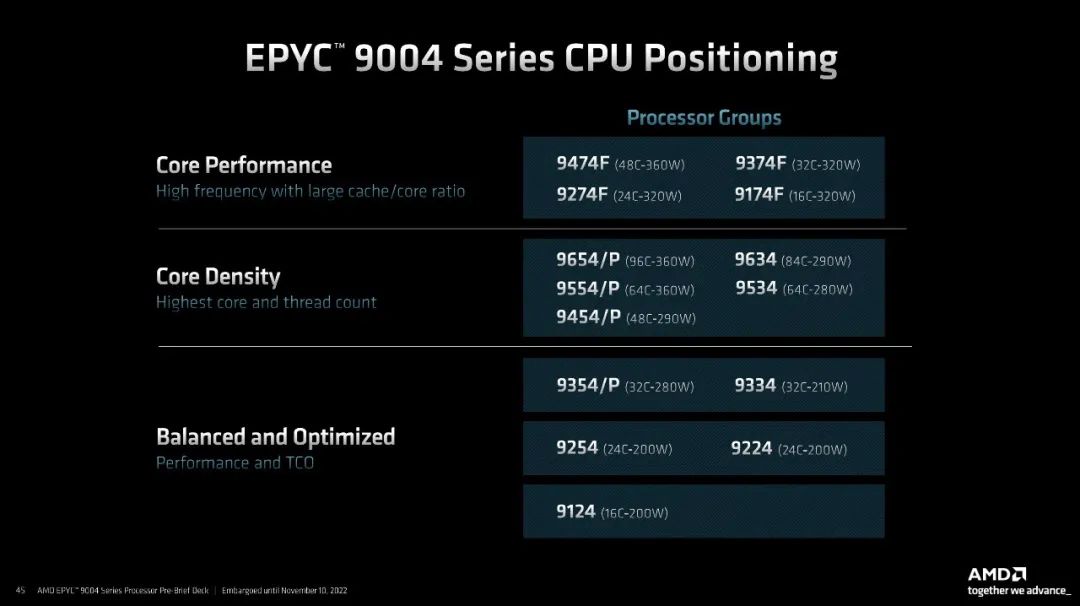

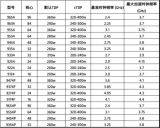

AMD本次發布了18款EPYC 9004系列處理器,分為3個大類,分別是追求核心密度的產品、追求平衡和優化的性能的產品以及追求核心性能的產品,具體規格見下表。

▲EPYC 9004、EPYC 7003、英特爾第12代酷睿、銳龍7000以及英特爾第11代酷睿處理器(從左到右)的外觀對比,可以看到EPYC 9004大了不少。

計算和擴展的領先地位:EPYC 9004技術架構一覽

毫不夸張地說,EPYC 9004是目前市面上最先進的企業級產品之一。它在CPU架構、Chiplet應用以及互聯方式上,幾乎都是當前技術條件下所能達到的極致。這一次,AMD在超大規模的企業級產品研發上進入了一個新的層次,短時間內,能超越它的只有AMD自己的下一代產品。

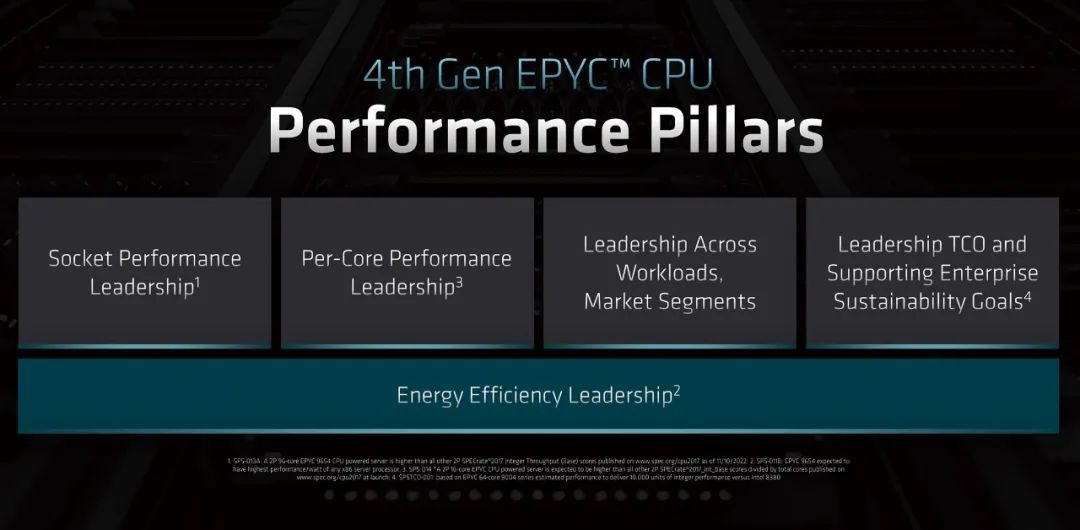

設計目標:擁有擴展和計算性能的優勢地位

▲AMD EPYC 9004的設計理念

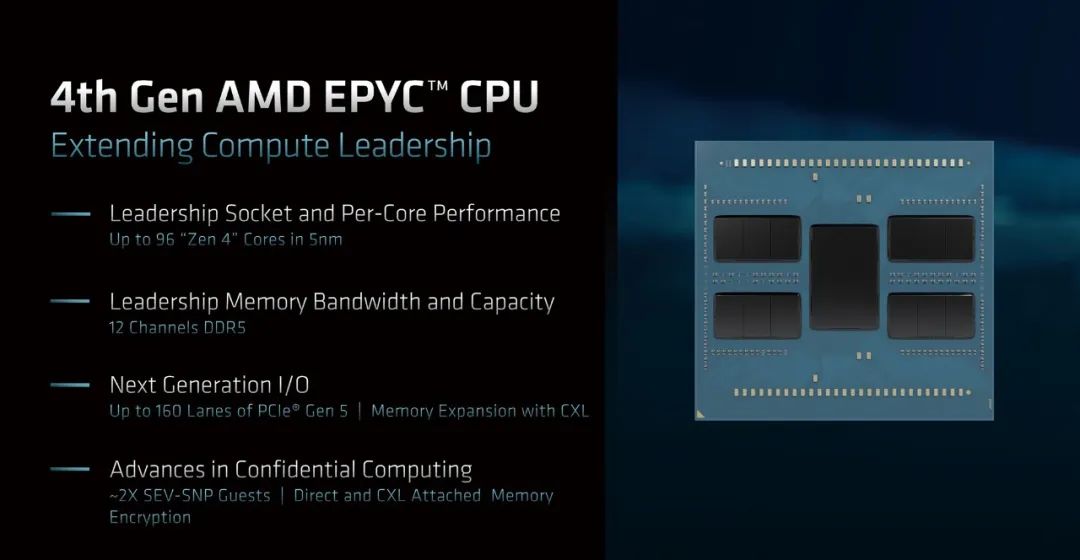

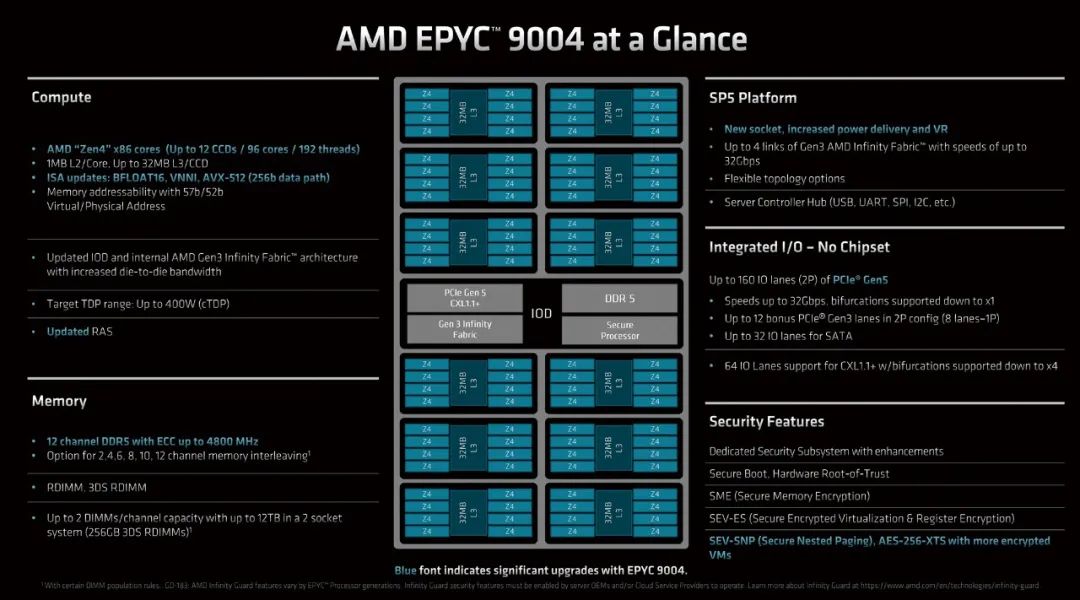

按照慣例,我們先來看看EPYC 9004的設計理念和實現情況。AMD EPYC 9004的設計理念就是繼續保持計算性能和擴展能力的優勢地位。AMD分四個方面進行了闡述:首先是擁有最先進的單核心性能和單插槽性能,這依靠最新的Zen 4架構和5nm工藝實現;其次是配備超大的內存帶寬和容量,這依靠12通道的DDR5內存來實現;第三是采用全新的下一代IO接口,這包括最大160通道的PCIe 5.0控制器以及可以利用CXL協議擴展的內存尋址功能等;第四則是加密計算方面的新進展,主要通過CXL以及2倍的SEV-SNP功能來實現。

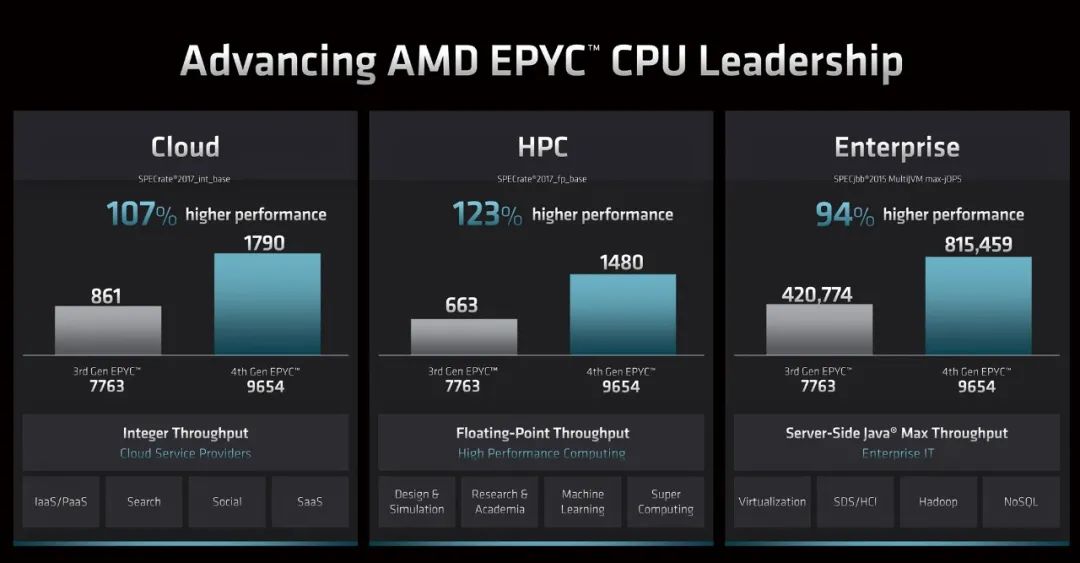

▲EPYC 9004和上代產品的性能比較情況

根據AMD官方數據顯示,和EPYC 7003系列的頂級型號EPYC 7763相比,EPYC 9004系列中的頂級型號EPYC 9654能夠在云端、HPC和企業級性能方面分別領先107%、123%以及94%。AMD宣稱第四代EPYC處理器是全世界最好的數據中心處理器,擁有最快的數據中心性能、領先的能源效率、優秀的TCO表現、安全的加密計算能力以及豐富的生態系統。

▲AMD EPYC 9004的宏觀布局

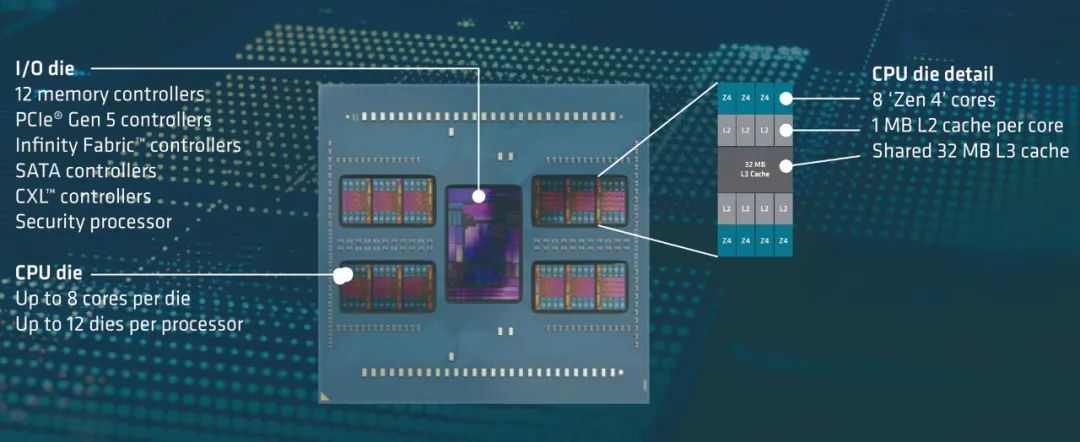

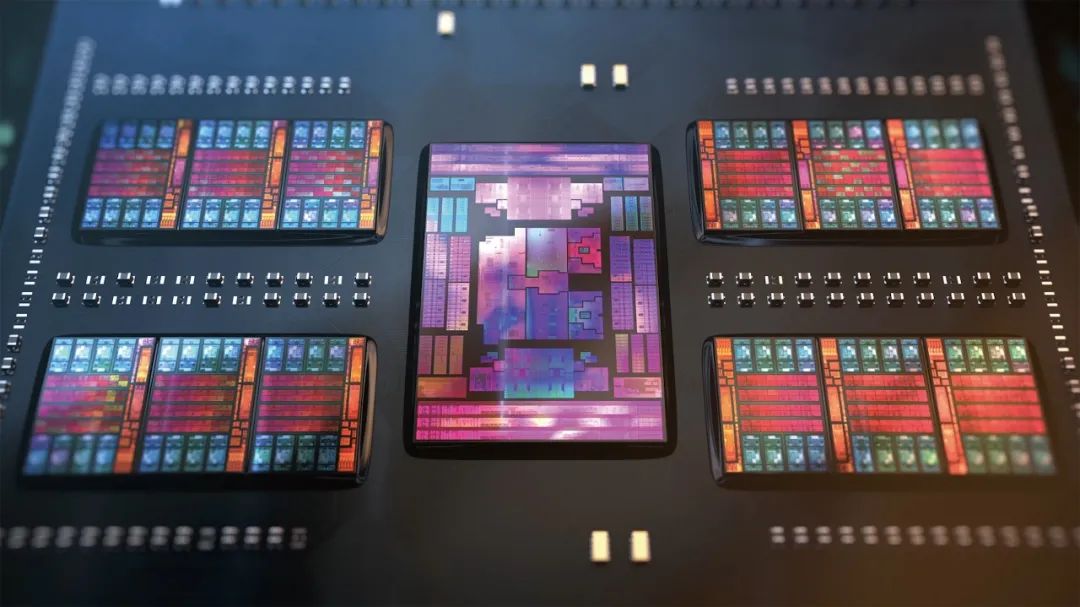

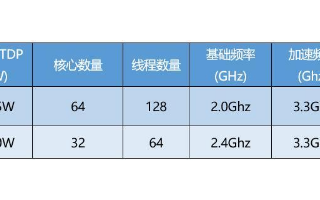

為了達到這些設計要求,EPYC 9004在結構上依舊采用了Chiplet設計,布局在中間的是全新設計的IO芯片,周圍的CCD單元數量增加到12個。每個CCD中依舊包含了8個CPU核心和相應的緩存,以及32MB L3緩存。EPYC 9004核心數量大增的原因是CCD數量從上代產品的最多8個增加到了最多12個,這使得它最多能提供96核心192線程。

Zen 4架構:IPC提升14%

AMD在企業級產品和消費級產品上采用了同樣的核心微架構:EPYC 9004和桌面銳龍7000系列都是最新的Zen 4架構。有關Zen 4架構,本刊在之前銳龍7000首發文章中曾有過介紹,本文再簡單回顧一下。

▲Zen 4微架構及改進一覽

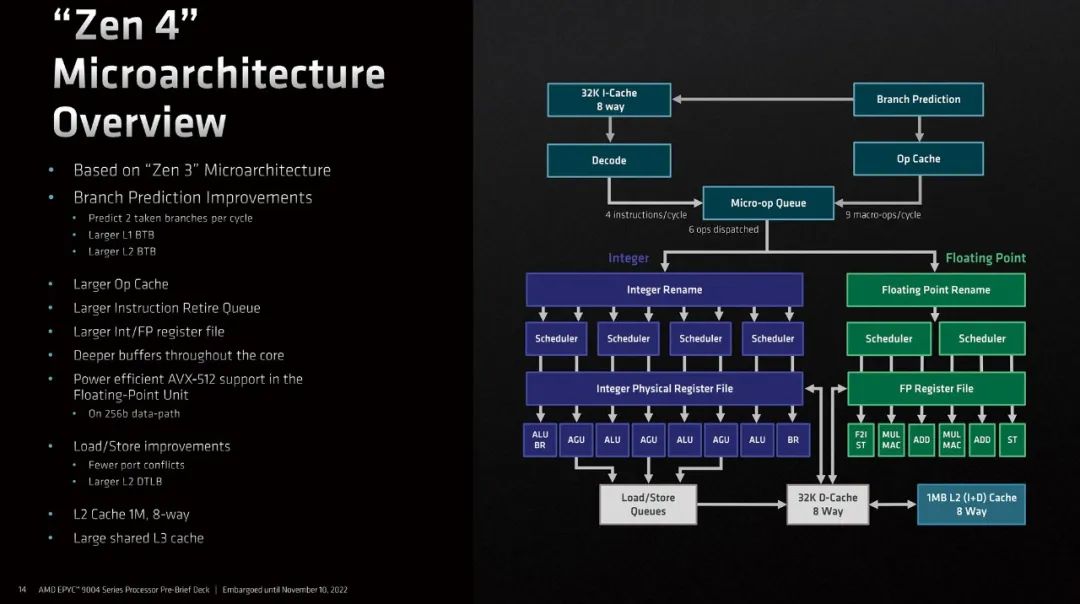

AMD Zen 4架構是基于Zen 3架構改進而來,在架構設計上,AMD希望實現更高的性能、更低的延遲和更好的能效比。其中性能的提升來自頻率和IPC的提升;更低的延遲主要是提升了緩存的性能并且降低了整個架構的平均延遲;能效比方面則通過新設計、新工藝以及將移動端的一些技術移植在桌面端,降低了整個CPU的動態功耗。

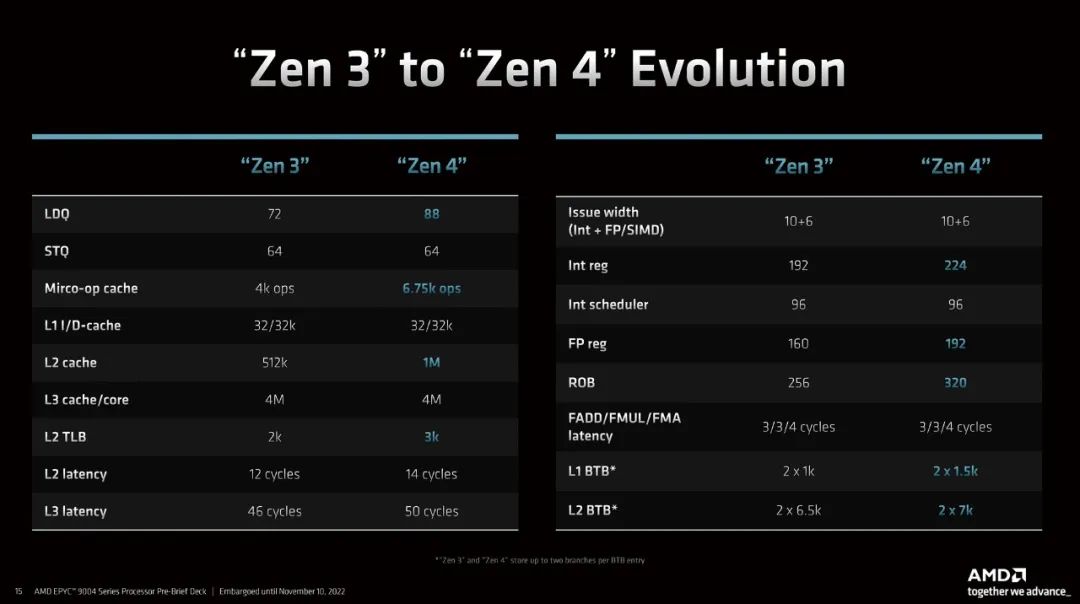

▲Zen 4架構相比Zen 3架構的重要提升

具體來看,Zen 4架構在分支預測、Op緩存、指令排序相關窗口、整數或浮點寄存器、每核心更深的緩沖區、后端讀取和加載等方面進行了優化。特別的變化是另外加入對AVX-512指令集的支持,以及重新調整的每核心1MB、8-way L2緩存。

前端方面,分支預測部分有大幅加強。AMD使用了一個更強有力的分支預測單元,每周期可以執行2次分支預測。此外,L1分支目標緩沖區的容量提升了50%,達到1.5K條目,L2分支目標緩沖區則達到7K。Zen 4還擁有更大的Op緩存、更大的指令回寫隊列,它們在很大程度上提升了處理器的前端性能。

執行單元部分,Zen 4沒有提升執行單元的數量,而是持續增大重排緩沖區。它增加了浮點/整數寄存器的體積,整數從192增加至224,浮點從160增加至192,核心緩沖區達到320條目。執行單元方面依舊是每周期10個INT和6個FP。

后端的讀取和加載部分,Zen 4擁有更大的讀取排序單元,更少的緩存端口沖突以及增大50%的L2 DTLB。另外依舊擁有每周期3個內存操作,最多每周期3個讀取和2個寫入。

緩存方面,最明顯的改變是每個核心的L2緩存翻倍到1MB,這樣可以降低CPU核心的未命中率并提升命中率,同時也降低了從L3和內存讀取數據的幾率。但是由于L2緩存增大,延遲也相應提升,L2和L3的延遲分別增加到最多14個周期和最多50個周期。

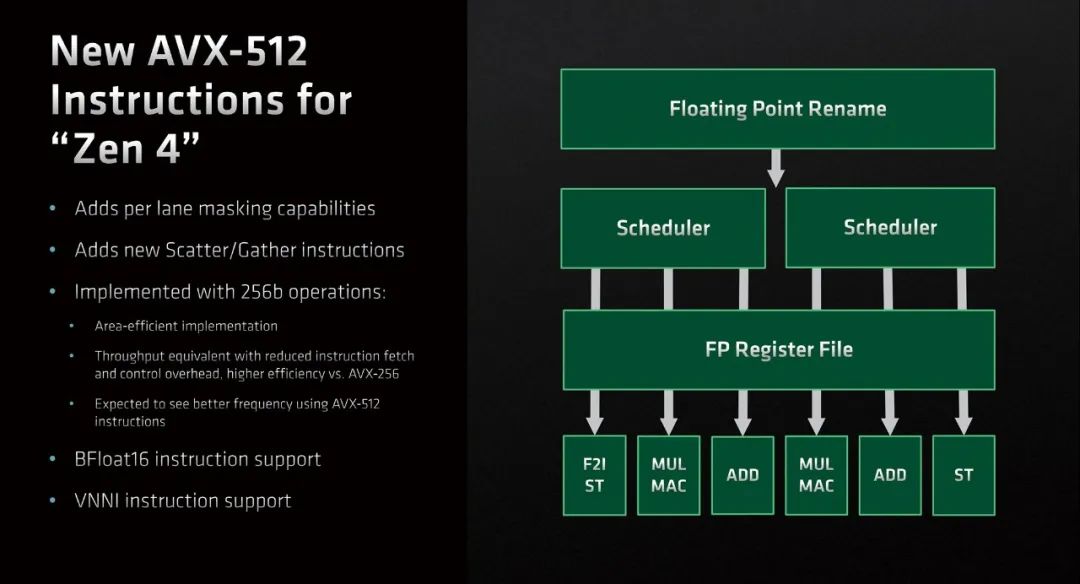

▲AMD在Zen 4上設計了全新的AVX-512引擎,和英特爾的路線有巨大差異。

在指令集方面,Zen 4實現了對AVX-512指令集的支持。Zen 4采用了2個AVX 256來合并執行1個AVX-512,而英特爾采用了獨立的AVX512 SIMD核心。AMD的設計可以節省晶體管資源,并且不需要降低頻率來運行AVX-512。但是當同時執行AVX2和AVX-512的時候,則必須完成一個后再執行另一個。AVX-512比之前Zen架構多核心執行FP32的工作效能提升了30%。此外,Zen 4也實現了對BF16數據格式的支持,這是AI計算中新興的一種重要數據格式。

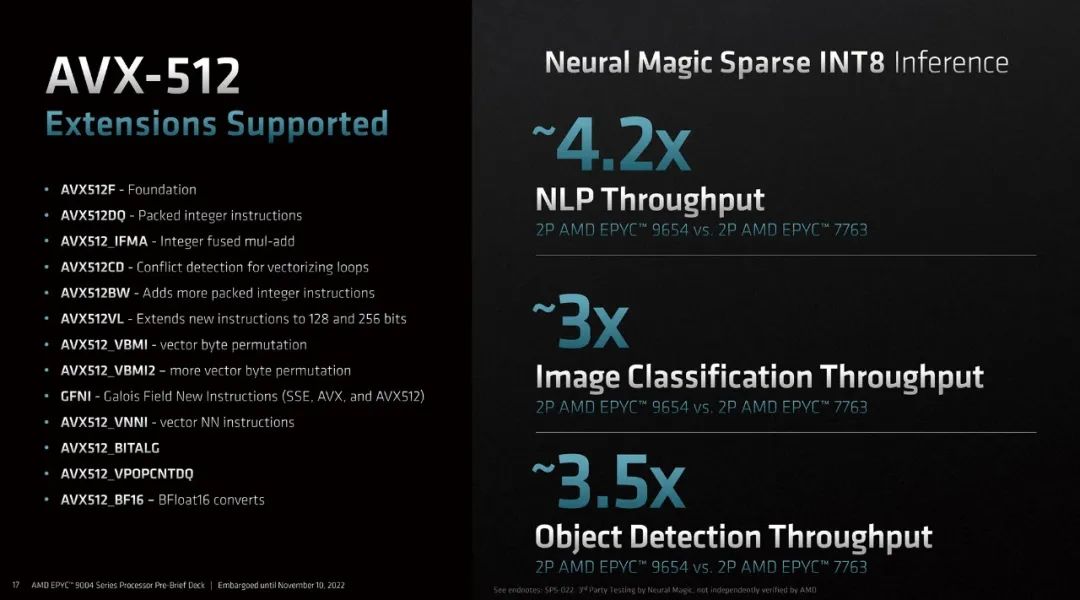

▲在啟用AVX-512后,相關性能得到了巨大提升。

根據AMD官方數據顯示,在支持AVX-512后,使用2路EPYC 9654(192核心)對比2路EPYC 7763(128核心),在NLP、圖像識別以及物體檢測的吞吐量測試中,前者的領先幅度分別達到4.2倍、3倍和3.5倍。

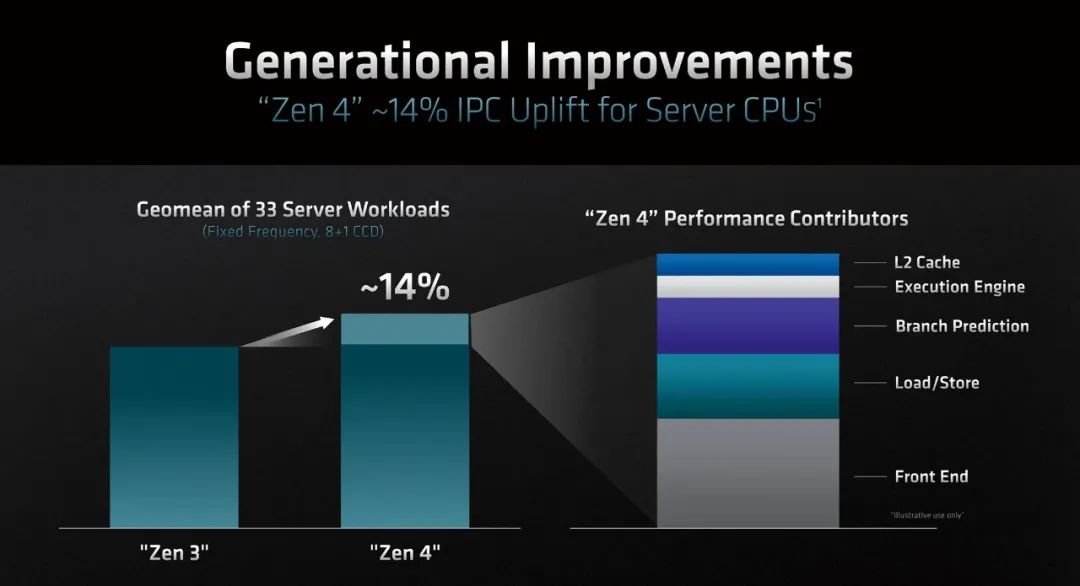

AMD還給出了Zen 4相比Zen 3的性能改進情況。總的來看,Zen 4有大約14%的IPC提升。其中貢獻最大的是前端的改進,其次是存儲和加載部分,再次是分支預測部分,執行部分和L2部分的改進帶來的性能增幅則相對較小。在發布銳龍7000系列的時候,AMD給出的IPC提升數據是13%,所以這里提到的14%應該是根據服務器所面向的不同負載重新測試而來。

▲AMD Zen 4架構在服務器端取得了14%的IPC提升

最后再來看看安全方面的內容。Zen 4架構目前支持安全加密的虛擬化,包括SEV-ES、SEV-SNP,內存加密支持AES-256-XTS,支持最多1006個加密的客戶機以及多主機秘鑰SMKE。此外,它還支持虛擬化X2APIC、免SMT攻擊和額外的SPEC_CTL功能等。

12通道DDR5內存

每核心帶寬至少比上代產品提升50%

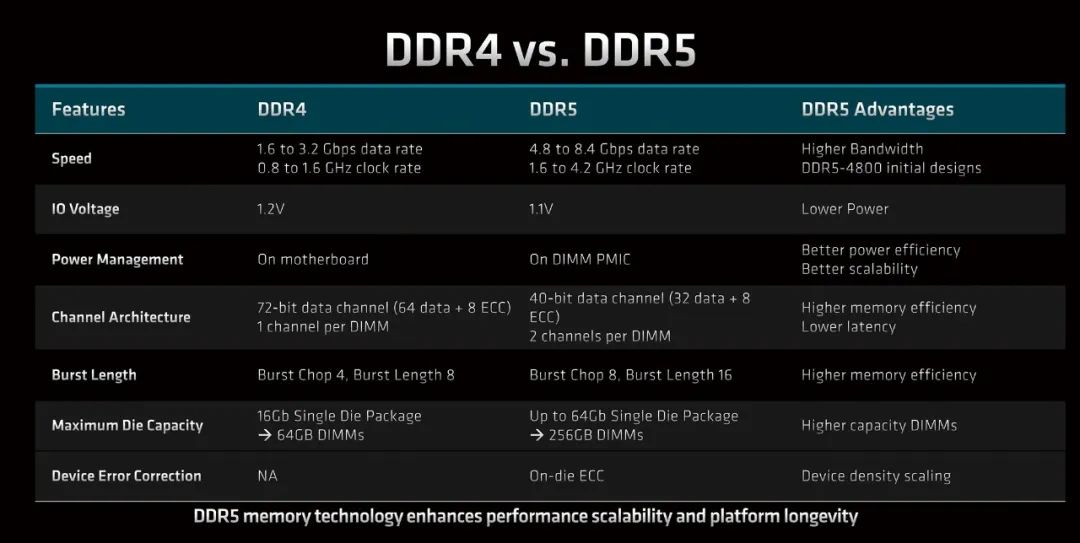

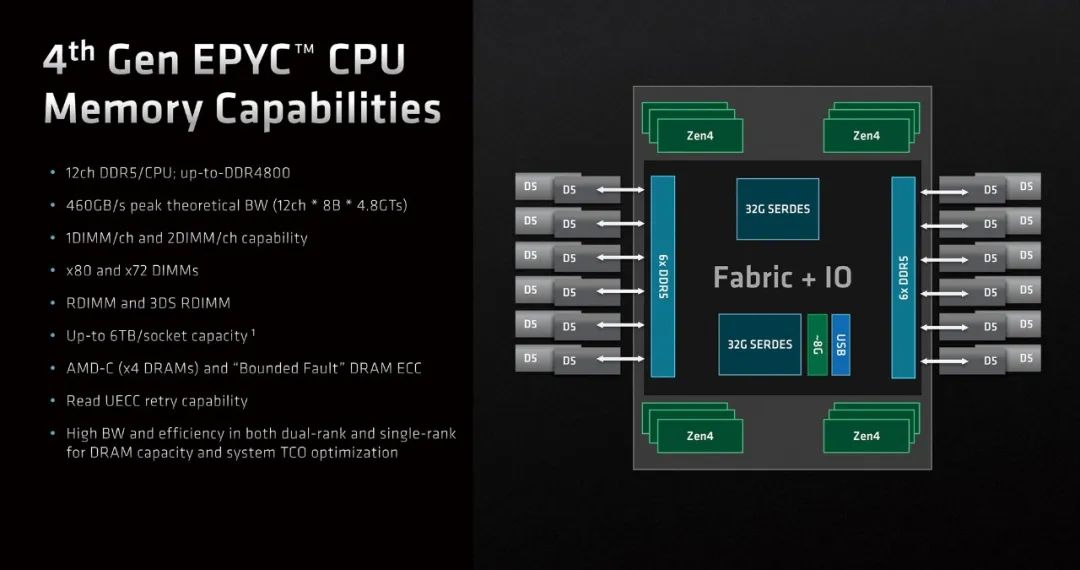

所有EPYC 9004系列處理器都支持12通道DDR5內存,相比上代支持的8通道DDR4內存有巨大進步。從內存帶寬來看,DDR5的使用在很大程度上緩解了超多核心處理器內存帶寬不足的情況。

▲AMD在EPYC 9004上全面啟用DDR5內存

舉例來說,上代EPYC 7763擁有64個核心128線程,支持8通道DDR4內存,內存總帶寬為204.8GB/s,平均每核心3.2GB/s。新一代的EPYC 9654擁有96核心192線程,支持12通道DDR5內存,內存總帶寬為460.8GB/s,平均每核心4.8GB/s。EPYC 9654在處理器核心數量更多的情況下,每核心內存帶寬提升了50%。如果是48核心或者32核心產品,每核心內存帶寬的提升會更大,這為內存帶寬敏感型應用帶來了極為不錯的性能提升空間。

▲EPYC 9004的內存架構和特性一覽

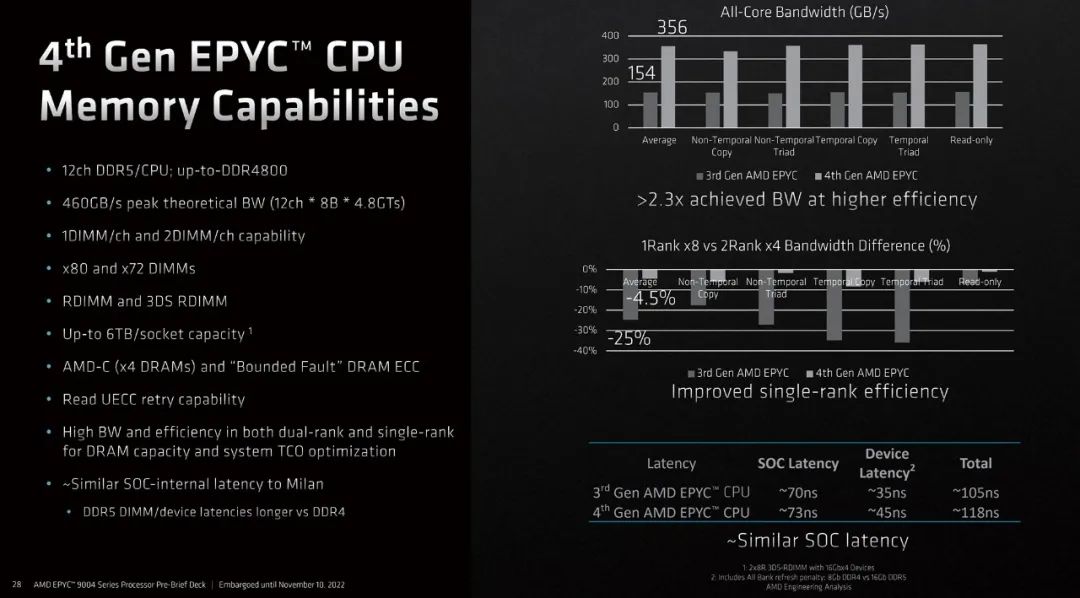

從AMD官方給出的實際測試數據來看,EPYC 7003系列的實際內存帶寬大約為154GB/s,EPYC 9004則高達356GB/s,是前代產品的大約2.3倍。延遲方面,由于EPYC 9004支持的DDR5內存容量更大、通道數量更多,因此延遲有所上升。EPYC 9004的SoC延遲大約在73ns左右,設備延遲大約是45ns左右,因此總延遲在118ns左右,而EPYC 7003的對應數據分別是70ns、35ns和105ns。從整體上來看,EPYC 9004的延遲略高,但是考慮到它擁有更大的帶寬,這一點是完全可以接受的。

▲EPYC 9004的內存性能情況

在內存容量方面,所有EPYC 9004系列處理器都支持高達6TB容量。不過目前AMD只給出了1DPC(DIMM Per Channel),也就是12個內存通道、12條內存插槽下的配置情況,內存最高支持12通道的DDR5 4800。至于2DPC配置,AMD宣稱會在2023年第一季度再公布詳細信息。不過考慮到EPYC 9004不小的面積,12通道DDR5內存插槽所占的體積以及接近400W的CPU供電所需要的PCB面積,未來出現24通道、48插槽的2DPC主板的可能性較低,并且6TB內存對大多數應用場景來說已經足夠了。

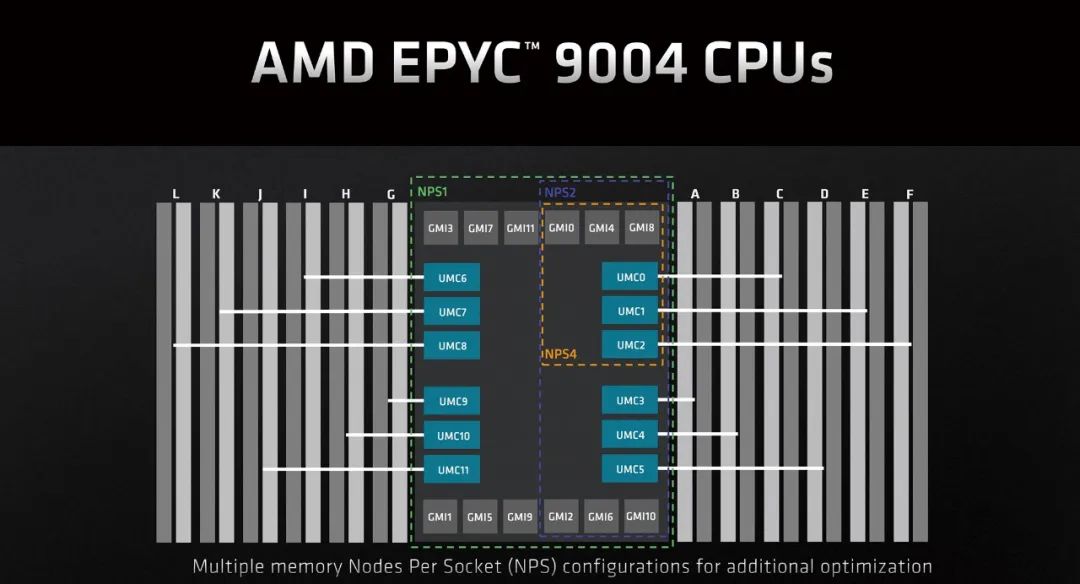

▲EPYC 9004設計有內存分區管理

最后再來看看內存分區。由于EPYC 9004系列處理器的規模很大,因此AMD也提供了NUMA域的管理和設置,使得用戶可以在某些情況下對內存和核心進行調配。它包括了NPS1、NPS2和NPS4三種分區方式:NPS1就是整個處理器;NPS2是將處理器分為2個部分,每個部分有6個內存通道和6個GMI3接口;NPS4則是將處理器分為4個部分。

IO芯片和總線連接系統:采用最新的GMI3連接

AMD在EPYC 9004上繼續采用大獲成功的Chiplet方案。整個處理器除了CCD之外,還有一個IO芯片。EPYC 9004的CCD由臺積電5nm工藝制造,這也是首個使用5nm工藝的企業級CPU產品。IO芯片也采用了臺積電6nm工藝制造。

▲EPYC 9004架構簡圖和特性一覽

因為EPYC系列一直采用Chiplet方案,因此在CCD和IO芯片之間需要通信協議予以連接。上一代EPYC處理器采用的是GMI2總線,其IO芯片內部有8個GMI2總線端口,因此總共能支持8個CCD單元連接,每個CCD擁有2個GMI總線接口,可以根據需要進行配置。

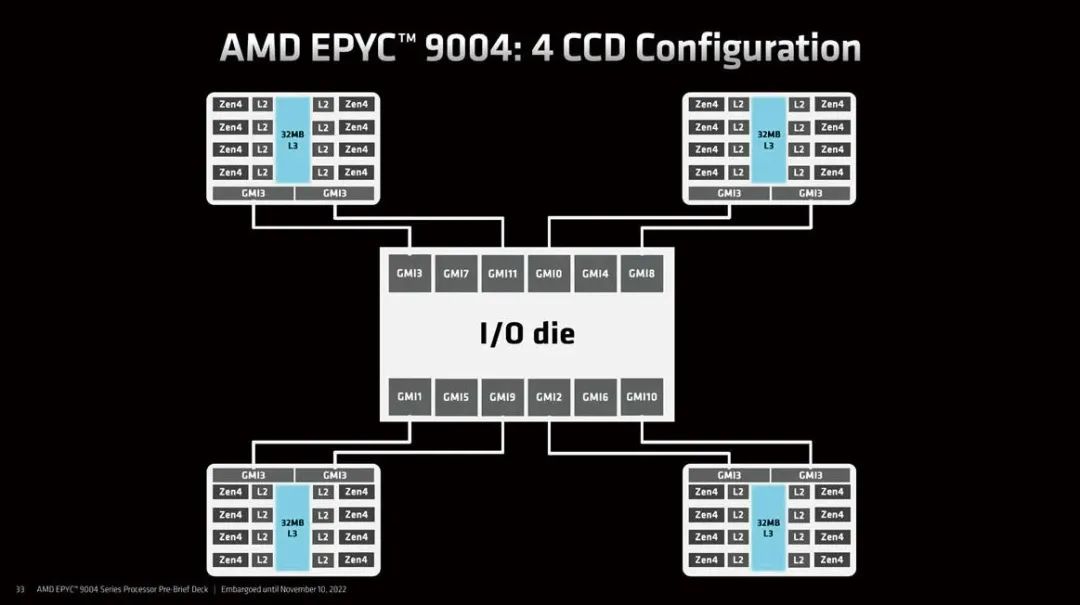

▲EPYC 9004的Chiplet連接圖一覽

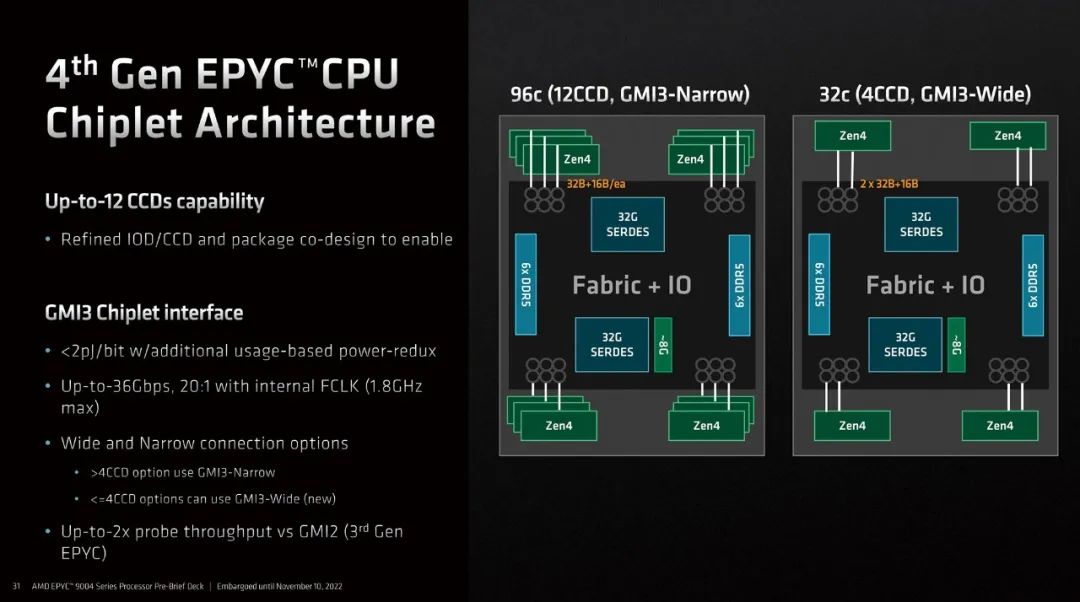

EPYC 9004升級為GMI3總線。其中Zen 4架構的8個CCD和12個CCD采用的是每個CCD與1個GMI3總線互聯,4個CCD架構中每個CCD通過2個GMI3總線進行互聯,從而實現更高的互聯帶寬。對于核心數量較少的型號,這樣的設計能夠為CCD數量較少時,帶來更大的互聯帶寬。IO芯片的GMI3總線端口數量升級到12個,因此可以最多連接12個CCD。

帶寬和功耗方面,每個GMI3總線每周期可以實現32Bit的數據讀取和16Bit的數據寫入,能耗為2pj/bit。帶寬方面最高可達36Gbps,和FCLK的頻率比值是20∶1,最高可達1.8GHz。AMD宣稱,GMI3的吞吐能力最高可達GMI2的2倍。

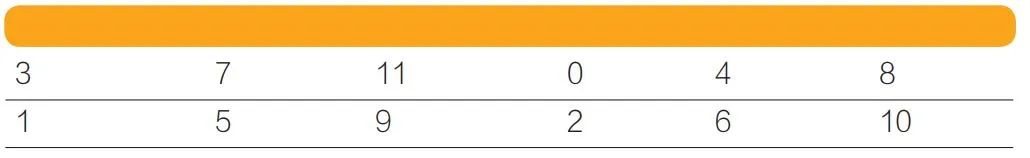

值得一提的是,IO芯片上的GMI3端口排序是經過設計的。它的端口序號排列如下:

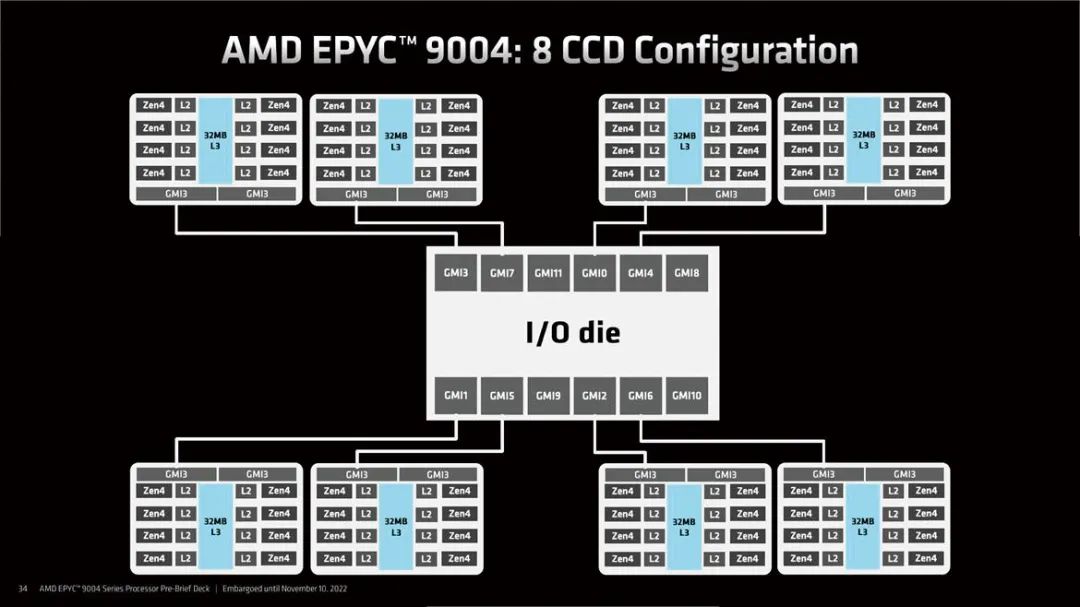

顯然,GMI3的端口并不是按照常規的從小到大或者從大到小排列的。AMD這樣做的原因,是考慮到CCD和IO芯片的距離和延遲。以96核的EPYC 9654為例,每個CCD有8個處理器核心,12個CCD分布在IO芯片兩側,每側各6個CCD。考慮到幾何和空間形狀,將優先使用IO芯片周圍的某幾個端口。比如有8個CCD,將使用GMI0~GMI7這幾個端口,位于中間和最遠端的GMI8、GMI9、GMI10和GMI11反而會空余。AMD還提到,靠近IO芯片的CCD位置將被優先使用,這意味著如果是8個CCD,那么最遠4個位置上的CCD要么徹底被屏蔽,要么干脆就是占位用的晶體塊。

AMD還特別對連接模式進行了說明。GMI3有兩種連接模式,一種被稱為窄連接模式,主要用在大于4個CCD也就是32核心以上的處理器上;另一種被稱為寬連接模式,它是新加入的,主要用在小于等于4個CCD,也就是32核心以下的產品。

▲EPYC 9004的8CCD連接模式,注意GMI11和GMI9等端口的空閑。

在窄連接模式中,如果8個CCD連接到IO芯片上,就像上文提到的那樣,將使用GMI0~GMI7進行連接。此時每個CCD的1個GMI3端口將被激活,并與IO芯片相應的GMI3端口進行連接,空余剩下的4個端口。

▲EPYC 9004的4CCD連接模式,每個CCD采用2個GMI總線連接IO芯片。

在寬連接模式中,每個CCD的2個GMI3端口將被激活,并和IO芯片上的GMI3端口進行連接。以4個CCD為例,每個CCD的第一個GMI3端口將先和GMI0~GMI3端口連接,然后第二個GMI3端口會和GMI8~GMI11端口連接,GMI7、GMI5、GMI4和GMI6端口將被閑置。

全新的SP5插槽:更大、更穩固

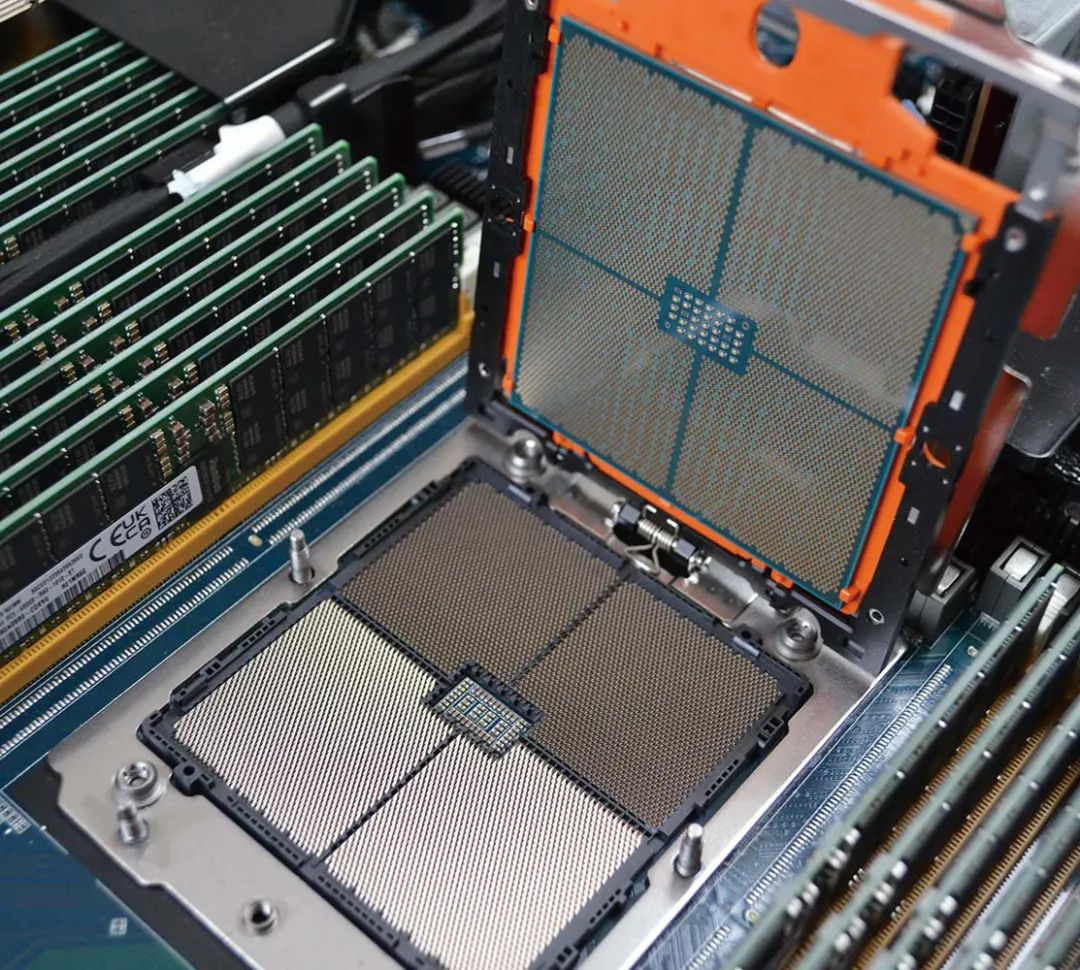

EPYC 9004的插槽上也被更新。新插槽被稱作Socket SP5,不兼容上一代Socket SP3。不兼容的原因主要是因為EPYC 9004系列處理器的基板為了放下12個CCD和IO芯片,變得更大。更多的內存通道、供電和CPU核心,也要求有更多的觸點來傳輸數據。

▲Socket SP5和插入其中的EPYC 9004處理器,共有6096個觸點。

官方數據顯示,Socket SP3的長寬分別是58.5mm、75.4mm,面積為4410.9mm2,包含了4094個觸點或者彈性接觸片。相比之下,Socket SP5的長寬分別為72mm、75.4mm,總面積達到5428.8mm2,包含了高達6096個觸點或者彈性接觸片。Socket SP5的CPU供電能力高達400W,這剛好對應了EPYC 9004系列處理器的最大功耗值。

▲ AMD給出了不同接口處理器的散熱器示意圖,可見SP5的散熱器更大。

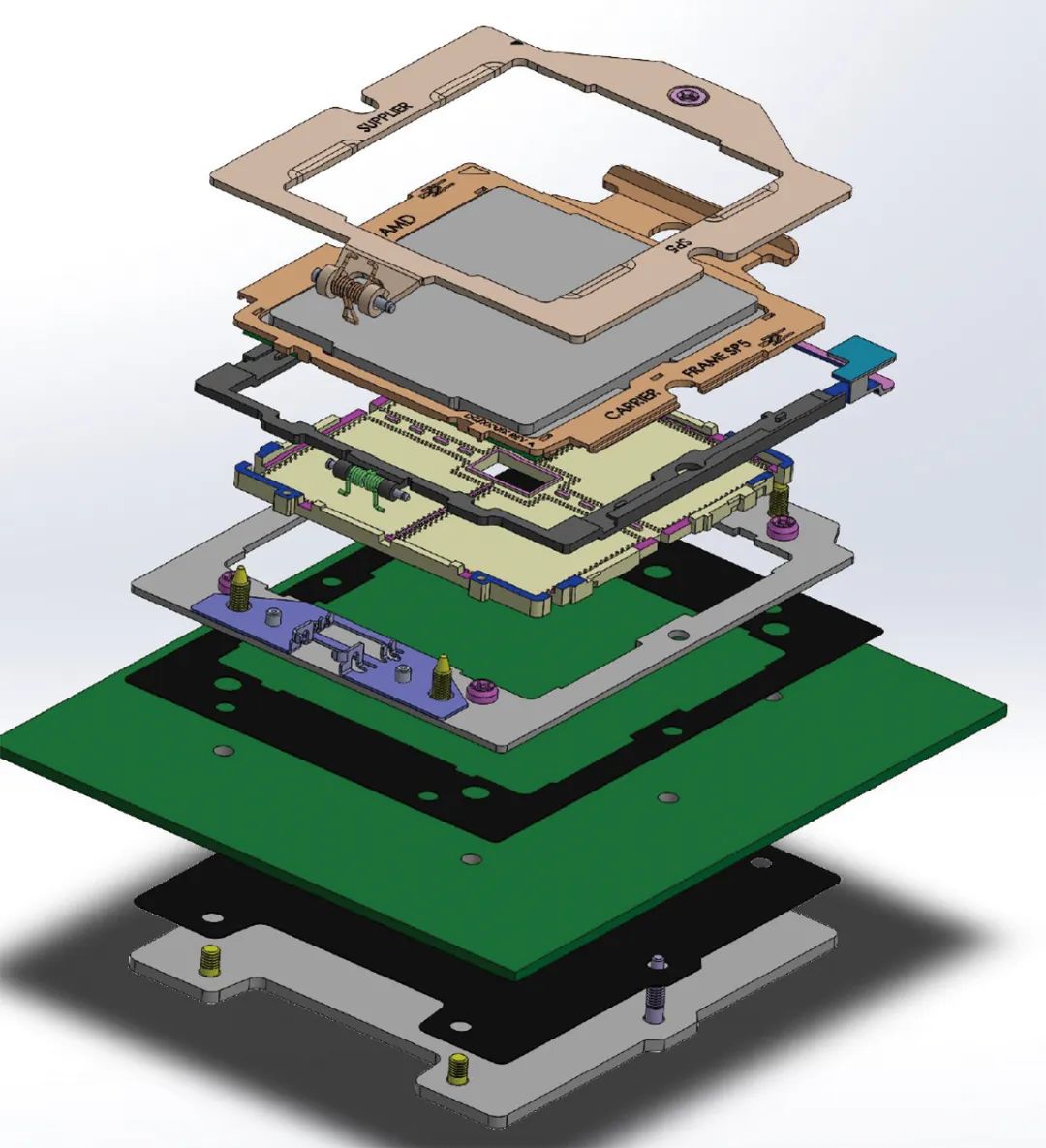

▲Socket SP5結構分層圖

Socket SP5在安裝方式上沒有做出太多改變,依舊采用先讓處理器模塊“滑入”扣具,然后扣下并固定在主板上的方式。這種安裝方式和桌面處理器需要手動將處理器放入插槽的方法完全不同,起固定作用的主要是扣具。值得注意的是,之前在Socket SP3處理器上出現過3個緊固螺絲由于緊固不到位導致接觸不良,從而使得某些內存通道消失的情況。因此在Socket SP5上,AMD選擇了多達6個緊固螺絲來實現主板和CPU的穩定連接,并平衡應力。相比上代產品,Socket SP5在耐久性方面更為出色。

雙CPU互聯:最多對外提供160條PCIe 5.0總線

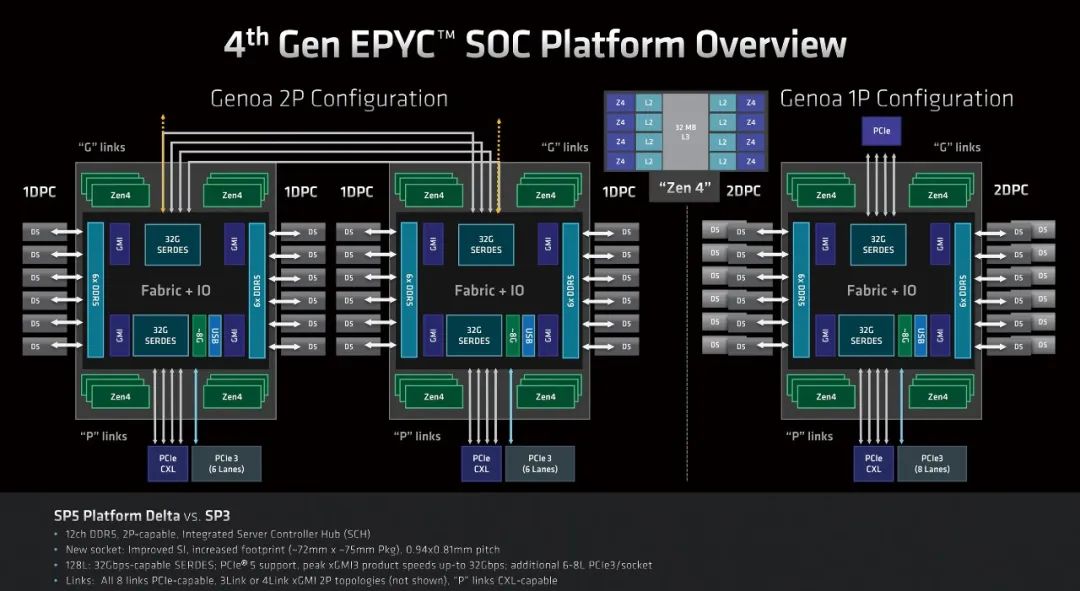

再來看有關雙CPU互聯的內容。EPYC 9004系列中2P型號的處理器可以搭建雙路系統,而在2個CPU的互聯上,它有一些新的變化。

▲AMD EPYC 9004系列處理器的1P、2P配置圖

▲AMD依舊采用IF總線連接2個處理器,不過EPYC 9004多了很多功能和設置。

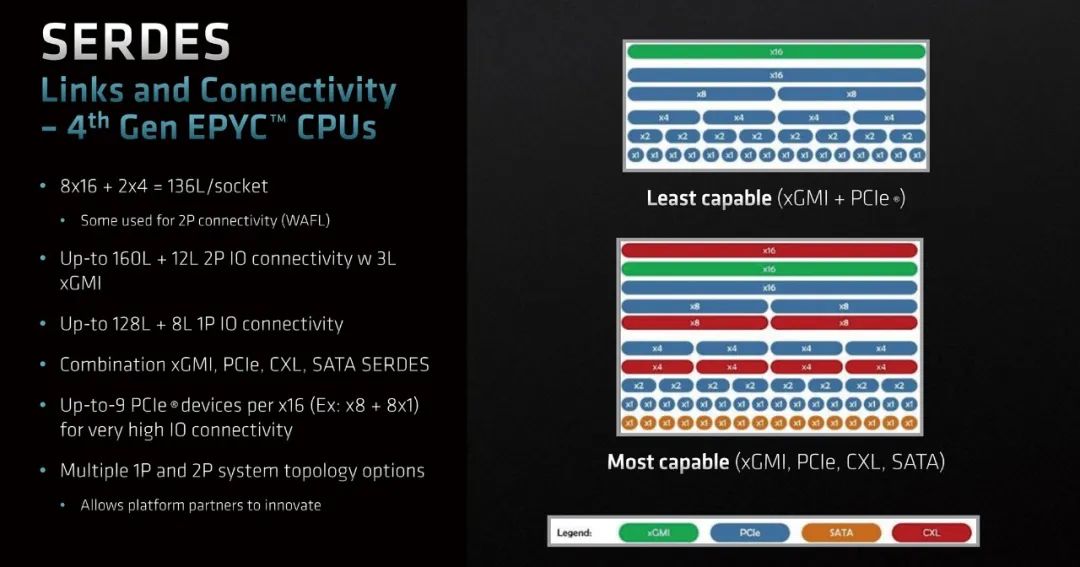

每個EPYC 9004處理器能夠對外提供128條PCIe 5.0通道。當組建2P系統時,通過IF總線使用的SerDes(串行器-解串器,AMD的SerDes支持兩種類型的連接,一種類型是支持標準的GMI或者PCIe接口、Infinity Fabric總線等,另一種則是支持其他類型的接口,包括SATA、CXL等,用戶可以根據需要進行配置),最多有64條通道被設置為4條Infinity Fabric總線(后文簡稱IF總線)來實現2個CPU的互聯傳輸。也就是說,在AMD的定義中每一條IF總線實際上相當于PCIe 5.0 x16的規格。

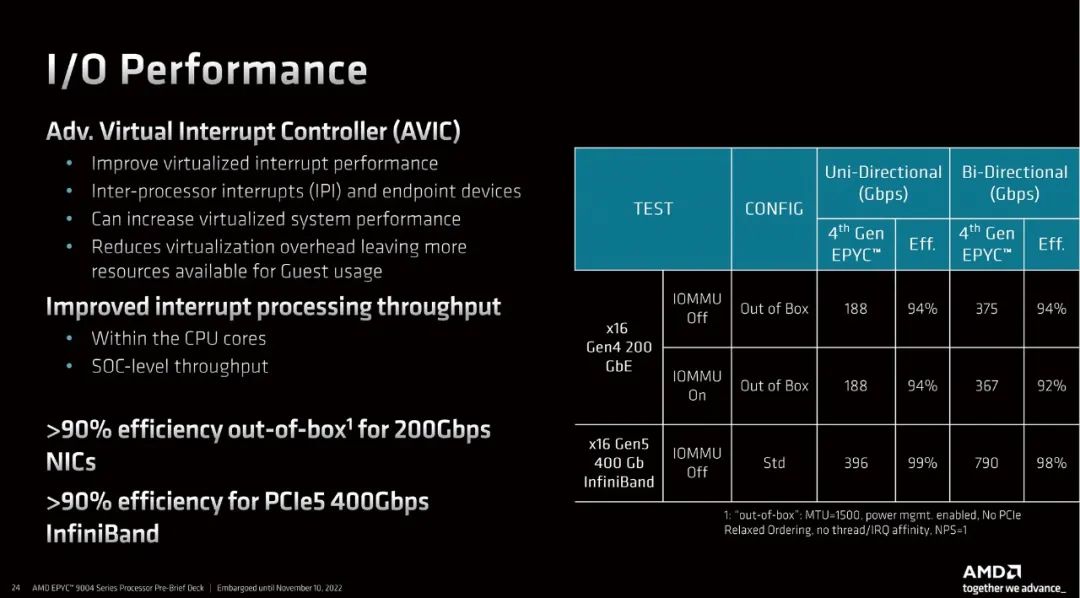

▲EPYC 9004的IO性能一覽

早期的IF總線采用的是PCIe 3.0 x16規格,帶寬較低。在升級到PCIe 5.0 x16規格后,其帶寬大增,所以可能有部分用戶認為3條IF總線已經足以承擔2個CPU的互聯工作。AMD允許用戶自行選擇啟用3條還是4條IF總線實現2P互聯操作。如果是3條的話,那么多余的1條IF總線可以被釋放為PCIe 5.0 x16通道。這樣一來,兩個CPU在3路IF總線連接的情況下,每個CPU最多可以空余80條PCIe 5.0通道,2個CPU就是160條。另外,IO芯片還能夠對外釋放12條PCIe 3.0通道。

▲EPYC 9004處理器的擴展和連接都非常自由

AMD對走線也進行了更新。現在IO芯片中的總線控制器(SerDes)被分為2個,體現在CPU的物理結構上,就是背部觸點兩側都可以連接總線輸出。在上一代EPYC 7003上,只有一側可以輸出IF總線或PCIe總線,并往往在主板上部。此時如果要連接主板下部的設備,就需要較長的走線并增加主板設計的復雜性。在EPYC 9004上,由于有兩個總線控制器且線路可以從CPU兩側走,因此更方便。AMD將CPU上部的線路稱為P總線,下部稱為G總線。其中P總線往往用于組成IF總線連接CPU,G總線用于連接外部設備。當然廠商也可以自由設置,比如使用“2P+2G” 的方式來連接CPU,或者其他廠商認為方便的設計亦可。

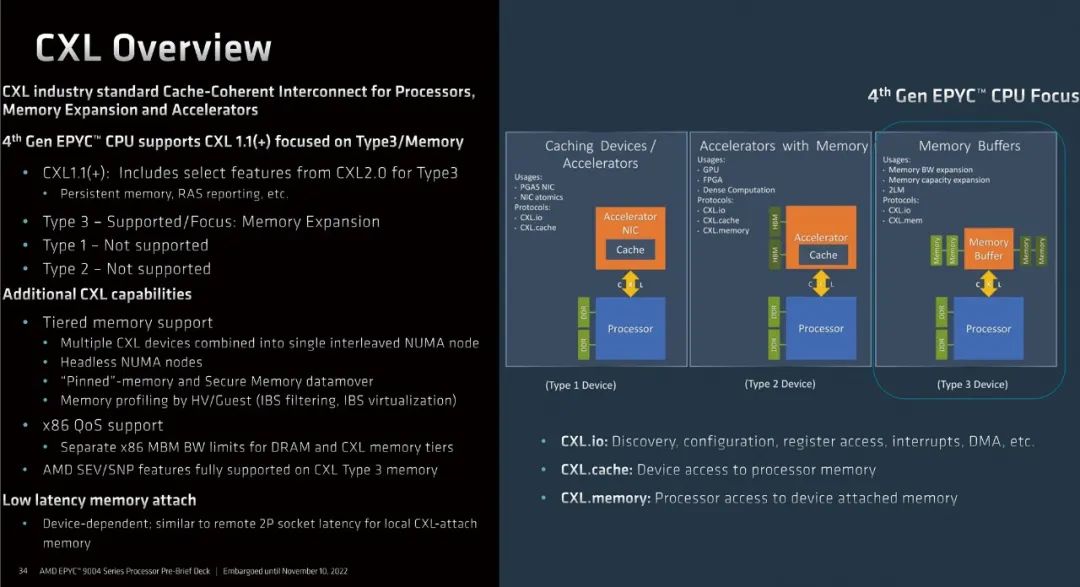

CXL 1.1+:提供超大規模的內存尋址空間

在互聯技術特性上,EPYC 9004對CLX 1.1+的支持是一個亮點。本刊之前介紹過有關CXL的技術內容,CXL的全稱是Compute eXpress Link,它是一個開放的行業標準,主要用于在CPU和加速單元(GPU、DPU)或者一些IO設備之間提供高速緩存一致性互聯,同時允許CPU在連接設備的相同內存區域上工作,從而提高性能和電源效率,并降低軟件復雜性,減少數據移動次數。該規范以PCIe 5.0作為技術基礎,最新修訂版本的CXL 3.0則以PCIe 6.0作為技術基礎。

CXL規范的推出速度非常快,在CXL 1.0技術還未準備好之前,CXL 2.0技術就已經到來,新規范要求在總線的SerDes級別提供內置支持,從而實現和遠程內存組的低延遲連接。因此,AMD不得不在新處理器的設計后期重新設計了CXL部分功能,還融入了包括持久內存和RAS報告等功能,但是其余部分則不能全部支持,因此AMD稱之為CXL 1.1+。目前AMD的CXL總線基于PCIe 5.0規范,和PCIe 5.0共用物理接口。

▲ AMD的CXL 1.1+只支持第三類,也就是內存擴展。

CXL支持三類設備,第一種常用于網卡這類高速緩存設備,第二種常見于GPU、AI等應用的內存加速器,第三種是內存擴展控制器,通常作為內存緩沖器,常用作內存帶寬或是容量的擴展。EPYC 9004目前只支持第三種方案,允許用戶將遠程內存作為本地內存進行尋址,并且允許將多個CLX Type-C設備聚合成一個交錯的NUMA節點,還支持“headless NUMA”節點。其他功能包括能夠優化本地內存和CXL內存之間延遲差異的QoS機制,支持AMD的SEV-SNP密鑰擴展和AES-256-XTS等功能。

AMD目前最多允許將64個PCIe 5.0通道分配給CXL 1.1+,單個CXL 1.1+允許最多16個通道,因此單個CXL 1.1總線帶寬為雙向128GB/s。如果啟用全部64個通道的話,帶寬會高達雙向512GB/s,這已經高出了12通道DDR5內存的460GB/s了。考慮到EPYC 9004高達96個CPU核心對內存帶寬的需求,這正是AMD支持CXL 1.1+的意義所在。

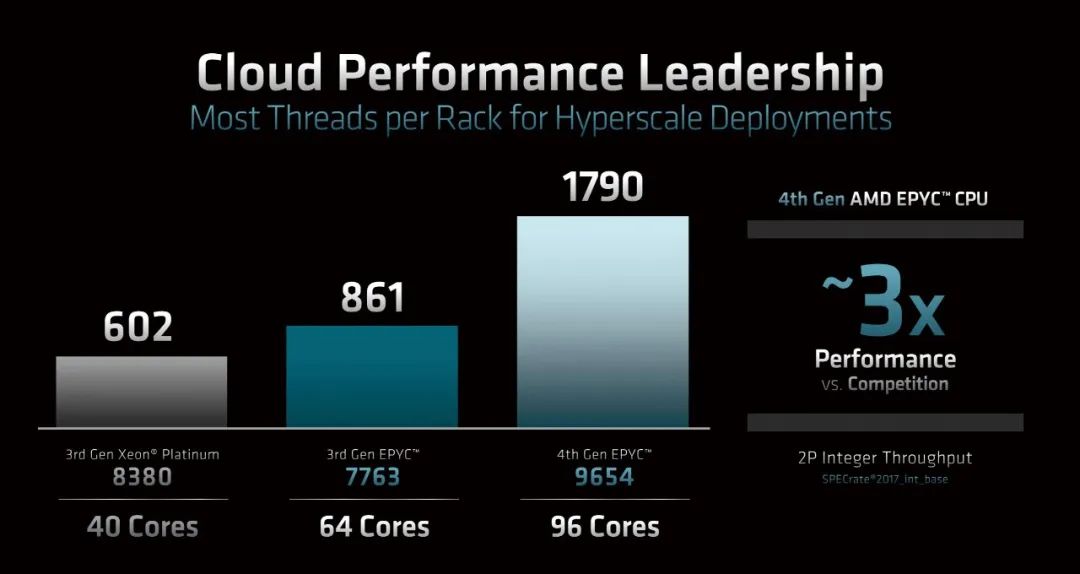

性能預覽:輕松拋離競爭對手

在架構介紹部分,AMD提及了不少性能方面的信息,不過最終還得看綜合性能情況。AMD選擇了英特爾第三代至強可擴展處理器,也就是Ice Lake-X架構的產品進行對比。

▲?EPYC 9004在云端方面的性能大幅度領先

▲AMD宣稱EPYC 9004在多項性能中領先

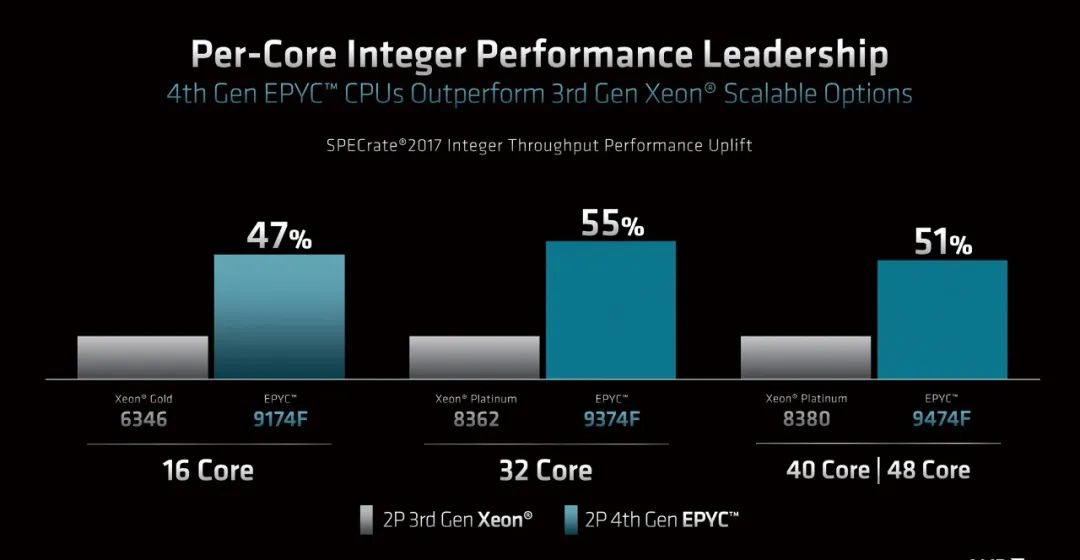

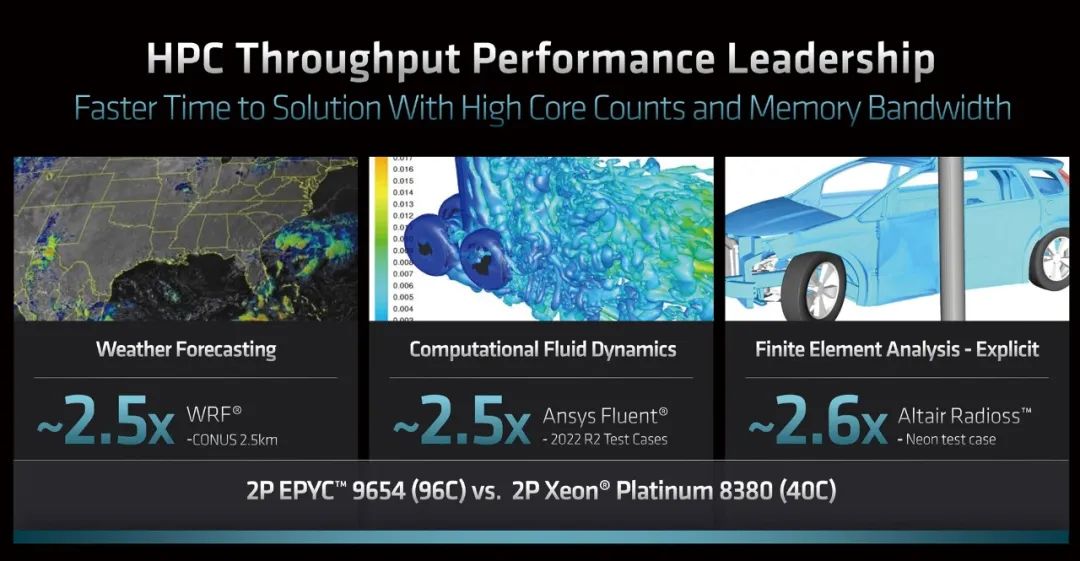

首先來看單核心性能。AMD使用了16、32、40/48核心的處理器進行對比。EPYC 9004系列的不同型號處理器在整數、浮點性能方面超越英特爾產品最多可達55%、96%。虛擬化性能方面,EPYC 7003的表現就足以抗衡英特爾產品,EPYC 9004的性能更是英特爾產品的2.8倍之多。在FSI模擬、3D渲染和商務(MySQL業務查詢)方面,EPYC 9654的性能分別是英特爾至強鉑金8380的大約2.1倍、2.4倍和2.7倍。HPC性能方面就更不用多說了,2P配置的EPYC 9654在天氣預報、計算流體和有限元分析方面分別是2P配置的英特爾至強鉑金8380的大約2.5倍、2.5倍和2.6倍。HPC單核心性能方面,同樣是這三項測試,32核心的EPYC 9374F性能是同為32核心的至強鉑金8362的2倍、1.7倍和1.7倍。

▲EPYC 9004系列不同型號處理器的單核心整數性能都大幅領先對手

▲EPYC 9004系列不同型號處理器的單核心浮點性能同樣大幅領先

▲HPC性能方面,EPYC 9004實現了對英特爾處理器的碾壓態勢。

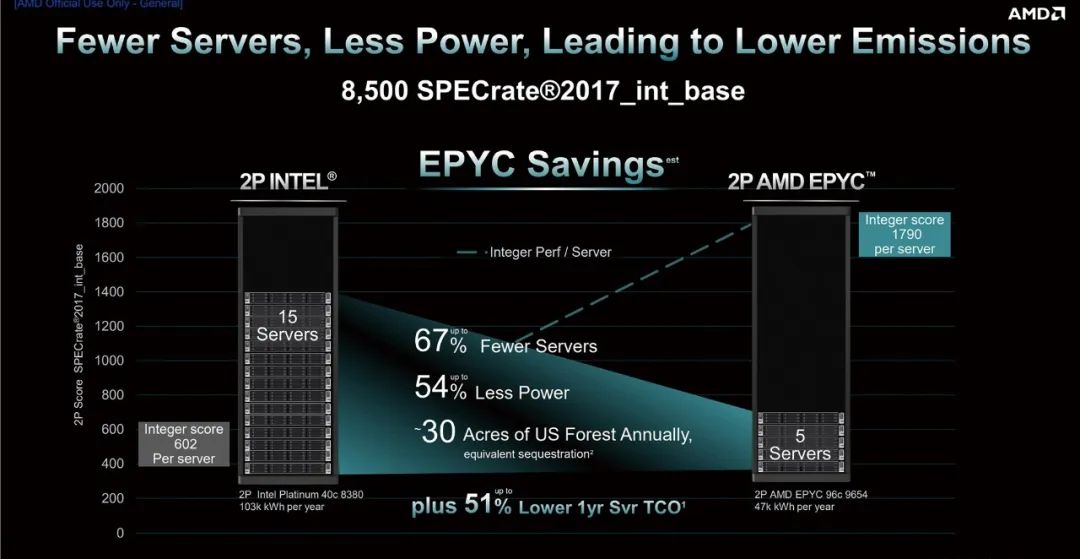

此外,AMD還評估了空間和電能需求。在同時處理1995個虛擬化需求的時候,2P的EPYC 9654處理器只需要5臺服務器即可完成,與之對應的英特爾至強鉑金8380則需要15臺服務器,AMD節約了67%的機架數量、52%的電能消耗(相當于34英畝森林所釋放的二氧化碳值),降低了40%的1年服務TCO。

▲AMD還評估了空間和電能需求,EPYC 9004系列更是大獲全勝。

在同樣性能的情況下,比如在SPECreat 2017整數基準測試中同樣獲得8500分,AMD只需要1P EPYC 9654的處理器使用10臺服務器即可,英特爾則需要2P的至強鉑金8380的處理器使用15臺服務器,這意味著AMD節約了67%的處理器數量、20%的核心數量、50%的能源消耗和46%的1年服務TCO。

AMD還展示了EPYC處理器在產業環境方面的情況。目前已經有數百家企業使用或者正準備使用AMD的產品,同時媒體和內容、制造業、5G和金融服務等行業都在使用AMD EPYC產品持續創造價值。歷經四代進化,AMD EPYC終于開創了一個非常不錯的產業環境,并正在逐漸拓展自己的市場范圍。

總結:強大的產品無須多言

從已知的信息和規格來看,EPYC 9004系列處理器代表了當前最先進、最強大的計算性能,無論是架構設計還是產品性能都沒有什么可挑剔的地方。

▲EPYC 9004的晶元結構示意圖,不同的部分清晰可見。

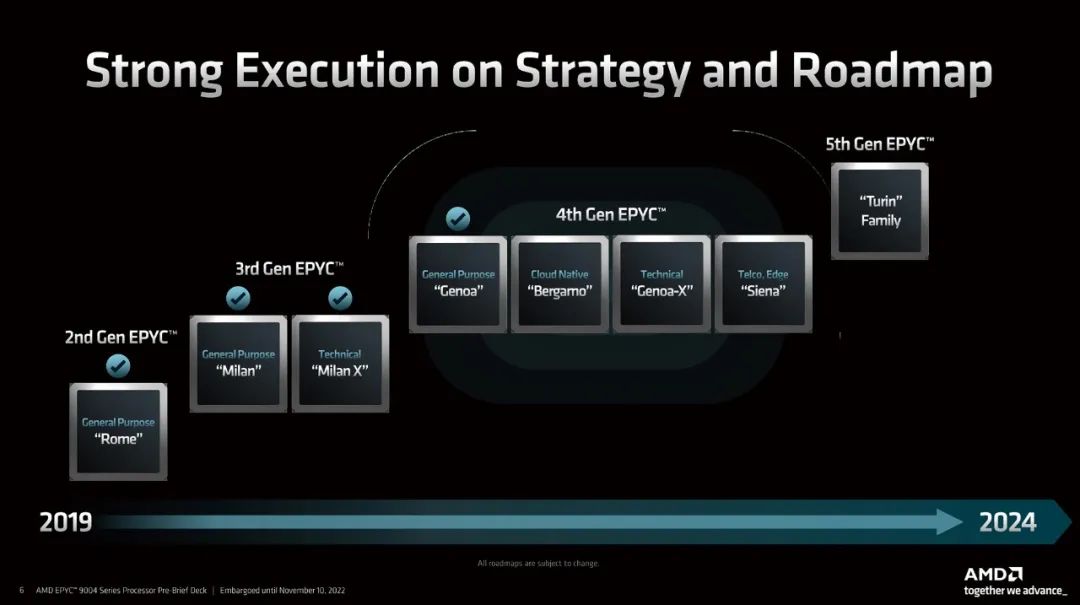

▲AMD EPYC產品路線圖一覽

AMD還給出了EPYC未來的產品路線圖。目前AMD發布的EPYC 9004系列是代號為“Genoa”的產品。接下來,AMD還將陸續推出采用3D V-Cache技術的“Genoa-X”,面向云計算服務的“Bergamo”(貝爾加莫),以及面向電信基礎設施和邊緣計算的“Siena”(錫耶納)。在2023年~2024年,AMD將推出全新設計的Zen 5架構以及第五代EPYC處理器家族,代號“Turin”(圖靈)。AMD在前三代EPYC大獲成功之后,已經開始計劃利用EPYC進入更多市場,繼續和英特爾等廠商展開正面廝殺。這樣的競爭態勢,顯示出AMD強大的進取心。就像全新進化的AMD新品牌平臺 “同超越,共成就 _”(“together we advance_”),持續進步的AMD還會帶給我們怎樣的驚喜呢?一起期待吧!

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論