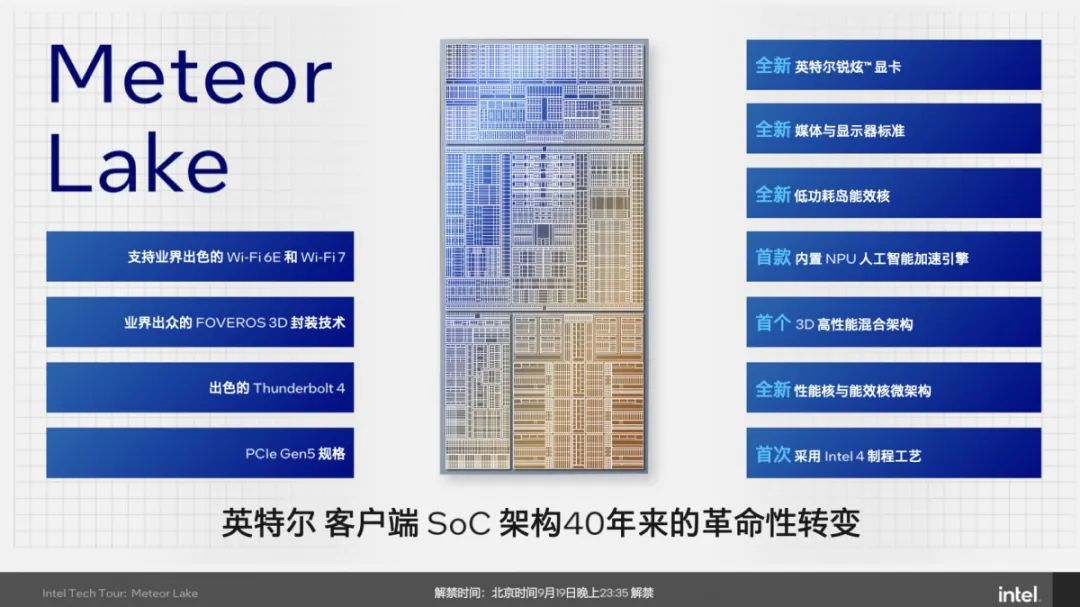

今年Intel Innovation(英特爾on技術(shù)創(chuàng)新大會(huì))應(yīng)該算是場(chǎng)大戲了,尤其是對(duì)PC處理器而言——主要是因?yàn)镸eteor Lake的全面揭曉。我們之前就Meteor Lake的預(yù)先報(bào)道應(yīng)該算是非常多了,包括Intel 4工藝、3D先進(jìn)封裝、微架構(gòu)改進(jìn)等等。

不過代號(hào)為Meteor Lake的這一代酷睿處理器并非14代酷睿。今年年中,Intel就宣布了酷睿(Core)處理器品牌變化,最新的Meteor Lake被稱為酷睿Ultra第1代處理器;而處理器不同SKU也改成了酷睿Ultra 5、Ultra 7和Ultra 9等。

Meteor Lake之所以矚目,我們認(rèn)為關(guān)鍵并不在它表明Intel四年5個(gè)工藝節(jié)點(diǎn)的計(jì)劃順利開展,而是它標(biāo)志著PC處理器基于先進(jìn)封裝chiplet時(shí)代的到來。AMD那邊雖然chiplet方案也用了挺久,但除了3D V-Cache之外,其die與die之間的互聯(lián)方式都很難稱得上“先進(jìn)封裝”。

另外,Intel EMIB、Foveros之類的先進(jìn)封裝技術(shù),雖然此前就已經(jīng)應(yīng)用到了數(shù)據(jù)中心芯片產(chǎn)品上,但在PC處理器上大規(guī)模應(yīng)用還是頭一回。這不僅是對(duì)Intel技術(shù)能力的考驗(yàn),也是PC處理器邁向新時(shí)代的開端。酷睿Ultra的品牌定位重置,應(yīng)該也是基于這樣的變化。

所以在Intel Innovation活動(dòng)之前,Intel就面向媒體做了技術(shù)向的pre-briefing——而且是就CCG業(yè)務(wù)做半導(dǎo)體制造向的技術(shù)科普。不過先期宣講是沒有把重點(diǎn)放在酷睿Ultra產(chǎn)品層面的,而是把大部分精力放在了chiplet、先進(jìn)封裝,和大框架的結(jié)構(gòu)上。(最新消息是,新一代酷睿Ultra處理器產(chǎn)品預(yù)計(jì)要到12月14日發(fā)布)

我們基于這部分信息,來率先看一看這顆將要應(yīng)用Intel 4制造工藝,并且全面開啟PC平臺(tái)基于先進(jìn)封裝chiplet時(shí)代的電腦處理器。

值得一提的是,由于Meteor Lake處理器新增了名為NPU的AI加速器,有關(guān)AI的部分,我們會(huì)另外撰文探討(點(diǎn)擊這里查看)。Intel 4制造工藝及Foveros先進(jìn)封裝部分,本次有一些內(nèi)容更新,也將單獨(dú)成文(點(diǎn)擊這里查看);

后續(xù)Intel Innovation活動(dòng)期間若有更多酷睿Ultra處理器產(chǎn)品層面的信息更新,我們也將再行撰文報(bào)道。本文主要談?wù)凪eteor Lake的關(guān)鍵技術(shù)信息,這些內(nèi)容對(duì)PC和技術(shù)愛好者而言,應(yīng)該都是一場(chǎng)難得的盛宴。

總覽Meteor Lake的chiplet設(shè)計(jì)

Meteor Lake是Intel接下來即將推向PC市場(chǎng)的新一代酷睿Ultra處理器,大方向上采用Intel 4制造工藝,并融合了先進(jìn)封裝技術(shù)。Meteor Lake芯片層面,目前已知的幾個(gè)核心處理器模塊包括了CPU、GPU、NPU,IO支持包括雷電4、USB 4、PCIe 5、WiFi 7、藍(lán)牙5.4等。

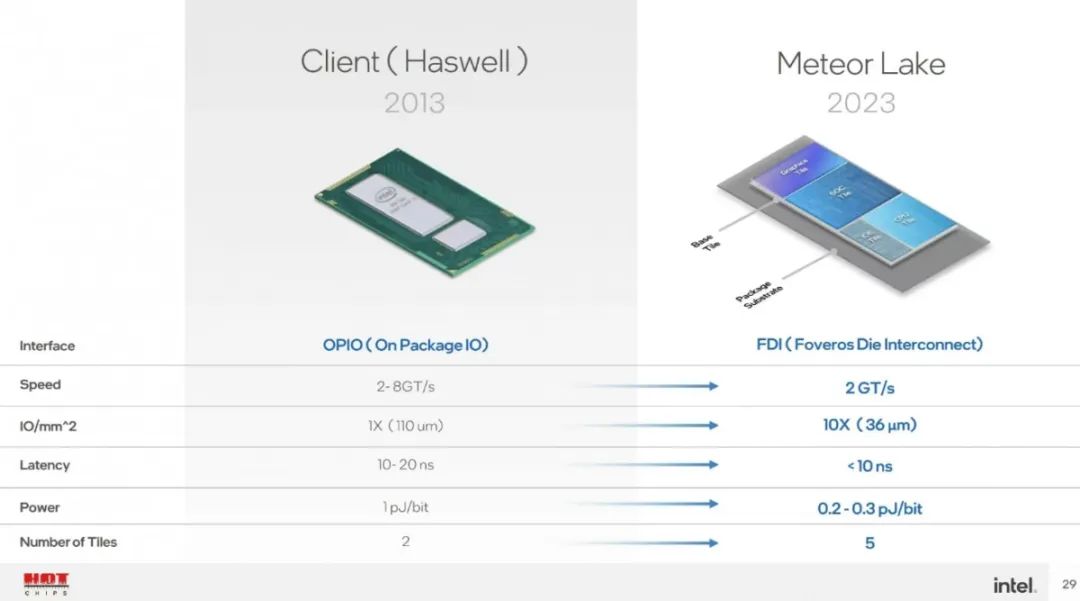

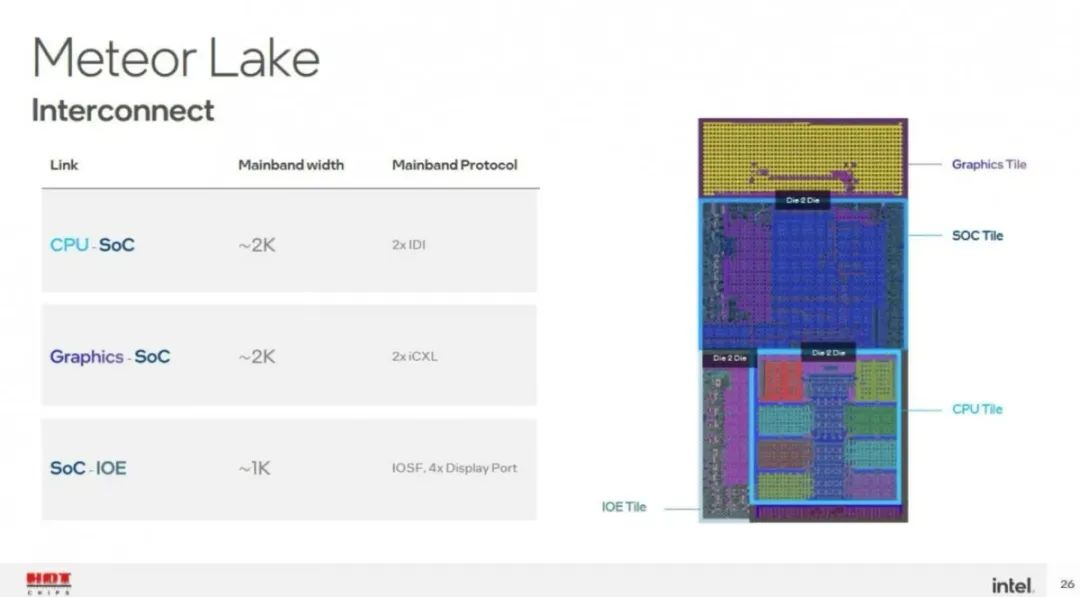

去年Hot Chips 34期間,我們就Meteor Lake的chiplet設(shè)計(jì)做過了比較詳細(xì)的解讀——就先進(jìn)封裝層面的詳細(xì)信息,包括die間通信功耗、協(xié)議、帶寬等,推薦閱讀這篇文章。

而有關(guān)chiplet和先進(jìn)封裝技術(shù)本身,這兩年電子工程專輯的封面故事都花很多篇幅去聊過(《先進(jìn)封裝的現(xiàn)在和將來,價(jià)值鏈的未來重心》《這次不說chiplet的好,來談?wù)刢hiplet的“壞”》)。

簡(jiǎn)單來說,隨著晶體管微縮的速度放緩,以及半導(dǎo)體尖端制造工藝成本的增加,外加芯片制造面臨reticle limit之類的限制,高性能計(jì)算領(lǐng)域的芯片面積,已經(jīng)大到無法用單die去解決的程度。

而chiplet就把一顆設(shè)想中很大的die,切成很多小片die,每片小die都叫做一個(gè)chiplet。而先進(jìn)封裝,就是通過更為密集的I/O互聯(lián)間距,將這些小die“縫合”起來,封裝到一起成為一整顆芯片。

Meteor Lake就是基于這種思路的產(chǎn)物——而且未來很長(zhǎng)一段時(shí)間的酷睿處理器產(chǎn)品,不出意外也會(huì)按照這個(gè)思路去走。

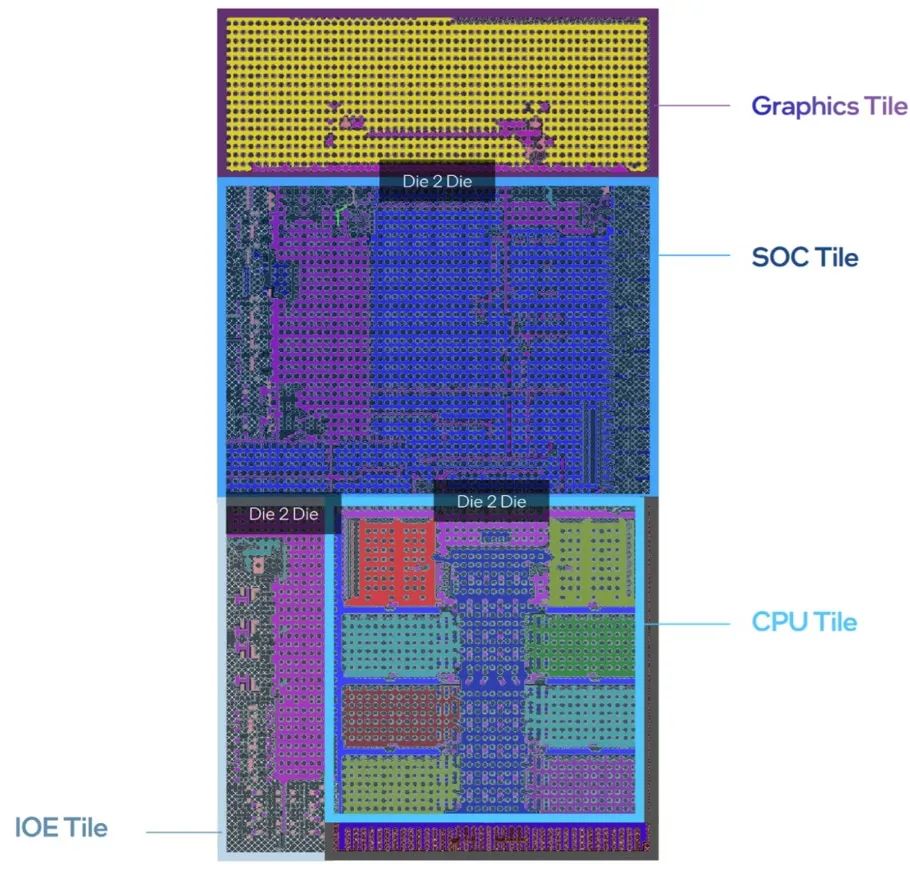

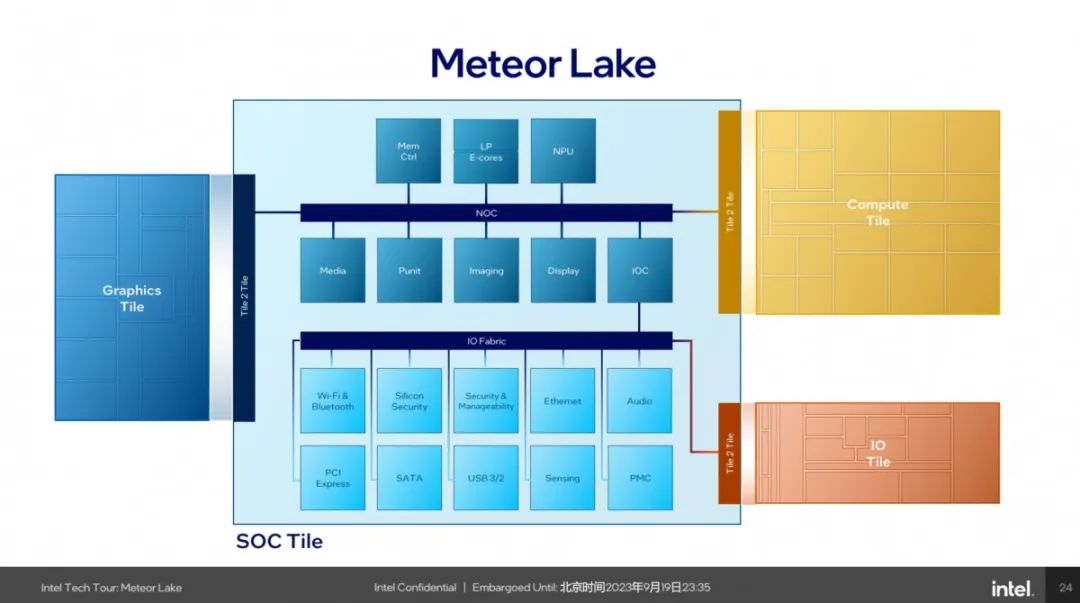

從這次Intel的介紹來看,Meteor Lake依舊分成了Compute tile(上面主要是CPU)、Graphics tile(核顯)、SoC tile(其上包含有低功耗E-core,NPU,WiFi與藍(lán)牙模塊、顯示引擎、DDR內(nèi)存控制器等)、IO tile(主要是PCIe Gen 5與Thunderbolt 4支持實(shí)現(xiàn))。Intel稱其為“tile”,中文譯作“模塊”,實(shí)際上就是chiplet。

此前我們就提過,Intel的chiplet思路和隔壁AMD的差異還是比較大的。不過從介紹來看,Intel這種模塊化設(shè)計(jì)的靈活度,在劃分不同SKU,及未來性能和架構(gòu)擴(kuò)展和進(jìn)化方面會(huì)提供極大的幫助。

Intel在介紹中提到,Meteor Lake的核心設(shè)計(jì)理念包括(1)性能功耗效率提升;(2)首次將NPU集成到PC處理器;(3)集顯性能飛躍;(4)采用Intel 4制造工藝。

這里的采用Intel 4制造工藝,主要是指Compute tile部分用的是Intel 4——畢竟chiplet的靈活性之一,就體現(xiàn)在不同的chiplet可以用不同的工藝。而且Meteor Lake的其中某些die應(yīng)該是臺(tái)積電造的,也體現(xiàn)了IDM 2.0策略。

CPU部分:新增一種低功耗E-core

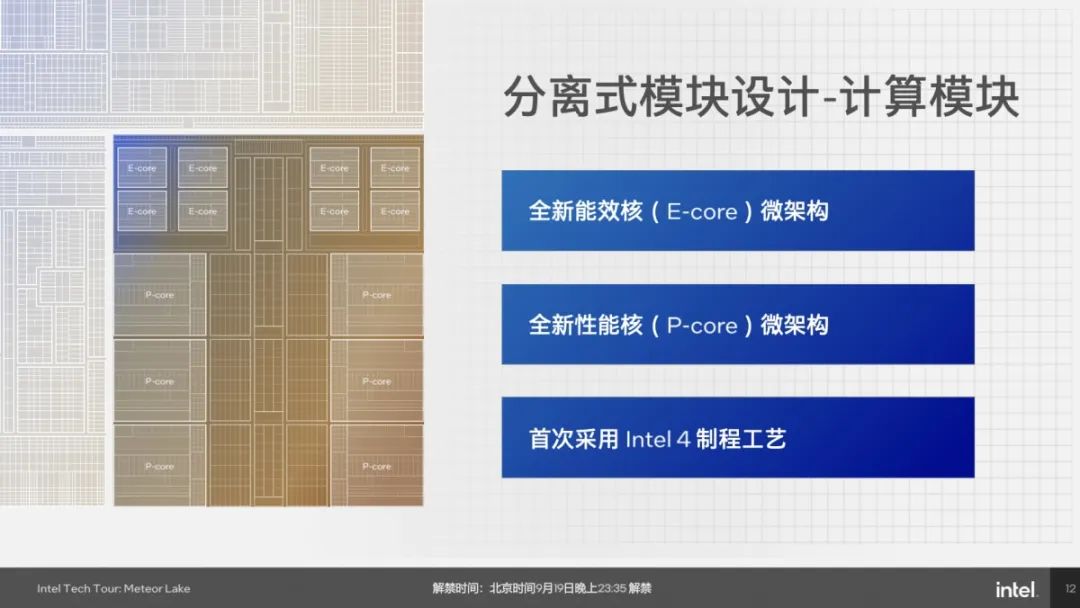

Intel從12代酷睿(Alder Lake)開始,CPU部分就采用異構(gòu)設(shè)計(jì)了,即包含P-core性能核、E-core能效核兩種不同架構(gòu)的核心設(shè)計(jì)。

Meteor Lake的CPU部分主要位于Compute tile之上——示意圖給出的是6+8的方案,6顆P-core,以及4核心一組的E-core總共8個(gè)核心,和ring fabric環(huán)形總線。其實(shí)就截止發(fā)稿前,我們還并不清楚在酷睿Ultra產(chǎn)品層面,這代處理器的具體配置如何,包括核心數(shù)、頻率等。這個(gè)部分后續(xù)還會(huì)單獨(dú)刊文報(bào)道。

目前就CPU部分了解到的信息是,P-core代號(hào)Redwood Cove,E-core代號(hào)Crestmont。但這并非Meteor Lake的全部。

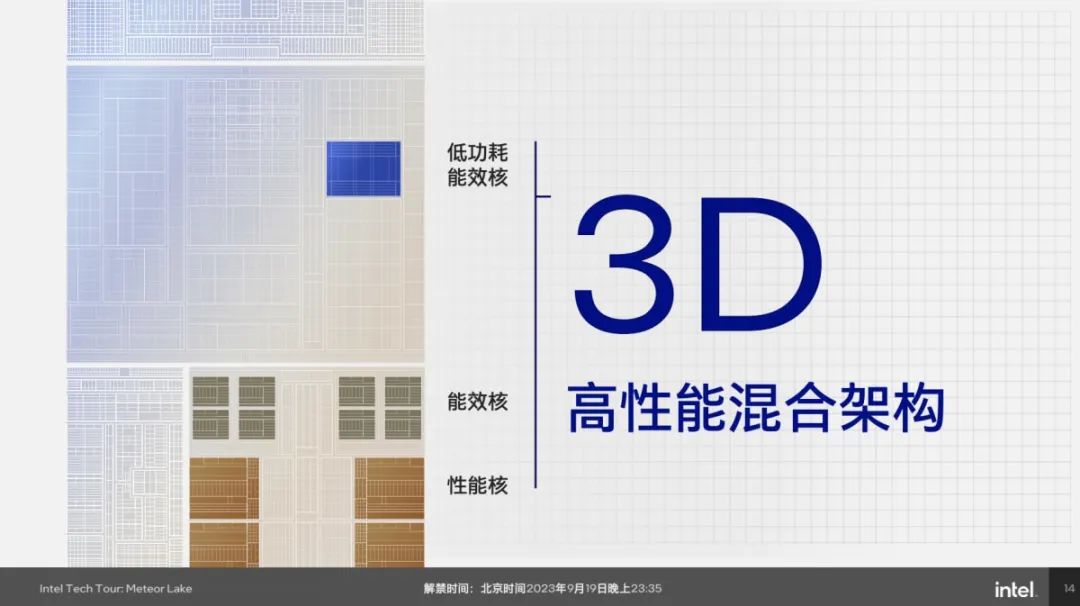

在SoC tile上,Intel還額外給了兩顆Low Power E-core(以下簡(jiǎn)稱LP E-core)。

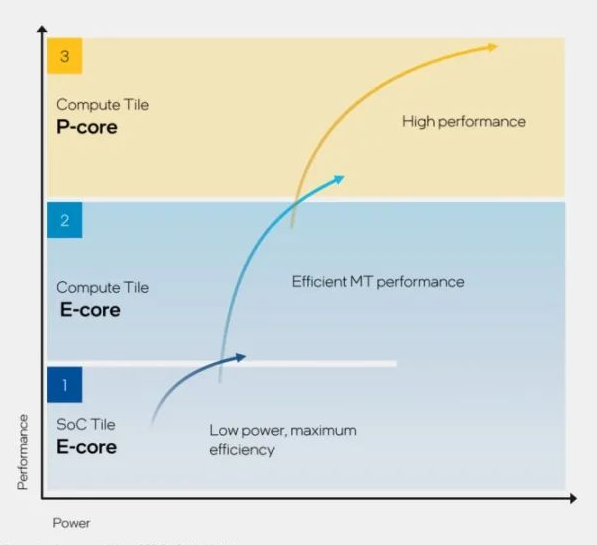

截至發(fā)稿前,暫不清楚這兩顆單獨(dú)的E-core在架構(gòu)層面,是否與Compute tile上的E-core一致。猜測(cè)應(yīng)該是不同的,因?yàn)樵诮榻B調(diào)度策略時(shí),Intel給出這種類似三叢集架構(gòu)(Intel稱其為3D性能混合架構(gòu))的功耗與性能關(guān)系,大致如下圖:

這張圖畫的還是相當(dāng)隨意,但總體都是在表達(dá)不同核心集群,負(fù)責(zé)不同性能和功耗區(qū)間的工作,以達(dá)成最高的能效。記得此前Arm說自己是全球唯一在做3-cluster核心CPU設(shè)計(jì)的企業(yè),這會(huì)兒Intel也是了。..

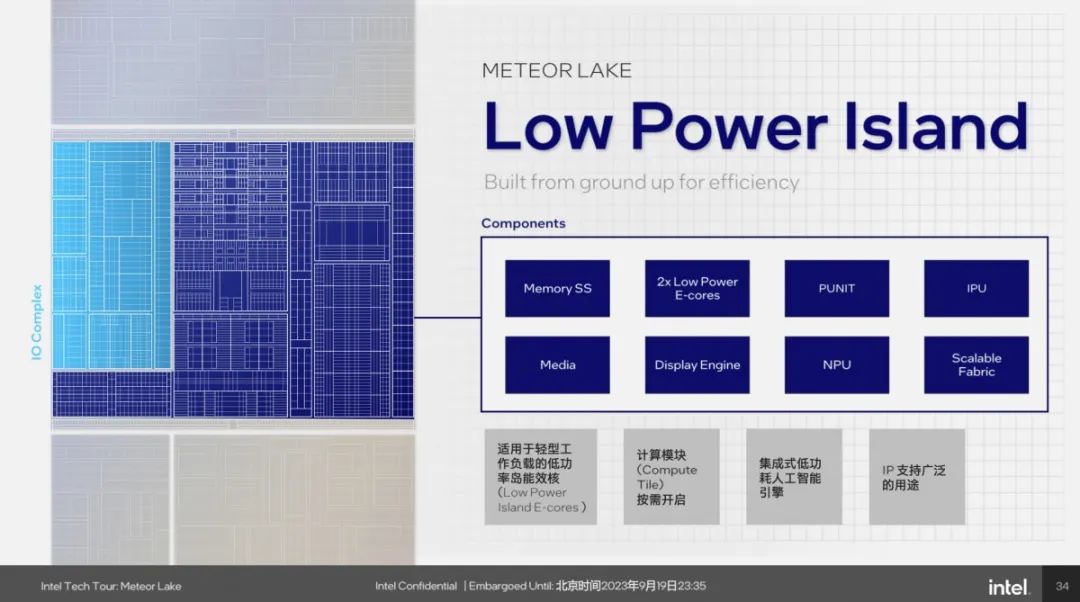

LP E-core所在的SoC tile(或其中一部分)似乎是被Intel稱作為“Low Power Island”(低功耗島)的,也不光是因?yàn)閮深wLP E-core,還在于其他模塊——這個(gè)我們放到后文去談。

不過Intel在介紹中提到,很多情況下“只要SoC tile是活著的,工作就可以繼續(xù);而Compute tile、Graphics tile都可以掛起睡眠或進(jìn)入超低功耗模式,甚至關(guān)閉。”“保證在不損失性能的情況下,在大部分時(shí)間里,都讓整個(gè)package處于非常低功耗的狀態(tài)”。

Intel在舉例中提到了類似IT后臺(tái)工作,大部分情況下可以交給LP E-core去跑。在需要性能和響應(yīng)速度時(shí),再切往E-core和P-core。

這種3集群的結(jié)構(gòu),實(shí)際上會(huì)給調(diào)度提出更高的要求。考慮到自12代酷睿起,P-core + E-core的兩集群異構(gòu)設(shè)計(jì),在某些場(chǎng)景下就存在調(diào)度問題,這次的Meteor Lake對(duì)Intel和微軟而言都會(huì)是相當(dāng)大的技術(shù)挑戰(zhàn)。

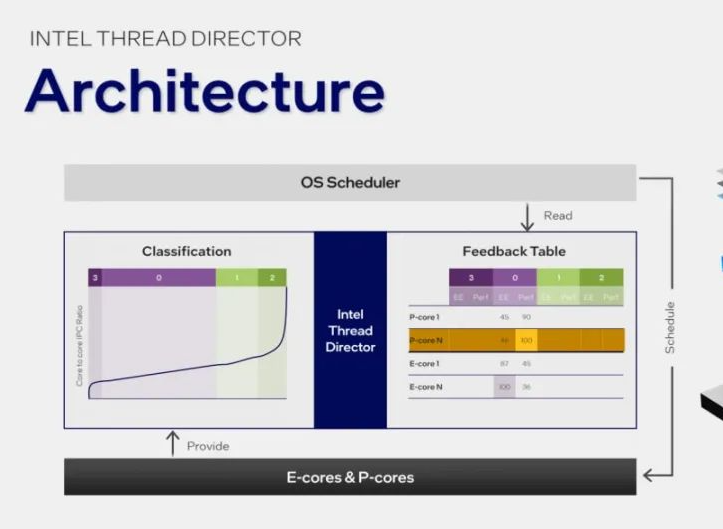

所以在媒體會(huì)上,Intel又花較大篇幅去談了Intel Thread Director(以下簡(jiǎn)稱ITD)。這個(gè)ITD是在Intel發(fā)布12代酷睿時(shí),也同期發(fā)布的、輔助操作系統(tǒng)做調(diào)度決策的機(jī)制——它介于CPU與操作系統(tǒng)scheduler之間,給予scheduler以hint,或者說建議。

這次Intel好像對(duì)Thread Director做了大改——起碼從介紹來看是如此:我們來大致了解一下現(xiàn)在的ITD機(jī)制:

上圖左邊classification,不同的class代表不同類型的指令或工作。縱坐標(biāo)代表不同集群核心的IPC(每周期執(zhí)行指令數(shù))比值。比如說對(duì)于class 0而言,P-core與E-core的情況基本類似(大部分指令落在這個(gè)區(qū)間內(nèi));而class 1部分則代表,P-core執(zhí)行此類指令的IPC將大于E-core;class 2顯然是P-core的IPC遠(yuǎn)高于E-core;class 3則是相反的。

右邊這張圖,則就每一類class,針對(duì)不同的核心,有EE(energy efficiency,能效)與Perf(性能)兩個(gè)打分。得分最高的,就將該核心推薦給OS scheduler。就像上面這張圖,就class 0,若追求性能,則ITD傾向于推薦P-core N,而若追求能效,則推薦E-core N。

這張表是動(dòng)態(tài)更新的,基于功耗、發(fā)熱等情況發(fā)生變化;“主打一個(gè)當(dāng)有其他IP占用power budget時(shí),做動(dòng)態(tài)的評(píng)估和判斷”;還有像是基于SoC運(yùn)行時(shí)間能力做更新等。比如Intel舉例中,存在有時(shí)class 0指令,無論從性能還是能效維度考量,都推薦E-core的情形。“在正確的時(shí)間讓正確的線程跑在正確的core上”。

Intel針對(duì)這一代ITD的總結(jié)還包括面向操作系統(tǒng)增強(qiáng)的feedback和更智能的hint,以及基于“系統(tǒng)運(yùn)行模式、硬件特征”等,都“納入到控制邏輯里面來”。

Intel在媒體會(huì)上舉了個(gè)比較抽象的調(diào)度案例。比如說有個(gè)高資源占用的前臺(tái)app跑起來,有4個(gè)進(jìn)程跑在P-core上;然后有個(gè)低資源占用的app跑了2條線程在E-core上;在高資源占用app跑完以后,若兩個(gè)輕載線程還在跑,則ITD會(huì)建議操作系統(tǒng)將它們搬到LP E-core核心,讓Compute tile整體閑置,以節(jié)約能耗。

其實(shí)當(dāng)工作負(fù)載很復(fù)雜時(shí),全流程仍然相當(dāng)考驗(yàn)Intel和微軟的功力。這種3集群設(shè)計(jì),在理想情況下可以做到低功耗、高能效;但如果不理想,則會(huì)對(duì)體驗(yàn)產(chǎn)生很大影響(而且LP E-core現(xiàn)在是在不同的die上,不知道線程遷移的延遲會(huì)不會(huì)因此大幅增加)。具體就看產(chǎn)品發(fā)布后的實(shí)際情況了,畢竟這方面的工作Arm也是和谷歌協(xié)調(diào)了好多年才走向成熟的。

GPU:核顯性能翻番、支持光追

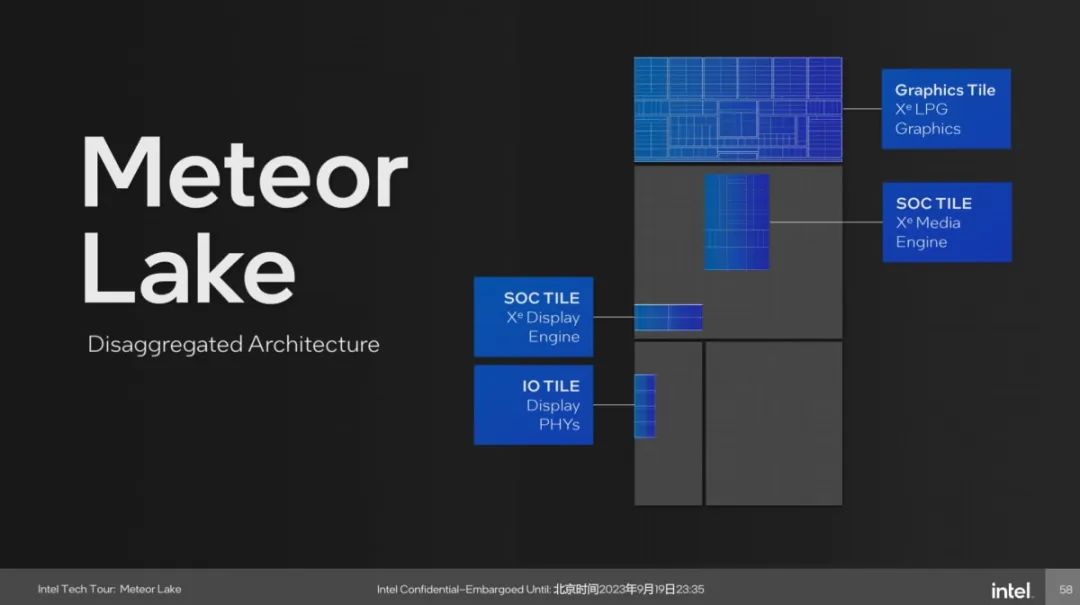

接下來聊一聊Graphics tile上的核顯,以及SoC tile上的媒體與顯示引擎(另顯示的PHY部分是放在了IO tile上的,如下圖)。以前,這三者習(xí)慣上我們總是放在一起聊的。

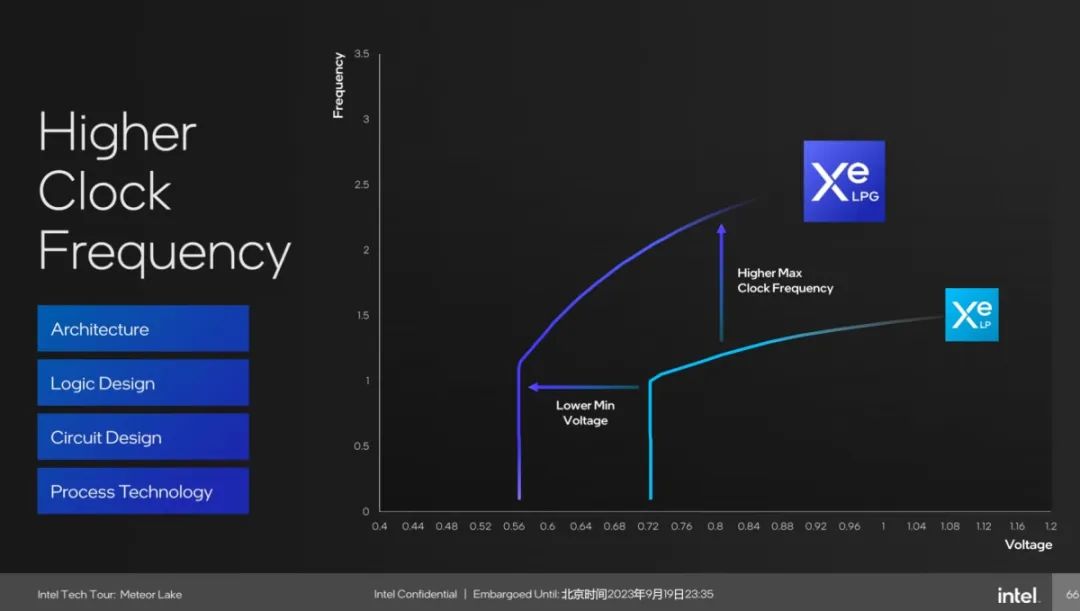

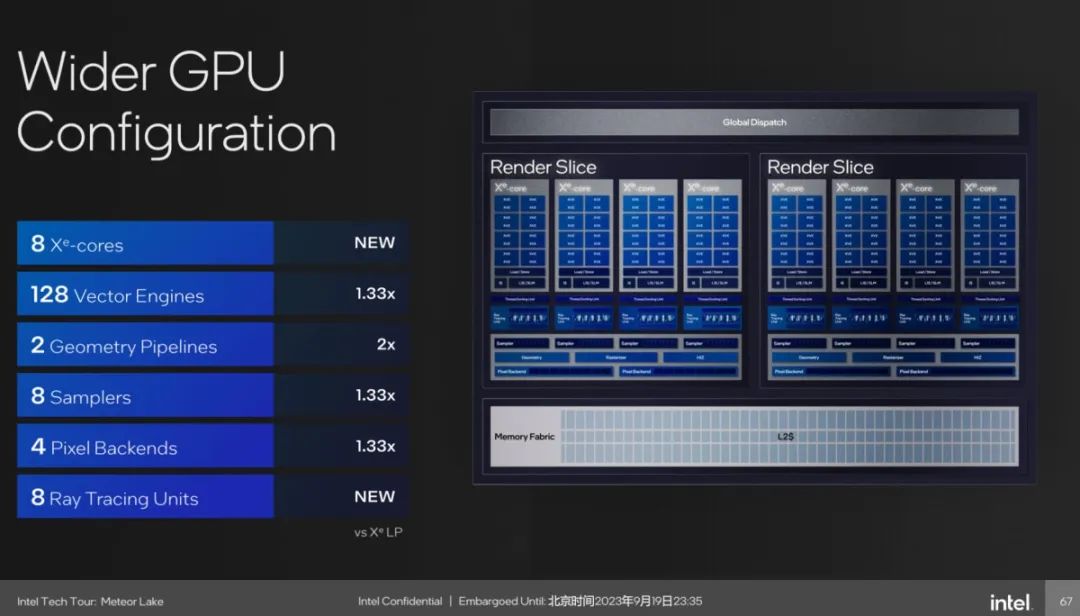

從總體上來看,Intel說這次的Xe核顯吸取了Arc獨(dú)顯方面的技術(shù)積累和經(jīng)驗(yàn);新版的Xe-LPG相比于前代Xe-LP,性能和能效(Perf/watt)都實(shí)現(xiàn)了翻番;而且新增了一些DirectX 12 Ultimate特性,新增光線追蹤(8個(gè)RTU)支持,兩倍速率HiZ,異步拷貝(Async Copies),以及亂序采樣(Out of Order Sampling)。

這里面的確有許多特性是繼承自Xe-HPG獨(dú)顯。具體架構(gòu)層面的變化,媒體分享會(huì)上并沒有詳談——據(jù)說有互聯(lián)、cache方面的優(yōu)化。從Intel提供的PPT來看,這一代Xe-LPG相比前代的Xe-LP,主要是提高了主頻、擴(kuò)大了規(guī)模、提升了架構(gòu)效率。

提頻依賴于架構(gòu)、邏輯與電路設(shè)計(jì),以及工藝進(jìn)化(雖然不知道Graphics tile是否基于Intel自己的Intel 4)。

而在規(guī)模擴(kuò)大的問題上,從下面這張架構(gòu)框圖來看,跟Xe-HPG的Render Slice的確還挺像的(只不過似乎還是沒有XMX)。

核顯總體規(guī)模就是8個(gè)Xe核心,總共128個(gè)矢量引擎——相比上代的96EU提升了33%;geometry管線達(dá)成雙倍拓寬;sampler和pixel backends都有對(duì)應(yīng)提升。按照Intel所說相比前代2倍圖形性能提升,矢量引擎數(shù)字提升卻沒有這么多,還是能看出整體架構(gòu)上的優(yōu)化的。

當(dāng)然每個(gè)Xe核心對(duì)應(yīng)的有一個(gè)光線追蹤單元,看來往后光追是真的要普及了。Intel在酷睿Ultra處理器核顯上,將RTU作為標(biāo)準(zhǔn)件推廣,對(duì)于其自身的光追和圖形生態(tài)發(fā)展也相當(dāng)有好處。不過基于Embree的Blender光追性能測(cè)試提升,Intel給的提升數(shù)據(jù)是相比CPU渲染提升2.5倍左右的性能,其實(shí)就光追部分來看還是挺弱的。

但如果說整體圖形性能真的達(dá)成了2倍提升(假定是3DMark這類benchmark成績(jī)提升100%),而且存儲(chǔ)不成為瓶頸,那么隔壁“大核顯”就可以被比下去了。則明年用輕薄本全面玩游戲,的確還是可以期待一下。

有關(guān)圖形部分,這里其實(shí)還有個(gè)問題,我們此前提過,即以往的酷睿處理器都是monolithic的SoC,核顯都是掛在環(huán)形總線上,甚至還能享用LLC的。Meteor Lake顯然就不能再這么做了,因?yàn)镚raphics tile都獨(dú)立了,和Compute tile中間還隔著個(gè)SoC tile。

此前我們就分析過,這么做可能實(shí)際造成的性能負(fù)面影響很有限(因?yàn)閳D形的cache hit rate原本就很低);而且這么做對(duì)整體系統(tǒng)功耗的降低,似乎還有相當(dāng)大的幫助,后文談uncore的部分會(huì)提及這一點(diǎn)。

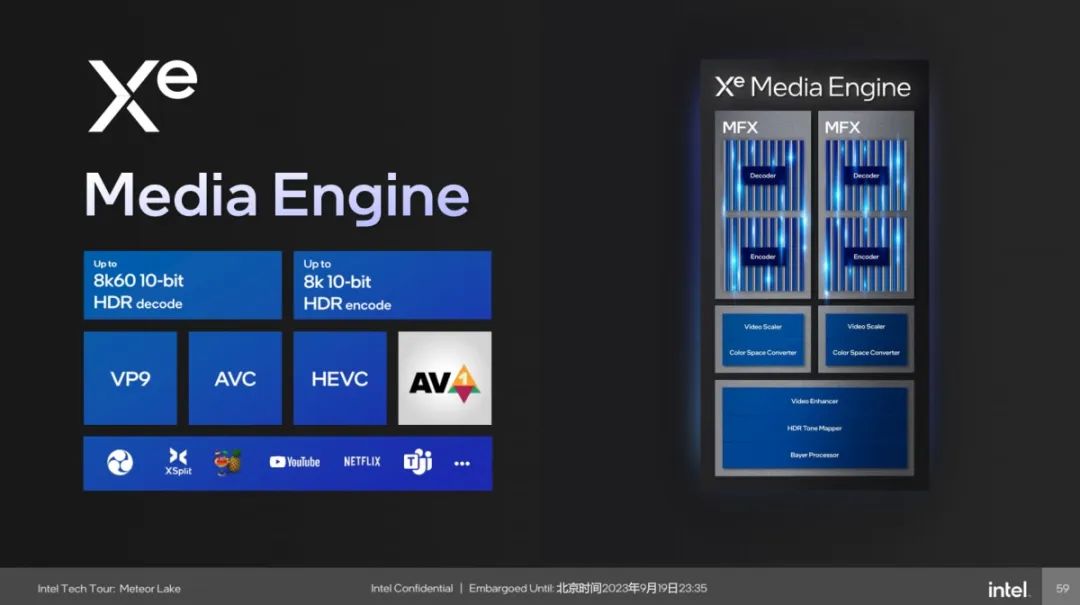

此外,Xe顯示引擎、媒體引擎主要都位于SoC tile上,并沒有放在Graphics tile上。媒體引擎支持最高8k60 10bit HDR解碼,8k30 10bit HDR編碼;格式方面,主流的VP9, AVC, HEVC, AV1都有支持。

顯示引擎部分,Intel強(qiáng)調(diào)做了功耗方面的優(yōu)化;全路徑(optimized end to end unified compression)壓縮,“當(dāng)遇到顯示輸出與分辨率不匹配時(shí),壓縮提供了很不錯(cuò)的輸出能力,功耗也控制得非常好”;低功耗模式,“降低對(duì)CPU、內(nèi)存、圖形方面的資源需求”。

顯示連接支持HDMI 2.1, Display 2.1, eDP 1.4;輸出最高8k60 HDR, 4x 4k60 HDR, 或者1080p/1440p 360Hz。

為低功耗而生的SoC tile

前面談到媒體引擎、顯示引擎主要都是放在了SoC tile上的;SoC tile上另外還有LP E-core、NPU、內(nèi)存控制器、IPU,以及包括對(duì)USB、Ethernet、WiFi 6E/7、藍(lán)牙等的支持。另外,IO tile部分主要是實(shí)現(xiàn)PCIe Gen 5和Thunderbot 4支持(似乎此種架構(gòu)下,也就沒有了PCH的概念——其實(shí)以前的PCH+CPU,也屬于多die方案,只不過嚴(yán)格意義上不屬于先進(jìn)封裝)。

這種Chiplet式的模塊化設(shè)計(jì),不僅是讓不同chiplet得以用最適配的工藝來制造,而且也確實(shí)某種程度上達(dá)成了不同模塊的解耦,包括未來要對(duì)顯示、媒體、imaging成像(IPU),或者PCIe和Thunderbolt支持做加強(qiáng),會(huì)更便利。Intel說這種架構(gòu)思路,會(huì)影響到未來數(shù)代CPU架構(gòu)設(shè)計(jì)。

其實(shí)這種設(shè)計(jì)的關(guān)鍵還在于die間通信帶寬、功耗、延遲。Intel在宣傳中說Foveros技術(shù)具備高密度(單位面積線數(shù))、高帶寬、低延遲、簡(jiǎn)單、高能效的特點(diǎn),但這次沒給具體的數(shù)字。去年的Hot Chips上Intel給過一組數(shù)據(jù),量級(jí)上可供各位同學(xué)參考:

不過其實(shí)SoC和IO tile的設(shè)計(jì),還是挺有講究的。就邏輯框圖來看,SoC tile位于整個(gè)Meteor Lake芯片的中間位置,上承Graphics tile,下接Compute tile和IO tile。Die與die之間有專門的高速互聯(lián)總線(Foveros Die Interconnect,不同die之間基于不同的通信協(xié)議)。

從上圖來看,SoC tile內(nèi)部有兩條總線,“北邊的是NOC(network on chip),特性是高帶寬、快速響應(yīng),能夠讓掛在上面的設(shè)備快速、低功耗地訪問memory”。前文著重提到的LP E-core、顯示與媒體引擎、NPU,乃至Compute tile和Graphics tile都掛在NOC上。

“南邊的是IO Fabric”,IO tile、PCIe、USB,以及SoC tile內(nèi)部的Audio、Ethernet、WiFi藍(lán)牙都掛在IO Fabric上。這部分還有兩個(gè)相關(guān)安全的組成部分,Silicon Security和Security & Managebility Engine(CSME),分別是silicon level和platform level的安全控制。

就不同tile的定位,Intel在宣傳中對(duì)Graphics tile的描述是“為3D性能做優(yōu)化”,對(duì)Compute tile的描述則為“為CPU性能做優(yōu)化”——這兩樣都很好理解。而SoC tile描述為“為功耗做優(yōu)化”。

SoC tile(或其中一部分)又被Intel稱作Low Power Island低功耗島。其實(shí)不光是因?yàn)長(zhǎng)P E-core位于其上,還包括集成DLVR、動(dòng)態(tài)的內(nèi)部總線頻率調(diào)節(jié)、基于負(fù)載的性能調(diào)節(jié)SoC算法、和前文提及ITD線程調(diào)度等特性。

而SoC tile實(shí)現(xiàn)低功耗的根本原因或許還在下面。

Uncore設(shè)計(jì),為將來打基礎(chǔ)

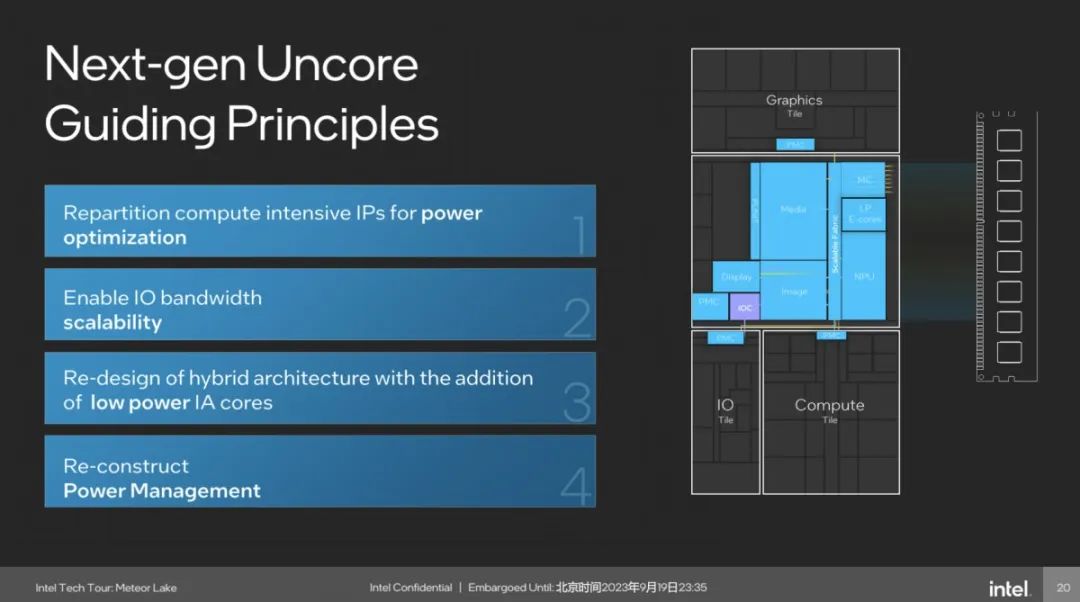

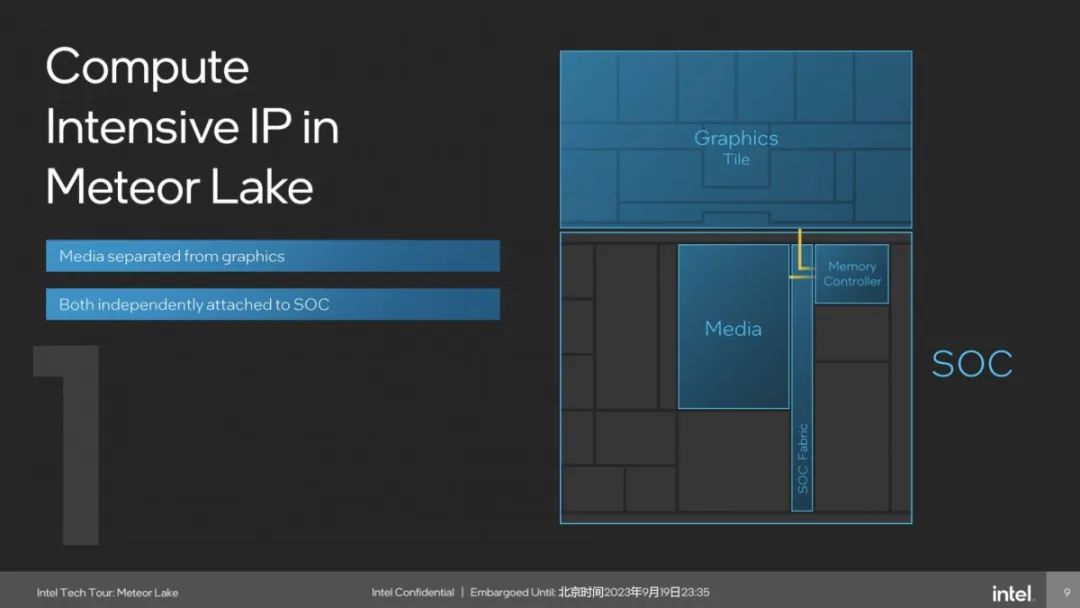

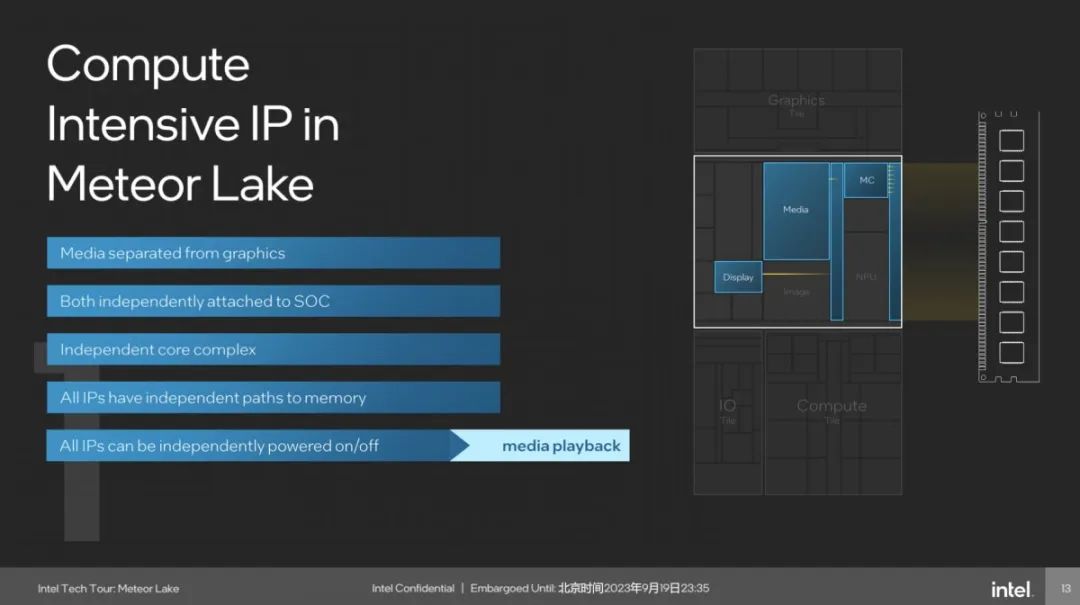

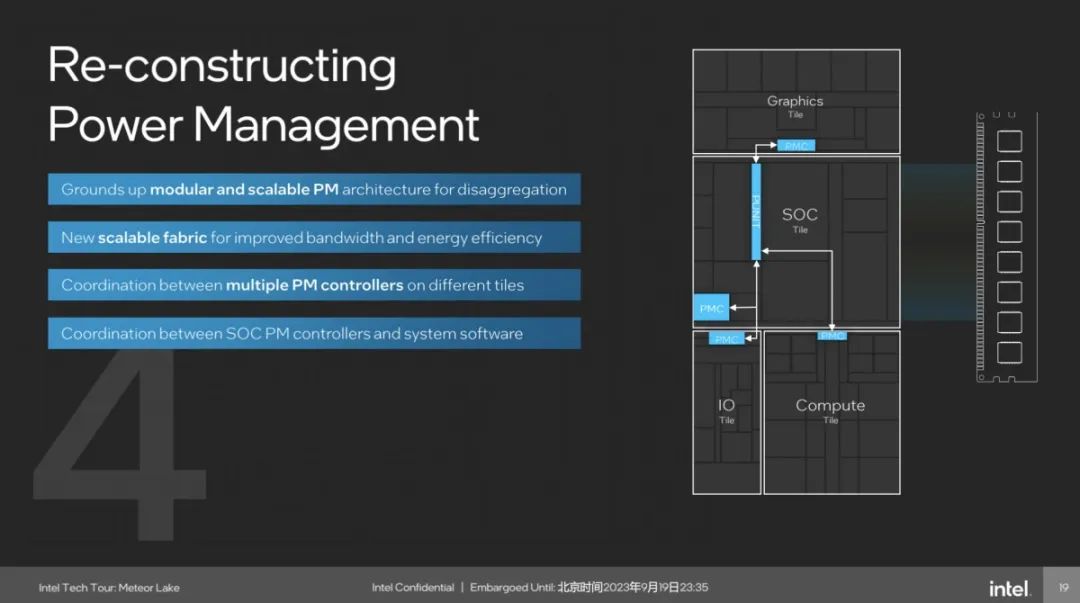

有關(guān)SoC tile,及其中相關(guān)uncore的部分,在于踐行低功耗、高能效理念過程里,這部分存在的價(jià)值。Intel花了不少篇幅去談uncore的設(shè)計(jì)指導(dǎo)原則——也可能成為未來酷睿處理器設(shè)計(jì)的基礎(chǔ):包括第一,對(duì)計(jì)算密集型IP的重新劃分,實(shí)現(xiàn)功耗優(yōu)化;第二,IO帶寬可擴(kuò)展;第三,引入低功耗核心(即LP E-core);第四,重組電源管理設(shè)計(jì)。

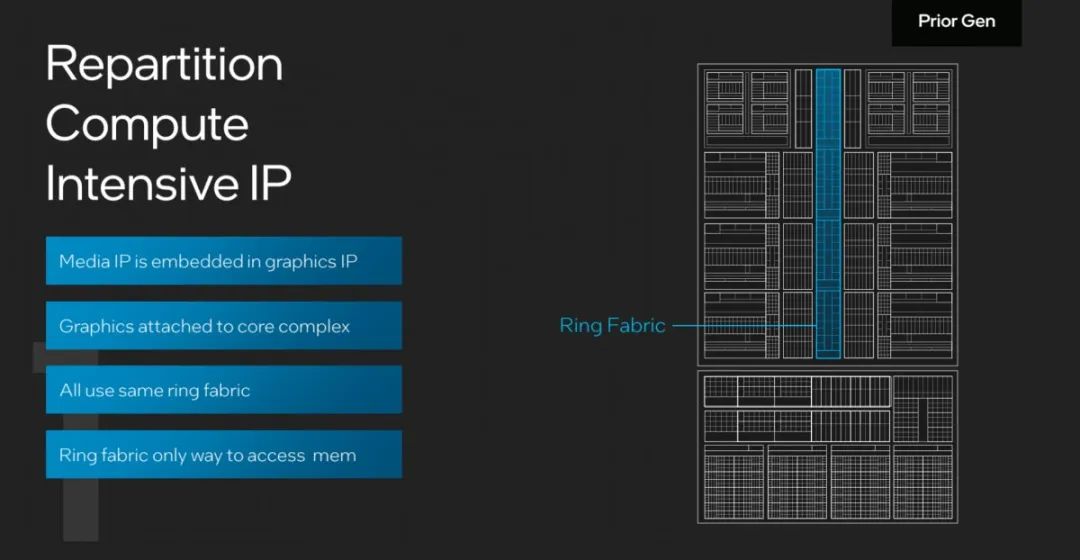

我們一個(gè)個(gè)來看。首先是“計(jì)算密集型IP重新劃分”——大致上體現(xiàn)在幾個(gè)方面,過去monolithic時(shí)代的酷睿處理器設(shè)計(jì),媒體編解碼器是和核顯(graphic IP)是放在一起的;而核顯則掛在LLC(L3 cache)上——前文也提到了這一點(diǎn)。下面這張圖展示了ring fabric將這些IP串起來。

“任何一個(gè)CPU core,或者graphic(核顯),或者media(媒體引擎)要訪問內(nèi)存,就會(huì)藉由ring總線,通過system agent(系統(tǒng)代理),到達(dá)內(nèi)存。對(duì)內(nèi)存訪問而言,這是非常高性能的解決方案。”以往很多代的酷睿處理器即是這么做的。

這種設(shè)計(jì)存在一個(gè)問題,即ring總線上的任何一環(huán)需要訪問內(nèi)存時(shí),“包括ring、core complex、graphic等邏輯單元就都需要激活”——Intel在介紹中說,對(duì)于具體的應(yīng)用而言,這種操作是沒有必要的。最終結(jié)果就是功耗更高。

比如說只是流媒體播放的話,media IP對(duì)memory做訪問,就要把整個(gè)ring都開啟。那么為了解決這個(gè)問題,前文已經(jīng)提到Meteor Lake的核顯部分是單獨(dú)位于Graphics tile的;媒體引擎則位于SoC tile;CPU核心主要位于Compute tile。也包括內(nèi)存控制器,“它們都有自己獨(dú)立的、在SoC總線上面attach的位置。”如下圖。

“無論graphics,media,還是compute core,要對(duì)內(nèi)存做訪問時(shí),不需要其他部分供電。”比如上面這張圖展示媒體引擎工作,與內(nèi)存控制器、顯示引擎之間通訊即可,其余部分是可以關(guān)閉的。那么在進(jìn)行視頻播放時(shí),功耗自然就能得到降低。

不過Intel并未給出有關(guān)這能帶來多大程度功耗降低的具體數(shù)據(jù)(這一點(diǎn)其實(shí)很重要)。或許這將有助于筆記本的日常使用場(chǎng)景下,降低低負(fù)載下的系統(tǒng)功耗水平——這其實(shí)一直以來都是Intel PC處理器的一大頑疾。

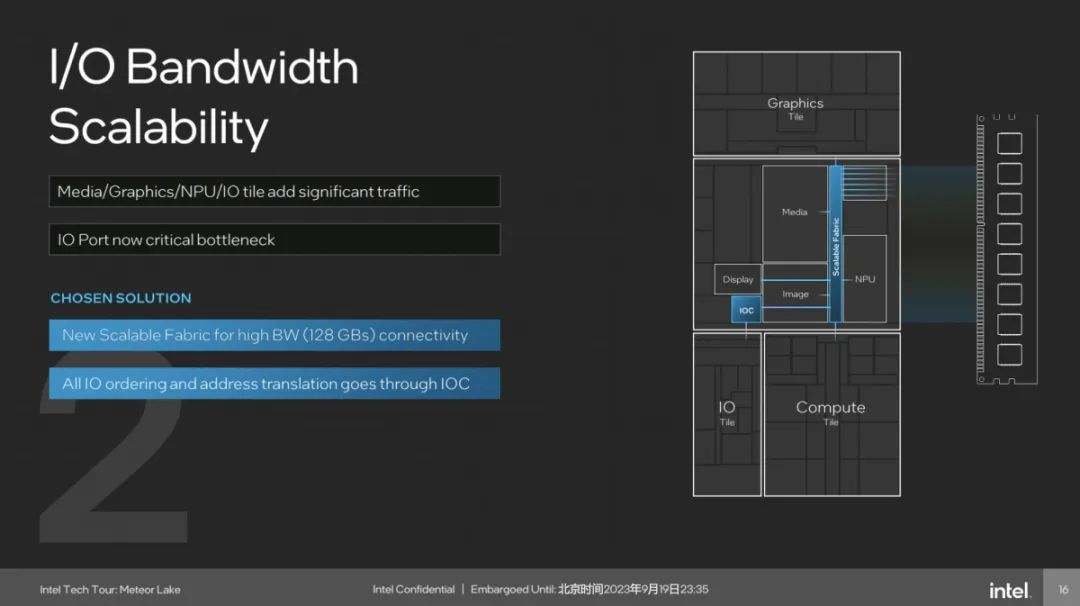

此外,談到uncore的第二個(gè)設(shè)計(jì)理念,是IO帶寬可擴(kuò)展,用以支持SoC內(nèi)部所有模塊對(duì)于帶寬的需求。尤其由于部分新IP的引入,則沿用過去的方案就會(huì)造成內(nèi)部IO的瓶頸和流量擁塞。

“碰到帶寬問題,常規(guī)解決辦法是制定優(yōu)先級(jí),為一些IP創(chuàng)建高優(yōu)先級(jí)。過去我們就是這么做的。但現(xiàn)在由于新IP的引入和劃分,Meteor Lake不能再沿用老的設(shè)計(jì)方式。”“所以我們針對(duì)SoC做了全新的帶寬擴(kuò)展,適配SoC內(nèi)部所有IP對(duì)帶寬的需求,消除SoC中IP與IP、IP與總線、IO之間的通信瓶頸。”

“同時(shí),我們還添加了IO緩存塊。”應(yīng)該是指上圖中的IOC(IO cache?),“來管理傳入IO的量和地址轉(zhuǎn)換,確保維持較好的次序。”雖然其實(shí)就Intel的講解來看,我們沒聽出scalability可縮放特性表現(xiàn)在哪兒,但應(yīng)當(dāng)至少包含了帶寬的增加。

其三,前文也已經(jīng)提到,就是Meteor Lake的混合架構(gòu)在SoC tile上引入了LP E-cores。因?yàn)楫吘共煌琁P之間的交互,還是需要控制、協(xié)調(diào)的。如果這個(gè)時(shí)候要依靠Compute tile上的CPU核心來協(xié)調(diào),顯然是得不償失的。

就這個(gè)角度來看,LP E-core的引入似乎是現(xiàn)有chiplet架構(gòu)下的必行之策。比如用前面的例子來看,進(jìn)行流媒體播放時(shí),LP E-core就能做基本控制,不需要Compute tile參與。

其四,是電源管理設(shè)計(jì)的“重塑”。主要表現(xiàn)為不同的tile,內(nèi)部都有獨(dú)立的電源管理控制器(PMC);而在SoC tile上,又有個(gè)PUNIT,“它跟不同tile上的電源管理控制器溝通,提供實(shí)時(shí)、可擴(kuò)展的電源管理架構(gòu)”,并“和上層的操作系統(tǒng)、軟件協(xié)同工作”。

這又是個(gè)模塊化、可縮放的方案,也是去中心化的組成部分。Intel說這種新架構(gòu)“為Meteor Lake提供了很多電源管理方面新的功能,也為將來芯片設(shè)計(jì)的電源管理,奠定了非常好的基礎(chǔ)”。怪不得Chips and Cheese認(rèn)為Intel的chiplet方案相比AMD的更松散、更靈活。

從Intel的描述來看,uncore的這些設(shè)計(jì)理念,應(yīng)該是Meteor Lake實(shí)現(xiàn)“出色的性能功耗效率”相當(dāng)重要的一環(huán);同時(shí)也是后續(xù)進(jìn)一步達(dá)成低功耗的探索和基礎(chǔ)。所以媒體分享會(huì)上,Intel說了好幾次Meteor Lake是“Intel歷史上能效最高的客戶端處理器”。雖然可能在大部分用戶看來,這是一句正確的廢話。

最后總結(jié)一下Meteor Lake的要點(diǎn),如上圖所述。(1)核顯性能2倍提升并支持光追;(2)新增SoC tile上的LP E-core,作為更高能效比及更低功耗區(qū)間段的第三個(gè)集群,加入到了CPU核心中;(3)新增NPU加速單元;(4)采用Intel 4制造工藝,與Foveros 3D先進(jìn)封裝技術(shù)。

有關(guān)NPU部分點(diǎn)擊這里查看;Intel 4工藝與Foveros先進(jìn)封裝技術(shù)更多信息則點(diǎn)擊這里查看。

很難得的,本文沒談CPU核心微架構(gòu),光在封裝級(jí)的系統(tǒng)設(shè)計(jì)層面打轉(zhuǎn)就已經(jīng)耗費(fèi)了將近7000文字。怪不得這兩年大家都在說,摩爾定律停滯之際,芯片設(shè)計(jì)的復(fù)雜性是往后端和系統(tǒng)層面進(jìn)一步傾斜了。

感覺要一次完成這么多工作,應(yīng)該會(huì)相當(dāng)困難。不知道最后Meteor Lake——即酷睿Ultra第1代處理器交付時(shí),最終能達(dá)成多少Intel自己的預(yù)設(shè)。其實(shí)即便其中的某些設(shè)計(jì)與方案未能達(dá)成預(yù)期,在我們看來也不要緊,因?yàn)镸eteor Lake對(duì)未來的酷睿Ultra處理器也會(huì)是至關(guān)重要的一代產(chǎn)品。Meteor Lake對(duì)Intel而言,乃是重回半導(dǎo)體技術(shù)王座的堅(jiān)實(shí)一步。

編輯:黃飛

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論