ARM處理器是一種流行的處理器架構,用于許多現代移動設備和嵌入式系統中。中斷和異常是ARM處理器中的兩個重要概念,它們是處理器中斷程序執行的關鍵機制。

2023-09-05 15:45:30 696

696

每一個未分組寄存器來說在所有處理器模式下指的都是一個物理寄存器。2.在異常中斷造成的處理器模式切換時,由于不同的處理器模式下指的都是同一物理寄存器,可能造成未分組寄存器中數據破壞。3.任何可采用通用

2022-06-01 18:07:47

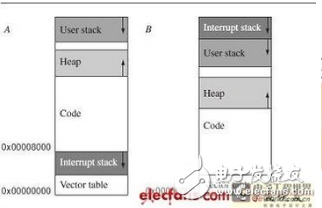

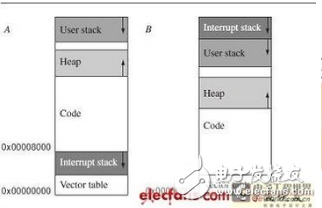

指令變為中斷和系統異常處理函數的起始地址。—寄存器組和某些編程模式也做了改變。這些變化意味著許多為經典ARM處理器編寫的匯編代碼需要修改,老的項目需要修改和重新編譯才能遷移到Cortex-M的產品上

2021-05-12 06:30:00

處理器模式和內部多線程和外部多處理器的處理器結構。在嵌入式系統中具有重要意義的異常中斷技術在S3C4510B系統中也體現了ARM體系獨有的一些的特點。本文根據S3C4510B系統的特點,分析了該系統中

2020-03-31 07:59:41

,CPU此時正在處理其他事情,當接收到這個信號會打斷當前cpu正在處理的事情。1)ARM有兩級外部中斷,FIQ和IRQ2)基于ARM系統的大多數有兩個中斷源中斷控制器:使cpu和外面可以接多個中斷源,作中斷

2022-05-05 10:16:31

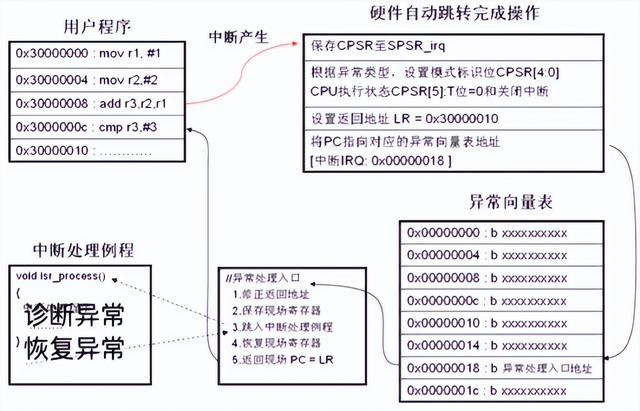

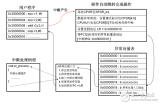

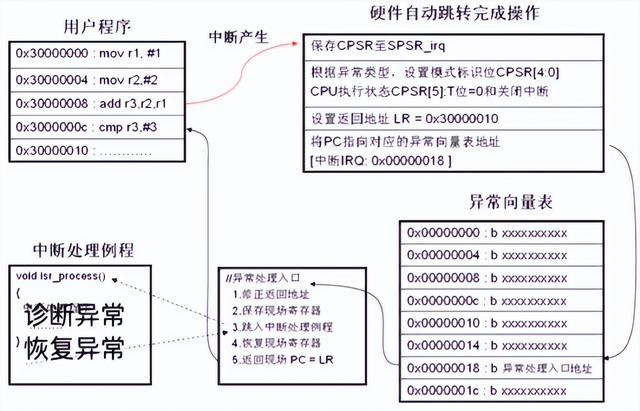

ARM處理器異常相應過程:1、保存處理器當前狀態、中斷屏蔽位以及各個條件標志位。將當前程序狀態寄存器CPSR保存到對應的SPSR寄存器中實現。每個異常中斷都有對應的物理SPSR寄存器。2、設置

2021-12-14 08:57:34

在ARM處理器中一條指令的執行分為取指、譯碼、執行三個階段,由于指令流水線的存在造成當前執行的指令的地址是PC-8(ARM指令集),那么當前執行指令的下一條指令的地址應該是PC-4,所以在異常產生

2017-03-02 15:08:27

在ARM處理器中一條指令的執行分為取指、譯碼、執行三個階段,由于指令流水線的存在造成當前執行的指令的地址是PC-8(ARM指令集),那么當前執行指令的下一條指令的地址應該是PC-4,所以在異常產生

2017-03-07 16:40:45

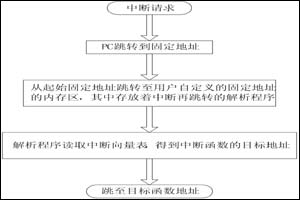

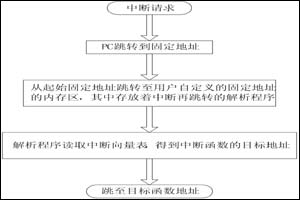

在ARM處理器中,我們常常使用SWI指令來產生一個軟中斷。軟中斷指令SWI指令中包含了一個24位的立即數,這個立即數指示了用戶請求的特定的SWI功能,即這個立即數表示的是SWI指令所想要觸發中斷

2017-01-10 15:09:37

ARM處理器中引起異常的原因是什么?

2022-11-03 15:20:37

)。FIQ 還必須禁用中斷。如果一個 FIQ 例程必須重新啟用中斷,則它太慢了,并應該是 IRQ 而不是 FIQ。 6.ARM處理器對異常中斷的響應過程 ARM處理器對異常中斷的響應過程如下所述

2020-11-17 16:13:49

的異常向量地址取下一條指令執行,從而跳轉到相應的異常處理程序處。如果異常發生時,處理器處于Thumb狀態,則當異常向量地址加載入PC時,處理器自動切換到ARM狀態。ARM微處理器對異常的響應過程用偽碼

2011-01-27 11:13:20

的異常向量地址取下一條指令執行,從而跳轉到相應的異常處理程序處。如果異常發生時,處理器處于Thumb狀態,則當異常向量地址加載入PC時,處理器自動切換到ARM狀態。ARM微處理器對異常的響應過程用偽碼

2011-01-27 14:19:05

(32位)數據,從第四個字節到第七個字節放置第二個存儲的字數據,一次排列。作為32位的微處理器,arm體系結構所支持的最大尋址空間為4GB。存儲器格式1、大端格式:高字節在低地址,低字節在高地址;2、小端

2017-11-06 10:43:47

32位的微處理器,arm體系結構所支持的最大尋址空間為4GB。存儲器格式1、大端格式:高字節在低地址,低字節在高地址;2、小端格式:高字節在高地址,低字節在低地址。指令長度Arm微處理器的指令長度是32位

2017-10-12 11:30:08

32位的微處理器,arm體系結構所支持的最大尋址空間為4GB。 存儲器格式1、大端格式:高字節在低地址,低字節在高地址;2、小端格式:高字節在高地址,低字節在低地址。 指令長度Arm微處理器的指令長度

2017-10-25 16:55:35

,同時該任務仍然使用用戶模式的寄存器組,而不是使用異常模式下相應的寄存器組,這樣可以保證當異常中斷發生時任務狀態不被破壞。二、ARM寄存器ARM處理器共有37個寄存器。包括:31個通用寄存器和6個狀態

2022-04-14 10:57:58

ARM處理器就會自動帶我們完成。其它重要的工作,必須由程序員來完成。ARM處理器處理的事包括從用戶模式切換到IRQ模式、狀態寄存器值的變化及跳轉。比如說,處理器自動跳轉到從0x0地址開始的異常中斷

2013-04-08 10:53:07

工作是任何異常發生時都必須要做的,所以ARM處理器就會自動帶我們完成。其它重要的工作,必須由程序員來完成。ARM處理器處理的事包括從用戶模式切換到IRQ模式、狀態寄存器值的變化及跳轉。比如說,處理器自動

2013-05-24 10:30:42

工作是任何異常發生時都必須要做的,所以ARM處理器就會自動帶我們完成。其它重要的工作,必須由程序員來完成。ARM處理器處理的事包括從用戶模式切換到IRQ模式、狀態寄存器值的變化及跳轉。比如說,處理器自動

2013-08-09 16:15:24

在學習與開發ARM處理器的過程中,一個不能繞開的話題就是異常處理流程。它在ARM的體系架構中,占據著不可動搖的重要地位。此處就以Coterx-A系列的ARM處理器簡單分析一下異常中斷處理流程。說異常

2016-11-11 09:55:57

在學習與開發ARM處理器的過程中,一個不能繞開的話題就是異常處理流程。它在ARM的體系架構中,占據著不可動搖的重要地位。此處就以Coterx-A系列的ARM處理器簡單分析一下異常中斷處理流程。說異常

2016-10-14 16:15:42

不同的異常中斷處理程序,返回地址以及使用的指令是不同的。ARM處理器對異常中斷的響應過程如下:(1).保存處理器當前狀態、中斷屏蔽位以及各條件標志位。這是通過將當前程序狀態寄存器CPSR的內容保存到將要執行

2020-08-28 08:09:17

(A+8); lr = pc – 4(這時處理器決定的,無法更改!)即 A+4。由于這類異常返回后應執行下一條指令(A+4),所以返回時,pc = lr 即可。 2.IRQ 和 FIQ 異常中斷處理的返回

2017-05-05 14:47:47

(這時處理器決定的,無法更改!)即 A+8 返回后,應執行被中斷而沒有執行的指令(上面的 A+4),所以返回時,pc = lr-4 3,指令預取中止異常中斷處理的返回:指令地址APC-8執行本指令時發生

2016-03-31 16:09:03

和快中斷異常,中斷必須在一條指令執行完以后被檢測到,如正在執行指令甲時發生了中斷,不等指令甲執行完是不會處理該中斷的,發生異常時 pc 已經更新(A+12); lr = pc – 4(這時處理器決定

2016-07-22 11:32:45

ARM(Advanced RISC Machines),既可認為是一個公司的名字,也可認為是對一類微處理器的統稱。中文名ARM嵌入式外文名Advanced RISC Machines屬 于一類微處理器的統稱產 品RISC處理器、相關技術及軟件目錄1 簡介? 企業? 處理器2

2021-09-09 07:29:36

ARM微處理器包括哪幾個系列?

2021-11-05 06:49:44

經典ARM微處理器包括7種異常:1、 復位異常2、 未定義指令異常3、 軟件中斷異常4、 預取指令異常5、 數據異常6、 IRQ(中斷)7、 FIQ(快速中斷)異常,單片機為中斷,籠統來講可以把異常

2021-07-16 07:04:57

1、ARM微處理器指令系統ARM指令集可以分為跳轉指令、數據處理指令、程序狀態寄存器傳輸指令、Load/Store指令、協處理器指令和異常中斷產生指令。根據使用的指令類型不同,指令的尋址方式分為

2022-04-26 10:30:57

):公司名/對一類微處理器的統稱/一種技術的名字1.2 ARM微處理器的應用領域及其特點1.應用領域①工業控制領域 :基于ARM核的微控制器芯片②無線通信領域 :超過85%的無線通信設備采用了ARM技術③網絡應用 :采用ARM技術的ADSL芯片此外,ARM在語音及視頻...

2021-12-14 07:38:22

微處理器的指令集可以分為六大類 :?跳轉指令?數據處理指令?程序狀態寄存器(PSR)處理指令?加載/存儲指令?協處理器指令?異常產生指令(1)ARM指令格式ARM指令的基本格式如下:...

2021-12-20 06:54:28

。而 Cortex-R 系列處理器的開發則面向深層嵌入式實時應用,對低功耗、良好的中斷行為、卓越性能以及與現有平臺的高兼容性這些需求進行了平衡考慮。? Cortex-A 系列1.3 ARM微處理器系列

2022-04-13 12:08:30

慕課電子科技大學.嵌入式系統.第三章.ARM微處理器編程基礎和接口實驗.ARM微處理器編程基礎實驗0 目錄3 ARM微處理器編程基礎和接口實驗3.1 ARM微處理器編程基礎實驗3.1.1課堂重點

2021-12-14 09:04:05

慕課電子科技大學.嵌入式系統.第三章.ARM微處理器編程基礎和接口實驗.ARM設備接口實驗0 目錄3 ARM微處理器編程基礎和接口實驗3.2 ARM設備接口實驗3.2.1課堂重點3.2.2測試與作業

2021-12-14 08:46:10

、FIQ,快速中斷請求(優先級3)當處理器的快速中斷請求引腳有效,且CPSR中的F位為0時,產生FIQ異常(異常向量:0x0000,001C)。總結如下表格:異常中斷類型異常中斷模式向量地址優先級(1最高

2014-10-13 10:06:50

(A+8);lr = pc – 4(這時處理器決定的,無法更改!)即A+4。由于這類異常返回后應執行下一條指令(A+4),所以返回時,pc=lr即可。IRQ 和FIQ異常中斷處理的返回指令地址對應于PC A

2017-05-31 15:45:30

在如今這個信息化時代,ARM嵌入式系統在各個領域均得到了廣泛的應用。本文從ARM的概念入手,就ARM嵌入式微處理器的相關內容進行了概述,并重點就ARM嵌入式微處理器的應用及發展情況,以及未來發展過程

2019-08-23 07:43:23

什么是ARM系列微處理器軟件架構工具?ARM系列微處理器軟件架構工具有哪些特征?

2021-11-05 06:40:18

ARM異常處理:只要正常的程序流被暫時中止,處理器就進入異常模式。例如響應一個來自外設的中斷。在處理異常之前,ARM內核保存當前的處理器狀態,這樣當處理程序結束是可以恢復執行原來的程序。注意:如果

2020-04-20 10:52:02

arm為什么是32位微處理器呢?所以ARM體系結構所支持的最大尋址空間為4GB嘍?

2023-03-15 10:27:53

中斷處理程序的執行可以被具有更高優先級的異常搶占。可以執行多少個具有更高優先級的異常中斷?產生了兩個中斷。這個數字是無限的嗎?

2022-12-09 08:01:35

如何從異常中斷返回?異常中斷處理程序結構什么樣?何為異常中斷向量表?哪一種異常中斷優先級最高?

2021-12-14 07:40:24

微處理器的結構是由哪些部分組成的?微處理器的代碼是如何執行的呢?

2022-02-28 09:25:10

1 引言 提到微處理器大家都會想到Intel公司和AMD公司的產品,但在當今嵌入式系統 應用 中還有一個同樣響亮的名字ARM微處理器,它是一種RISC 架構下嵌入式系統的核心部件,被廣泛地應用到 工業 控制、無線通訊、消費類 電子 產品等很多領域。

2019-07-15 06:49:14

目錄1、系統異常中斷2、外部中斷(全部)3、優先級5、如何開關中斷示例6、搶斷優先級、響應優先級說明7、定時器說明7.1基本定時器7.2高級/通用定時器7.3定時器拓展補充-主要特性F429 在內

2021-08-18 06:32:24

BOSStartHang ,//根據提示,應當永遠不會到這步的。其實很簡單,因為STM32本身的異常中斷PendSV_Handler替代了UCOS的異常中斷OSPe

2021-08-23 08:19:41

(A+8); lr = pc – 4(這時處理器決定的,無法更改!)即 A+4。由于這類異常返回后應執行下一條指令(A+4),所以返回時,pc = lr 即可。 2.IRQ 和 FIQ 異常中斷處理的返回

2016-09-23 14:35:11

(這時處理器決定的,無法更改!)即 A+8 返回后,應執行被中斷而沒有執行的指令(上面的 A+4),所以返回時,pc = lr-4 3,指令預取中止異常中斷處理的返回:指令地址APC-8執行本指令時發生

2016-07-25 11:19:25

一、ARM處理器之中斷與異常CPU被中斷的方式有指令不對、數據訪問有問題、Reset信號等這稱為異常,還有中斷源:按鍵、定時器、網路數據等稱為中斷,中斷處于一種異常體系,對于異常,首先需要我們保存

2022-05-30 09:46:26

RISC和CISC指令集有何區別呢?ARM處理器異常的處理過程是怎樣的?

2021-11-30 07:04:33

(A+8); lr = pc – 4(這時處理器決定的,無法更改!)即 A+4。由于這類異常返回后應執行下一條指令(A+4),所以返回時,pc = lr 即可。 2.IRQ 和 FIQ 異常中斷處理

2014-04-02 15:16:51

); lr = pc – 4(這時處理器決定的,無法更改!)即 A+4。由于這類異常返回后應執行下一條指令(A+4),所以返回時,pc = lr即可。 2.IRQ 和 FIQ 異常中斷處理的返回:指令地址

2016-07-04 16:20:49

戶模式進入系統模式。ARM 處理器是一個綜合體,ARM 公司自身并不制造微處理器。它們是由 ARM 的合作 伙伴(Intel 或 LSI)制造。ARM 還允許將其處理器通過協處理器接口進行緊耦合。它還

2019-09-24 17:47:38

用來保存額外的斷點信息。舉例BKPT ;BKPT 0xF02C;注意事項只有實現V5T體系結構的微處理器支持BKPT指令。BKPT指令時無條件的。3.前導0計數與使用其他ARM指令相比,前導0計數

2016-07-19 10:34:22

復制到發生的異常模式下SPSR中; b.模式切換:將CPSR模式位強制設置為與異常類型相對應的值,同時處理器進入到ARM執行模式,禁止所有IRQ中斷,當進入FIQ快速中斷模式時禁止FIQ中斷; c.

2018-05-10 10:58:33

。高效的處理能夠極大的提升系統的性能。ARM處理器一共有7種可以暫停指令的執行序列的異常。主要分為三個部分:點擊這里

2021-12-14 09:23:07

廣東省電子技術研究所 陳麗珍 林小薇要選好一款處理器,要考慮的因素很多,不單單是純粹的硬件接口,還需要考慮相關的操作系統、配套的開發工具、仿真器,以及工程師微處理器的經驗和軟件支持情況等。微處理器

2019-07-19 06:23:07

的。—向量表從跳轉指令變為中斷和系統異常處理函數的起始地址。—寄存器組和某些編程模式也做了改變。這些變化意味著許多為經典ARM處理器編寫的匯編代碼需要修改,老的項目需要修改和重新編譯才能遷移

2018-09-13 10:01:22

應用程式碼變大,需要較大的程式記憶體空間,且存在指的模式與異常令種類較多等等的缺點。4、大量使用寄存器二、ARM處理器的模式與異常ARM體系結構主要支持7種處理器模式,分別為 : 用戶模式、快中斷模式

2022-04-20 10:33:40

時間內響應中斷次數。二、異常源在ARM體系結構中,存在7種異常處理。當異常發生時,處理器會把PC設置為一個特定的存儲器地址。這一地址放在被稱為向量表(vector table)的特定地址范圍內,向量

2022-08-18 15:26:04

處理器對異常中斷的響應過程答:ARM處理器對異常中斷的響應過程如下所述:保存處理器當前狀態、中斷屏蔽位以及各條件標志位;設置當前程序狀態寄存器CPSR中的相應位;將寄存器lr_mode設置成返回地址

2017-10-17 14:19:25

處理器對異常中斷的響應過程答:ARM處理器對異常中斷的響應過程如下所述:保存處理器當前狀態、中斷屏蔽位以及各條件標志位;設置當前程序狀態寄存器CPSR中的相應位;將寄存器lr_mode設置成返回地址

2017-09-02 15:58:48

/*屏蔽外部中斷 IRQ*/PC = exception vector address復位異常概念當處理器復位引腳有效時,系統產生復位異常中斷,程序跳轉到復位異常中斷處理程序處執行,復位異常中斷通常

2022-04-13 11:44:12

ARM處理器對異常中斷的響應過程如下:1.將CPSR的內容保存到將要執行的異常中斷對應的SPSR中 。2.設置當前狀態寄存器CPSR中的相應位 3.將引起異常指令的下一條指令的地址保存到新的異常工作

2012-04-19 10:27:29

= pc – 4(這時處理器決定的,無法更改!)即 A+8 返回后,應執行被中斷而沒有執行的指令(上面的 A+4),所以返回時,pc = lr-43,指令預取中止異常中斷處理的返回:指令地址

2018-06-26 08:42:18

簡介ARM微處理器編程模型的一些基本概念,包括工作狀態切換、數據的存儲格式、處理器異常等,通過對本章的閱讀,希望讀者能了解ARM微處理器的基本工作原理和一些與程序設計

2008-09-09 14:54:17 382

382 通過基于立宇泰S3C44B0X 開發板的BSP 移植調試,闡述了VxWorks 的異常中斷處理機制,實現了VxWorks 基于S3C44B0X 處理器的中斷處理,并以外部中斷EINT4/5/6/7為例分析了中斷的響應過程,

2009-09-03 11:25:12 17

17 ARM微處理器的編程模型

目錄ARM微處理器的工作狀態ARM體系結構的存儲器格式指令長度及數據類型ARM微處理器的工作模式ARM體系結構的寄存器組織

2010-02-21 09:14:25 50

50 摘要:本文首先簡要概述了ARM處理器的異常中斷種類、響應和返回過程;然后重點討論了中斷解析程序的原理和實現,并分別給出了普通中斷和向量中斷的處理示例流程圖和詳細

2006-03-11 12:18:54 760

760

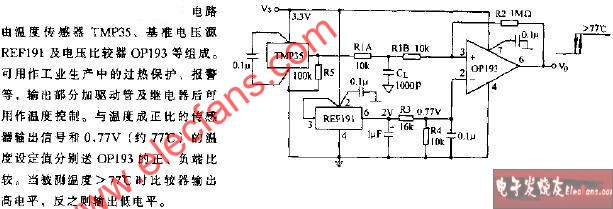

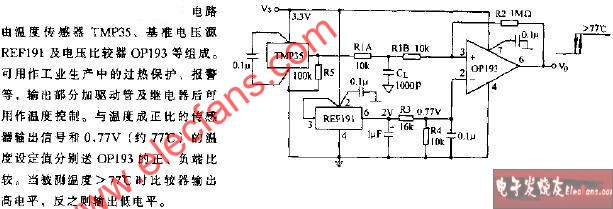

微處理器中斷發生器電路

2009-02-12 07:51:34 423

423

uCOS II在ARM處理器上移植過程中的中斷處理

uCOS II是一個源碼公開、可移植、可固化、可剪裁和搶占式的實時多任務操作系統,其大部分源碼是用ANSI C編寫,與處理器硬

2010-01-25 11:14:24 1532

1532 ARM單片機是大多數新手選擇的入門切入點,但由于知識的不足,在設計過程中新手們經常會遇到這樣或那樣的問題,ARM異常中斷返回就是這樣一種令人頭疼的問題。在ARM的使用問題中異常中斷返回是新手們較為苦惱的問題,本文就將對ARM異常中斷的集中情況進行總結,并給出了一些解決方法。

2016-04-28 10:52:56 1145

1145 ARM體系中的異常中斷及其應用

2017-09-22 16:51:52 4

4 3.4 異常中斷處理 異常或中斷是用戶程序中最基本的一種執行流程和形態。這部分主要對ARM架構下的異常中斷做詳細說明。 ARM有7種類型的異常,按優先級從高到低的排列如下:復位異常(Reset

2017-10-18 13:29:56 1

1 11.7 異常中斷產生指令(斷點指令) Thumb異常中斷產生指令與ARM指令集下的異常中斷指令十分相似。同ARM指令集相同,Thumb指令集中同樣包含兩條異常中斷產生指令:軟件中斷指令SWI用于

2017-10-19 09:32:58 0

0 ARM微處理器的概述

2017-10-25 11:42:19 9

9 所謂異常就是正常的用戶程序被暫時中止,處理器就進入異常模式,例如響應一個來自外設的中斷,或者當前程序非法訪問內存地址都會進入相應異常模式。

2017-11-02 12:57:26 17727

17727

當異常中斷發生時,系統執行完當前指令后,將跳轉到相應的異常中斷處理處執行。當異常中斷處理程序執行完成后,程序返回到發生中斷指令的下一條指令處繼續執行。在進入異常中斷處理程序時,要保存被中斷程序的執行線程。從中斷處理程序退出時要恢復被中斷程序的執行現場。

2017-12-16 08:57:03 4440

4440 嵌入式系統要求對異常及中斷處理器能快速響應。文中分析了ARM體系結構下 異常處理 特點,提出一種基于 ARM處理器 的高效異常處理解決方案,以LPC3250硬件平臺為基礎,對該方案進行了設計與實現

2018-02-03 03:38:01 1139

1139

本文介紹A了RM S3C4510B系統 的 異常中斷 機制,包括異常中斷的分類,響應與返回;中斷處理程序的安裝與調用;SWI,IRQ中斷的實例與關鍵代碼。隨著人們對于電子產品的要求越來越高

2018-02-03 05:32:01 1561

1561

ARM單片機是大多數新手選擇的入門切入點,但由于知識的不足,在設計過程中新手們經常會遇到這樣或那樣的問題,ARM異常中斷返回就是這樣一種令人頭疼的問題。在ARM的使用問題中異常中斷返回是新手們較為苦惱的問題,本文就將對ARM異常中斷的集中情況進行總結,并給出了一些解決方法。

2018-02-08 09:29:45 6187

6187

ARM單片機是大多數新手選擇的入門切入點,但由于知識的不足,在設計過程中新手們經常會遇到這樣或那樣的問題,ARM異常中斷返回就是這樣一種令人頭疼的問題。在ARM的使用問題中異常中斷返回是新手們較為苦惱的問題,本文就將對ARM異常中斷的集中情況進行總結,并給出了一些解決方法。

2018-05-26 07:11:00 2800

2800 ARM中異常中斷的類型問題分析總結 一、ARM中異常中斷的類型: 異常中斷名稱 含義 復位(Reset) 當處理器復位引腳有效時,系統產生復位異常中斷,程序跳轉到復位異常中斷處理程序處執行。復位

2018-04-05 10:51:00 1148

1148 ARM體系結構中,存在7種異常處理。當異常發生時,處理器會把PC設置為一個特定的存儲器地址。這一地址放在被稱為向量表(vector table)的特定地址范圍內。向量表的入口是一些跳轉指令,跳轉到專門處理某個異常或中斷的子程序。

2019-03-20 10:25:32 7

7 當ARM異常中斷發生時,系統執行完當前指令后,將跳轉到相應的異常中斷處理程序處執行。當異常中斷處理程序執行完成后,程序返回到發生中斷指令的下條指令處執 行。在進入異常中斷處理程序時,要保存被中斷程序的執行現場,從異常中斷處理程序退出時,要恢復被中斷程序的執行現場。

2020-06-17 10:05:12 7046

7046 外部中斷請求(IRQ) 當處理器的外部中斷請求引腳有效,而且CPSR的寄存器的I控制位被清除時,處理器產生外部中斷請求異常中斷。系統中個外設通過該異常中斷請求處理服務。

2020-08-27 14:21:29 2354

2354 異常是能夠引起程序流偏離正常流程的事件,當異常發生時,正在執行的程序就會被掛起,處理器轉而執行一塊與該事件相關的代碼(異常處理)。事件可以是外部輸入,也可以是內部產生的,外部產生的事件通常被稱作中斷

2021-10-12 17:14:18 4165

4165 在Cortex‐M0內核上搭載了一個異常響應系統,支持眾多的系統異常和外部中斷。其中,編號為1-15的對應系統異常,大于等于16的則全是外部中斷,優先級的數值越小,則優先級越高。除了個別異常的優先級被定死外,其它異常的優先級都是可編程的。

2022-06-01 14:41:41 3614

3614 正確處理,處理器可能會崩潰或數據損毀。ARM處理器有七種異常模式,即:重置模式、用戶模式、FIQ模式、IRQ模式、監督模式、中斷模式和異常模式。 1. 重置模式 當ARM處理器啟動時,它將進入重置模式。在這種模式下,處理器處于其最初狀態

2023-09-05 16:22:25 2036

2036 arm處理器有哪些中斷源?arm處理器對異常中斷的響應過程? ARM處理器是一種廣泛使用的嵌入式處理器,運行著各種不同類型的應用程序。為了保證應用程序的穩定性和正確性,ARM處理器需要在遇到異常

2023-10-19 16:35:59 675

675 ARM9處理器從哪些方面保證了FIQ異常響應的快速性? ARM9處理器是一款高性能、低功耗的處理器,它采用了一系列技術來優化FIQ異常響應的速度和精度。本文將從以下幾個方面詳細介紹ARM9處理器

2023-10-19 16:36:02 413

413 機制。ARM處于操作系統和硬件之間,因此異常處理機制在有效性、安全性、可靠性方面必須經過充分測試和驗證。 ARM異常指令是程序中不受控制的分支或其他例外情況,如硬件故障、訪問非法地址、非法指令、軟件中斷等。雖然大多處理器都有異常響應和處理

2023-10-19 16:36:05 454

454 ARM中的異常中斷是如何實現進入中斷程序的?如何進入呢? 在計算機系統中,異常和中斷是兩個常見的概念。 在ARM中,異常和中斷的主要目的是幫助處理器響應與系統操作相關的事件。 由于處理器必須同時執行

2023-10-19 16:36:11 481

481 ARM中斷的實現是通過中斷控制器和異常模式實現的。ARM處理器通過中斷控制器來接收和處理外部的中斷信號,而異常模式用于處理內部的異常事件。本文將詳細介紹ARM中斷的原理和實現方式。 一、ARM中斷

2024-01-05 15:18:11 206

206

電子發燒友App

電子發燒友App

評論