1 引言

目前, 在軍事、工業和醫學領域存在著大量的非標準視頻系統, 其視頻信號只能在專業的設備上才能播放和錄制。而實際中廣泛采用的是標準電視信號(PAL ,NTSC, SECAM) 或VGA 視頻, 這就給這些領域內的觀測監督和學術交流造成了許多困難。以醫學信號為例, 目前, 國內醫院很多科室的手術監控設備都是國外進口的一體式設備, 手術影像資料只能供室內的幾名醫生觀看, 無法通過電視系統傳送到外部監測。如能將非標準視頻流轉換為標準視頻流, 無疑會給這些領域帶來很大的便利。時下的視頻轉換系統大多存在轉換速度慢、功能單一、圖像質量不高的缺點, 且一般是一機一用。本文介紹了基于單片機+ FPGA 的視頻制式的轉換系統, 利用單片機方便的嵌入性及靈活的可編程性, 再結合FPGA 強大的邏輯控制功能很好地克服了這些弊端, 實現了實時、高質量的視頻圖像轉換, 同時, 可以方便地改變系統參數, 實現一機多用。

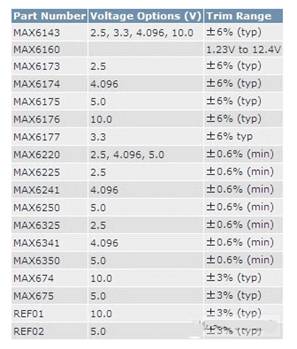

2 系統設計原理簡介

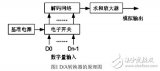

不同制式視頻信號間的根本區別在于掃描方式和行場頻率不同。標準VGA 采用逐行掃描, 在一幀內實現對圖像的完全掃描; 標準電視信號(以PAL制為例)采用隔行掃描, 利用視覺暫留, 將奇偶場恢復成一幀完整圖像。而非標準視頻流則無一定規律。因此, 視頻轉換的基本思路是將非標準視頻信號經模數轉換成數字信號, 在存儲器中緩存, 變頻讀出或經過數字信號處理, 再通過數模轉換恢復成標準視頻流。本系統設計思

路框圖如圖1 所示。

從原理可以看出, 只要數據讀出速度高于寫入速度, 就不會使圖像產生突變現象, 從而達到實時處理的目的。設計中, 存儲器采用2片512K×8 bit 的FIFOAL440, 它采用DRAM 工藝, 最高時鐘可達80MHz,是專用的視頻存儲器。邏輯主控單元選用Altera 公司出品的FLEX10K50E 實現, 其門數達到5 萬個, 處理速度最高可達220MHz, 很適合高速數據流處理。同步恢復采用74ACT715, 它可按編程數據產生隔行或逐行的電視行場同步信號, 非常適合于多制式輸出系統。而視頻恢復編碼部分采用的是專用數字圖像處理芯片DSP AL128, 其內置的高集成化數字處理器, 可以將逐行掃描數字信號直接恢復成標準電視信號和S-VIDEO 輸出。

3 系統設計實現

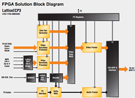

整個系統大體框架如圖2 所示, 圖中虛線部分均由FPGA 實現。

3. 1 單片機接口模塊

系統中有FIFO ,AL128 的I2C 參數和74ACT715的初始化參數及數模、模數時鐘分頻參數共計90 個,為避免出現繁瑣的判斷語句, 設計中采用FPGA 內置ROM 結構。其原理圖如圖3 所示。

圖3 單片機譯碼原理圖

FPGA 將單片機送來的機器地址(00H~5AH )譯碼成芯片地址, 芯片地址總共10位, 高2位用來判斷配置何種芯片, 低8位用來判斷配置該芯片中第N個寄存器。再結合單片機送來的數據線和讀寫控制線來決定對該寄存器進行讀或寫操作以及寫入的數據。

74ACT715 的配置參數為12位, 配置中用兩個連續的地址分別記錄其高4位和低8位數據。其中, 57H~5AH為只讀地址, 相應數據將控制數模、模數時鐘的頻率。

3. 2 I2C 配置及時鐘控制模塊

本系統FPGA 的一個重要功能就是對芯片初始化和I2C 參數配置。I2C 總線是一種由飛利浦公司開發的接口總線, 利用一條數據線sdata 和一條時鐘線sclk 在主從器件間進行串行通信。飛利浦公司制定了標準I2C協議, 但是, 工業上依然使用很多非標準I2C器件, 本系統的FIFO、AL128 均為非標準I2C 器件, 故要對它們分別進行配置, 利用FPGA 的邏輯控制及內置MUX 可以在不同讀寫時序間靈活切換, 達到對多個芯片的全雙工同步數據傳輸。實現原理圖如圖4 所示。

圖4 總線切換控制原理圖

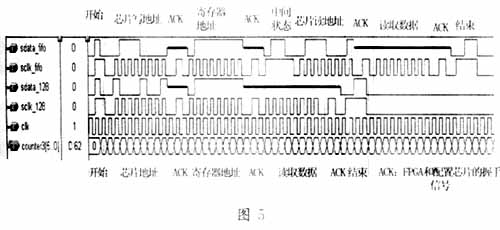

同時, 由系統實現原理分析可知, 視頻制式變換的關鍵在于掃描頻率變化, 即,AD采樣時鐘頻率和DA圖像恢復時鐘頻率。這部分數字頻率在系統中是由外部鎖相環(PLL) 和FPGA 中的可變分頻計數器實現的。其原理圖如圖5 所示。

圖5 數字鎖相環原理圖

與普通鎖相環不同的是, 利用FPGA 的可編程性, PLL的參考頻率可以由單片機配置的分頻數隨意更改, 使數字頻率合成電路有較高的穩定性、靈活性和靈敏度。

3. 3 FIFO 控制模塊

考慮到非標準視頻信號一幀圖像數據量太大, 一塊FIFO 放不下, 同時, 電視信號都采用隔行掃描, 數據流將按奇偶場交替輸出, 故設計中用兩塊FIFO A、B 分別存放圖像的奇偶幀, 但在圖像恢復時為逐行掃描方式, 這就涉及到在兩塊FIFO 間交替讀出數據的問題。設計中, 用兩個場同步信號Vsync 間的行同步信號Hsync 做判斷, 決定兩塊F IFO 的讀寫, 使數據按ABAB..... 逐行讀出。該部分代碼段如下, 仿真時序圖見圖6。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY ctrl IS

PORT (

vsync, hsync : IN STD_LOGIC;

fifoa_en, fifob_en:OUT STD_LOGIC

);

END ctrl;

ARCHITECTURE behav OF ctrl IS

SIGNAL fifo_en: STD_LOGIC;

BEGIN

PROCESS (hsync, vsync)

BEGIN

IF vsync='0' THEN

fifo_en<= '1';

ELSIF hsync'event AND hsync='0' THEN

fifo_en<= not (fifo_en);

END IF;

END PROCESS;

fifoa_en<= fifo_en WHEN vsync='1' ELSE '1';

fifob_en<= not (fifo_en) WHEN vsync='1' ELSE '1';

END behav;

圖6 仿真時序圖

在時鐘方面, FIFO 寫入時鐘與AD 采樣時鐘相等,FIFO 讀出時鐘與DA 恢復像素時鐘相等。實時處理運動幀時, 為不在兩場之間出現跳動現象, 讀出時鐘要高于寫入時鐘。在實際應用中, 為了產生分頻率1024×768, 刷新頻率為60 Hz 的VGA 圖像, 讀出時鐘高達46MHz,這樣的高速數據處理就必須滿足一定的時延要求。以50MHz 時鐘為例, 數據與時鐘間的最大時延不能超過10ns (像素時鐘20ns, 半周期為10ns)。經過FGPA 的Quartus 綜合分析, 時鐘與數據間的最大延時為3.7ns, 滿足系統時延要求。一般地, 這一數據是系統最壞情況下的延時, 實際系統延時將小于仿真數據。

4 結束語

在數字電路設計中, FPGA 發揮了越來越重要的作用, 隨著FPGA 向高密度、低成本方向發展, 目前的一個趨勢是把系統級功能放到FPGA 器件中。本文介紹的視頻轉換系統以FPGA 作為系統主控元件, 不但大大減少了電路版尺寸, 而且增強了系統可靠性和靈活性。在實際測試中, 將非標準隔行視頻信號(1024行, 50Hz 場頻) 成功地轉換成了高清晰度的VGA 圖像和標準PAL 電視圖像。目前, 該系統已應用于某醫院監視系統。

電子發燒友App

電子發燒友App

評論