LED的多種形式封裝結(jié)構(gòu)及技術(shù)

LED是一類(lèi)可直接將電能轉(zhuǎn)化為可見(jiàn)光和輻射能的發(fā)光器件,具有工作電壓低,耗電量小,發(fā)光

2009-12-31 09:09:03 1170

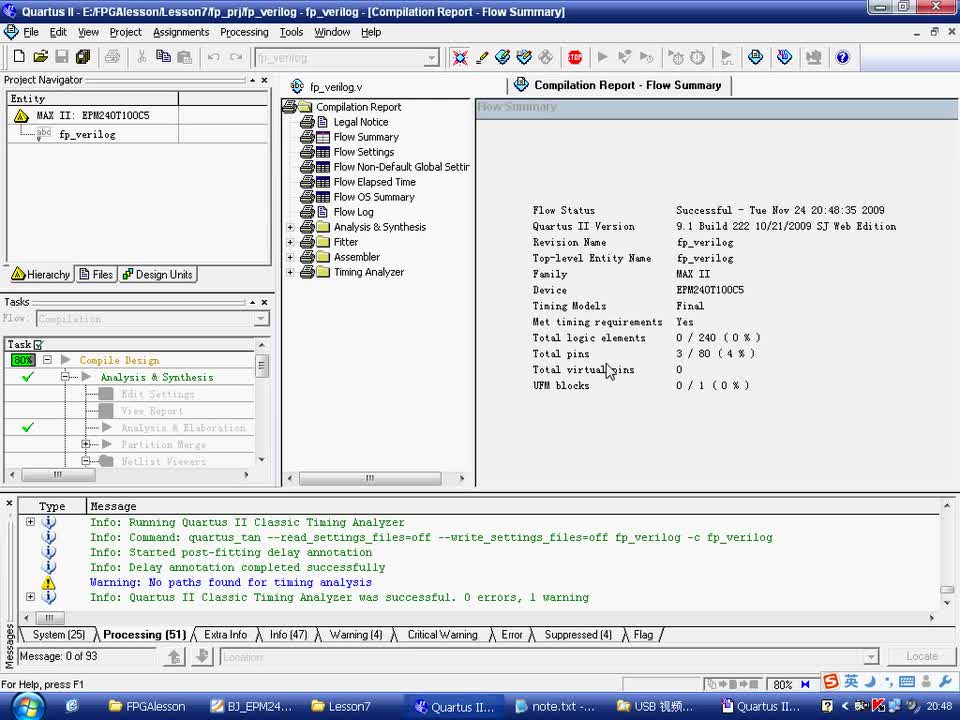

1170 分頻器是數(shù)字系統(tǒng)設(shè)計(jì)中的基本電路,根據(jù)不同設(shè)計(jì)的需要,我們會(huì)遇到偶數(shù)分頻、奇數(shù)分頻、半整數(shù)分頻等,有時(shí)要求等占空比,有時(shí)要求非等占空比。在同一個(gè)設(shè)計(jì)中有

2010-09-03 17:04:20 2442

2442

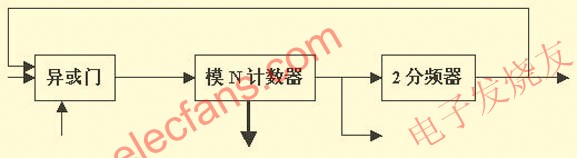

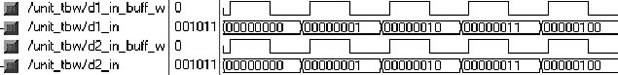

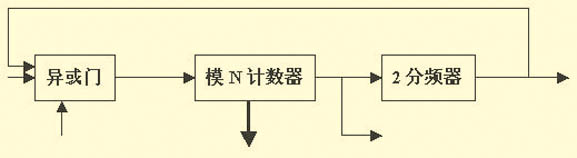

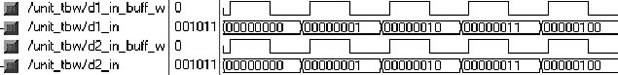

本文首先介紹了各種分頻器的實(shí)現(xiàn)原理,并在FPGA開(kāi)發(fā)平臺(tái)上通過(guò)VHDL文本輸入和原理圖輸入相結(jié)合的方式,編程給出了仿真結(jié)果。最后通過(guò)對(duì)各種分頻的分析,利用層次化設(shè)計(jì)思想,綜合設(shè)計(jì)出了一種基于FPGA的通用數(shù)控分頻器,通過(guò)對(duì)可控端口的調(diào)節(jié)就能夠實(shí)現(xiàn)不同倍數(shù)及占空比的分頻器。

2015-05-07 09:43:16 4685

4685

;文獻(xiàn)[5]給出了FPGA內(nèi)部沒(méi)計(jì)TS101鏈路口的框圖,但只給出了簡(jiǎn)單的介紹,無(wú)法給設(shè)計(jì)者以參考。本文采用Altera公司Cyclone系列芯片EP1C12實(shí)現(xiàn)了與TS101/TS201兩種芯片的鏈路口

2019-06-19 05:00:08

;文獻(xiàn)[5]給出了FPGA內(nèi)部沒(méi)計(jì)TS101鏈路口的框圖,但只給出了簡(jiǎn)單的介紹,無(wú)法給設(shè)計(jì)者以參考。本文采用Altera公司Cyclone系列芯片EP1C12實(shí)現(xiàn)了與TS101/TS201兩種芯片的鏈路口

2018-12-04 10:39:29

初學(xué)FPGA,聽(tīng)說(shuō)分頻貌似挺重要,是必備的基礎(chǔ)技能。小白的我今天就從奇偶分頻開(kāi)始我的FPGA學(xué)習(xí)成長(zhǎng)之路偶數(shù)分頻很簡(jiǎn)單的哈,打字蠻累的,直接上代碼/*************6分頻

2016-03-30 11:35:51

`基于FPGA+的任意小數(shù)分頻器的設(shè)計(jì)基于FPGA的多種分頻設(shè)計(jì)與實(shí)現(xiàn)基于FPGA的小數(shù)分頻器的實(shí)用Verilog 實(shí)現(xiàn)基于FPGA 的通用分頻用Verilog+HDL實(shí)現(xiàn)基于FPGA的通用分頻

2012-02-03 15:02:31

分頻器模塊實(shí)現(xiàn)的基本原理就是設(shè)計(jì)一個(gè)工作在系統(tǒng)時(shí)鐘下的計(jì)數(shù)器,循環(huán)地遞減或者遞加計(jì)數(shù),在某個(gè)計(jì)數(shù)的固定值將輸出翻轉(zhuǎn),即可實(shí)現(xiàn)時(shí)鐘分頻的功能。例如,實(shí)驗(yàn)板上的系統(tǒng)時(shí)鐘是 50MHz,而所需的讀寫(xiě)周期

2018-11-15 09:25:35

誰(shuí)幫忙設(shè)計(jì)一下模數(shù)轉(zhuǎn)換芯片ADC0809以及串行通信部分均需要有相應(yīng)的時(shí)鐘驅(qū)動(dòng)。而此次選擇的Altera CycloneⅡ系列FPGA中的EP2C5T144C8的系統(tǒng)時(shí)鐘為20MHz,因此根據(jù)需要

2014-05-09 11:53:23

fpga 基于quartus ii的原理圖設(shè)計(jì) 有哪些分頻模塊啊

2011-11-18 11:03:34

`fpga應(yīng)用篇(三):你可能用了假分頻 分頻對(duì)于fpga的重要性不言而喻,對(duì)于大多數(shù)通信方式來(lái)說(shuō),一個(gè)穩(wěn)定且準(zhǔn)確的分頻程序?qū)τ谕ㄐ诺姆€(wěn)定很重要。為什么你的UART總是不穩(wěn)定,很有可能你用了一個(gè)假

2017-04-07 21:03:07

多種EDA工具的FPGA設(shè)計(jì)方案

2012-08-17 10:36:17

多種開(kāi)發(fā)板FPGA原理圖

2013-10-29 16:47:12

,一旦為低,FPGA指示程序數(shù)據(jù)加載 CRC校驗(yàn)出錯(cuò)。此時(shí)需要復(fù)位FPGA,重新加載。4、嵌入式 的驅(qū)動(dòng)實(shí)現(xiàn)本文以模塊形式實(shí)現(xiàn)了運(yùn)行于上的驅(qū)動(dòng)程序,源文件如下(有關(guān)寄存器的設(shè)置參考的數(shù)據(jù)手冊(cè),以下源代碼

2019-12-10 17:42:18

Actel FPGA PLL鎖相環(huán)的最大能達(dá)到幾倍頻幾分頻?我在網(wǎng)上查了一下有人說(shuō)是20倍頻,10分頻,但是我沒(méi)有在芯片手冊(cè)里面找到資料,想要確認(rèn)一下。

2014-12-04 11:25:15

GSM賦予基站的無(wú)線組網(wǎng)特性使基站的實(shí)現(xiàn)形式可以多種多樣--宏蜂窩、微蜂窩、微微蜂窩及室內(nèi)、室外型基站,無(wú)線頻率資源的限制又使人們更充分地發(fā)展著基站的不同應(yīng)用形式來(lái)增強(qiáng)覆蓋,吸收話(huà)務(wù)--遠(yuǎn)端 TRX、分布天線系統(tǒng)、光纖分路系統(tǒng)、直放站。

2019-10-31 09:11:24

在FPGA的設(shè)計(jì)中一直都擔(dān)任著很重要的角色,而說(shuō)到分頻,我相信很多人都已經(jīng)想到了利用計(jì)數(shù)器計(jì)數(shù)來(lái)得到想要的時(shí)鐘頻率,但問(wèn)題是僅僅利用計(jì)數(shù)器來(lái)分頻,只可以實(shí)現(xiàn)偶數(shù)分頻,而如果需要三分頻、五分頻、七分頻

2019-12-11 10:15:33

`我想采集電壓信號(hào)然后將它轉(zhuǎn)換成電流信號(hào),但是它倆差了90度相位角想的是通過(guò)先倍頻再分頻來(lái)實(shí)現(xiàn)我看了一下網(wǎng)上可以用D觸發(fā)器來(lái)實(shí)現(xiàn),但是這樣的倍頻與分頻過(guò)后相位并沒(méi)有改變這個(gè)電路原理上有什么問(wèn)題?有沒(méi)有朋友做過(guò)類(lèi)似的電路可以實(shí)現(xiàn)這樣的功能`

2015-05-13 19:49:35

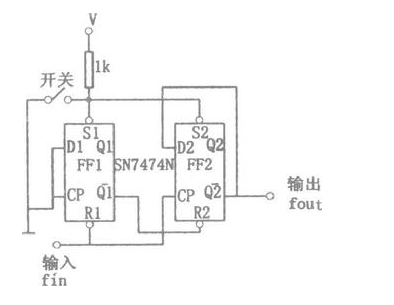

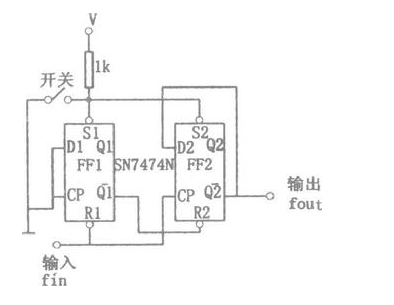

各位FPGA的高手們,小弟再做一個(gè)FPGA二分頻信號(hào)時(shí),有一個(gè)很困惑的問(wèn)題,一直搞不明白,具體要求如下硬件連接,編程要求圖中電源電壓VCC=3.3V,R1 = 1×(1±10%)KΩ,R2 = 1

2015-03-13 13:35:12

//分頻程序修訂版,只需要修改一個(gè)參數(shù)就可以完成指定的分頻工作//修改DIV參數(shù)即可,最大支持2的32方分頻module div(clk_out, clk_in, rst);output

2019-12-12 14:35:25

分頻器是FPGA設(shè)計(jì)中使用頻率非常高的基本設(shè)計(jì)之一,盡管在目前大部分設(shè)計(jì)中,廣泛使用芯片廠家集成的鎖相環(huán)資源,如賽靈思(Xilinx)的DLL.來(lái)進(jìn)行時(shí)鐘的分頻,倍頻以及相移。但是對(duì)于時(shí)鐘要求不高

2019-06-14 06:30:00

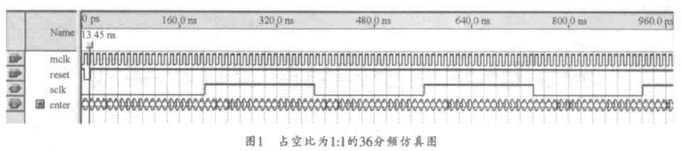

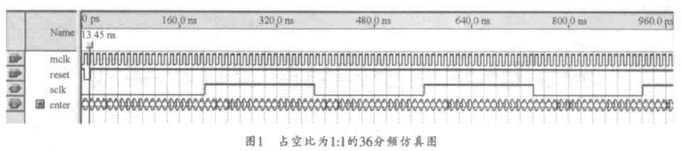

基于FPGACPLD的占空比為1∶n的n分頻器的設(shè)計(jì)

2017-09-30 09:11:08

本帖最后由 weihu_lu 于 2014-6-19 16:25 編輯

作者:盧威虎1、前言 分頻器是FPGA設(shè)計(jì)中使用頻率非常高的基本單元之一。盡管目前在大部分設(shè)計(jì)中還廣泛使用集成鎖相環(huán)(如

2014-06-19 16:15:28

【摘要】:介紹了基于FPGA的任意分頻系數(shù)的分頻器的設(shè)計(jì),該分頻器能實(shí)現(xiàn)分頻系數(shù)和占空比均可以調(diào)節(jié)的3類(lèi)分頻:整數(shù)分頻、小數(shù)分頻和分?jǐn)?shù)分頻。所有分頻均通過(guò)VHDL語(yǔ)言進(jìn)行了編譯并且給出了仿真圖。本

2010-04-26 16:09:01

中從電子設(shè)計(jì)的外圍器件逐漸演變?yōu)閿?shù)字系統(tǒng)的核心。伴隨著半導(dǎo)體工藝技術(shù)的進(jìn)步,FPGA器件的設(shè)計(jì)技術(shù)取得了飛躍發(fā)展及突破。分頻器通常用來(lái)對(duì)某個(gè)給定的時(shí)鐘頻率進(jìn)行分頻,以得到所需的時(shí)鐘頻率。在設(shè)計(jì)數(shù)

2019-10-08 10:08:10

分頻器在CPLD/FPGA設(shè)計(jì)中使用頻率比較高,盡管目前大部分設(shè)計(jì)中采用芯片廠家集成的鎖相環(huán)資源 ,但是對(duì)于要求奇數(shù)倍分頻(如3、5等)、小數(shù)倍(如2.5、3.5等)分頻、占空比50%的應(yīng)用場(chǎng)合卻往往不能滿(mǎn)足要求。利用CPLD/FPGA設(shè)計(jì)多功能分頻器,我們具體該怎么做呢?

2019-08-12 07:50:25

分頻器是FPGA設(shè)計(jì)中使用頻率非常高的基本設(shè)計(jì)之一,盡管在目前大部分設(shè)計(jì)中,廣泛使用芯片廠家集成的鎖相環(huán)資源,如賽靈思(Xilinx)的DLL.來(lái)進(jìn)行時(shí)鐘的分頻,倍頻以及相移。但是對(duì)于時(shí)鐘要求不高

2019-07-09 09:11:47

LS 小波變換是怎樣進(jìn)行的?FPGA 及提升核是怎樣實(shí)現(xiàn)的?如何實(shí)現(xiàn)提升小波變換核?

2021-04-12 06:27:38

怎么設(shè)計(jì)一款基于FPGA的多種分頻設(shè)計(jì)?

2021-05-08 07:06:43

汽車(chē)電子鎖有多種形式,常見(jiàn)的是電子鑰匙式電子鎖。這種電子鎖的鑰匙內(nèi)藏電子電路存儲(chǔ)密碼,通過(guò)光、電和磁性等多種形式和主控電路聯(lián)系。

2020-03-19 09:01:27

我想對(duì)2GHz的正弦波(相位噪聲很低)進(jìn)行16分頻,分頻出來(lái)的125M信號(hào)輸入給FPGA,想選用ADi的分頻器實(shí)現(xiàn)分頻功能,我有以下幾個(gè)問(wèn)題:1.我查了ADi的分頻器,分為(1)時(shí)鐘分頻器,(2

2019-01-11 13:39:43

求助FM調(diào)制器的FPGA實(shí)現(xiàn),對(duì)FPGA這些完全不了解,在網(wǎng)上看可以用DDS技術(shù)實(shí)現(xiàn)FM的數(shù)字調(diào)制,就在書(shū)上按照步驟先做了產(chǎn)生正弦波分頻模塊尋址模塊數(shù)據(jù)存儲(chǔ)模塊,但編譯不能通過(guò),也不知道該怎樣進(jìn)行頻率調(diào)制,請(qǐng)問(wèn)該怎樣實(shí)現(xiàn)頻率的調(diào)制,請(qǐng)問(wèn)有人寫(xiě)過(guò)頻率調(diào)制的verilog代碼嗎,急求,謝謝

2019-03-16 11:43:26

進(jìn)行讀寫(xiě)操作和異步讀寫(xiě)時(shí)鐘的FIFO。這是MII接口設(shè)計(jì)中的難點(diǎn),本身也具有很高的實(shí)用價(jià)值。奇偶分頻器的實(shí)現(xiàn)分頻器是數(shù)字系統(tǒng)設(shè)計(jì)中的基本電路,同一個(gè)設(shè)計(jì)中有時(shí)要求多種形式的分頻。通常由計(jì)數(shù)器或計(jì)數(shù)器

2019-04-30 07:00:16

專(zhuān)用協(xié)議MAC的形式實(shí)現(xiàn)實(shí)時(shí)功能。而協(xié)議的其他功能由運(yùn)行在嵌入式處理器中的軟件堆棧來(lái)完成,這些處理器可以是在Cyclone III FPGA中實(shí)現(xiàn)的Nios II軟核處理器。

2019-07-29 07:40:50

在復(fù)雜數(shù)字邏輯電路設(shè)計(jì)中,經(jīng)常會(huì)用到多個(gè)不同的時(shí)鐘信號(hào)。介紹一種通用的分頻器,可實(shí)現(xiàn)2~256 之間的任意奇數(shù)、偶數(shù)、半整數(shù)分頻。首先簡(jiǎn)要介紹了FPGA 器件的特點(diǎn)和應(yīng)用范

2009-11-01 14:39:19 78

78 本文介紹了一種能夠完成半整數(shù)和各種占空比的奇/偶數(shù)和的通用的分頻器設(shè)計(jì),并給出了本設(shè)計(jì)在Altera公司的FLEX10K系列EPF10K10LC84-3型FPGA芯片中實(shí)現(xiàn)后的測(cè)試數(shù)據(jù)和設(shè)計(jì)硬件的測(cè)

2009-12-19 16:25:09 65

65 基于FPGA 的等占空比任意整數(shù)分頻器的設(shè)計(jì)

給出了一種基于FPGA 的等占空比任意整數(shù)分頻電路的設(shè)計(jì)方法。首先簡(jiǎn)要介紹了FPGA 器件的特點(diǎn)和應(yīng)用范圍, 接著討論了一

2010-02-22 14:22:32 39

39 簡(jiǎn)要介紹了CPLD/FPGA器件的特點(diǎn)和應(yīng)用范圍,并以分頻比為2.5和1.5的分頻器的設(shè)計(jì)為例,介紹了在MaxPlusII開(kāi)發(fā)軟件下,利用VHDL硬件描述語(yǔ)言以及原理圖的輸入方式來(lái)設(shè)計(jì)數(shù)字邏輯電路的過(guò)

2010-07-17 17:55:57 36

36 摘要:簡(jiǎn)要介紹了CPLD/FPGA器件的特點(diǎn)和應(yīng)用范圍,并以分頻比為2.5的半整數(shù)分頻器的設(shè)計(jì)為例,介紹了在MAX+plus II開(kāi)發(fā)軟件下,利用VHDL硬件描述語(yǔ)言以及原理圖的輸

2006-03-13 19:36:44 869

869

用VHDL語(yǔ)言實(shí)現(xiàn)3分頻電路

標(biāo)簽/分類(lèi):

眾所周知,分頻器是FPGA設(shè)計(jì)中使用頻率非常高的基本設(shè)計(jì)之一,盡管在目前大部分設(shè)計(jì)中,廣泛使用芯片廠家集成的鎖相

2007-08-21 15:28:16 5527

5527

具有奇次和偶次分頻的分頻器

2009-04-11 10:22:12 880

880

基于多種EDA工具的FPGA設(shè)計(jì)

介紹了利用多種EDA工具進(jìn)行FPGA設(shè)計(jì)的實(shí)現(xiàn)原理及方法,其中包括設(shè)計(jì)輸入、綜合、功能仿真、實(shí)現(xiàn)、時(shí)序仿真、配置下載等具體內(nèi)容。并以實(shí)

2009-05-14 18:38:38 854

854

D觸發(fā)器實(shí)現(xiàn)二分頻電路(D觸發(fā)器構(gòu)成的2分頻電路)&

2009-06-12 13:58:56 75438

75438

摘要:介紹了利用多種EDA工具進(jìn)行FPGA設(shè)計(jì)的實(shí)現(xiàn)原理及方法,其中包括設(shè)計(jì)輸入、綜合、功能仿真、實(shí)現(xiàn)、時(shí)序仿真、配置下載等具體內(nèi)容。并以實(shí)際操作介紹了

2009-06-20 11:42:45 522

522

摘要:介紹了為PET(正電子發(fā)射斷層掃描儀)的前端電子學(xué)模塊提供時(shí)間基準(zhǔn)而設(shè)計(jì)的一種新型高頻時(shí)鐘扇出電路。該電路利用FPGA芯片來(lái)實(shí)現(xiàn)對(duì)高頻時(shí)鐘的分頻

2009-06-20 12:41:04 1238

1238

摘要:簡(jiǎn)要介紹了CPLD/FPGA器件的特點(diǎn)和應(yīng)用范圍,并以分頻比為2.5的半整數(shù)分頻器的設(shè)計(jì)為例,介紹了在MAX+plus II開(kāi)發(fā)軟件下,利用VHDL硬件描述語(yǔ)言以及原理圖的輸

2009-06-20 12:45:00 627

627

摘 要: 本文利用FPGA完成了8路同步話(huà)音及16路異步數(shù)據(jù)的復(fù)接與分接過(guò)程,并且實(shí)現(xiàn)了復(fù)接前的幀同步捕獲和利用DDS對(duì)時(shí)鐘源進(jìn)行分頻得到所需時(shí)鐘的過(guò)程。該設(shè)計(jì)

2009-06-20 13:38:43 565

565

用VHDL語(yǔ)言實(shí)現(xiàn)3分頻電路(占空比為2比1)

分頻器是FPGA設(shè)計(jì)中使用頻率非常高的基本設(shè)計(jì)之一,盡管在目前大部分設(shè)計(jì)中,廣泛使用芯片廠家集成的鎖

2009-06-22 07:46:33 7831

7831 基于CPLD/FPGA的多功能分頻器的設(shè)計(jì)與實(shí)現(xiàn)

引言

分頻器在CPLD/FPGA設(shè)計(jì)中使用頻率比較高,盡管目前大部分設(shè)計(jì)中采用芯片廠家集成的鎖相環(huán)資源 ,但是對(duì)于要求

2009-11-23 10:39:48 1139

1139

多種EDA工具的FPGA設(shè)計(jì)方案

概述:介紹了利用多種EDA工具進(jìn)行FPGA設(shè)計(jì)的實(shí)現(xiàn)原理及方法,其中包括設(shè)計(jì)輸入、綜合、功能仿真、實(shí)現(xiàn)、時(shí)序仿真、配

2010-05-25 17:56:59 670

670

給出了一種小數(shù)分頻技術(shù)的實(shí)現(xiàn)方法, 并在實(shí)驗(yàn)的基礎(chǔ)上進(jìn)一步證實(shí)了小數(shù)分頻的可行性該法通過(guò)微機(jī)控制,

2011-02-22 14:58:54 45

45 為了對(duì)運(yùn)動(dòng)控制系統(tǒng)中的脈沖進(jìn)行精確控制以減少累計(jì)誤差,需要對(duì)脈沖進(jìn)行分、倍頻和合成處理。介紹了通用的各種形式分頻器的實(shí)現(xiàn)方法,給出了在Altera公司的Cyclone II系列EP2C8Q208C8型

2011-06-13 16:53:56 66

66 分析了應(yīng)用于倍頻電路的預(yù)置可逆分頻器的工作原理,推導(dǎo)了觸發(fā)器的驅(qū)動(dòng)函數(shù)。并建立了基于simulink 和FPGA 的分頻器模型,實(shí)驗(yàn)結(jié)果表明分頻器可以實(shí)現(xiàn)預(yù)置模和可逆分頻功能,滿(mǎn)足倍

2011-08-17 16:50:45 1896

1896

為了對(duì)運(yùn)動(dòng)控制系統(tǒng)中的脈沖進(jìn)行精確控制以減少累計(jì)誤差,需要對(duì)脈沖進(jìn)行分、倍頻和合成處理。介紹了通用的各種形式分頻器的實(shí)現(xiàn)方法,給出了在Altera公司的CyclONe II系列EP2C8Q208C8型

2011-10-21 17:55:34 32

32 本文給出了分頻技術(shù)通用模型。并結(jié)合最新的一些分頻技術(shù),提出了一種基于FPGA全新的分頻系統(tǒng)的設(shè)計(jì)方法,簡(jiǎn)單的介紹了設(shè)計(jì)的思路、原理及其算法,并對(duì)該方案的性能進(jìn)行了分析,

2011-11-08 18:03:32 137

137 提出了一種基于FPGA的小數(shù)分頻實(shí)現(xiàn)方法,介紹了現(xiàn)有分頻方法的局限性,提出一種新的基于兩級(jí)計(jì)數(shù)器的分頻實(shí)現(xiàn)方法,給出了該設(shè)計(jì)方法的設(shè)計(jì)原理以及實(shí)現(xiàn)框圖

2011-11-09 09:36:22 121

121 給出了一種基于FPGA的分頻電路的設(shè)計(jì)方法.根據(jù)FPGA器件的特點(diǎn)和應(yīng)用范圍,提出了基于Verilog的分頻方法.該方法時(shí)于在FPGA硬件平臺(tái)上設(shè)計(jì)常用的任意偶數(shù)分頻、奇數(shù)分頻、半整數(shù)分頻

2011-11-09 09:49:33 355

355 介紹了一種基于FPGA的雙模前置小數(shù)分頻器的分頻原理及電路設(shè)計(jì),并用VHDL編程實(shí)現(xiàn)分頻器的仿真.

2011-11-29 16:43:06 48

48 本書(shū)比較全面地闡述了fpga在數(shù)字信號(hào)處理中的應(yīng)用問(wèn)題。本書(shū)共分8章,主要內(nèi)容包括典型fpga器件的介紹、vhdl硬件描述語(yǔ)言、fpga設(shè)計(jì)中常用軟件簡(jiǎn)介、用fpga實(shí)現(xiàn)數(shù)字信號(hào)處理的數(shù)據(jù)規(guī)劃、多種

2015-12-23 11:07:46 44

44 用 Verilog實(shí)現(xiàn)基于FPGA 的通用分頻器的設(shè)計(jì)時(shí)鐘分頻包括奇數(shù)和偶數(shù)分頻

2016-07-14 11:32:47 45

45 最近正在準(zhǔn)備找工作,由于是做FPGA開(kāi)發(fā),所以verilog實(shí)現(xiàn)技術(shù)分頻電路是一道經(jīng)常出現(xiàn)的題目,三分頻,五分頻電路等等;經(jīng)過(guò)一下午時(shí)間總結(jié)出了一個(gè)通用電路,可以實(shí)現(xiàn)任意奇數(shù)分頻電路。

2017-02-09 14:21:08 2571

2571 分頻器是FPGA設(shè)計(jì)中使用頻率非常高的基本設(shè)計(jì)之一,盡管在目前大部分設(shè)計(jì)中,廣泛使用芯片廠家集成的鎖相環(huán)資源,如賽靈思(Xilinx)的DLL.來(lái)進(jìn)行時(shí)鐘的分頻,倍頻以及相移。

2017-02-11 12:33:40 10916

10916 分頻器是FPGA設(shè)計(jì)中使用頻率非常高的基本設(shè)計(jì)之一,盡管在目前大部分設(shè)計(jì)中,廣泛使用芯片廠家集成的鎖相環(huán)資源,如賽靈思(Xilinx)的DLL.來(lái)進(jìn)行時(shí)鐘的分頻,倍頻以及相移。

2017-02-11 13:36:36 12409

12409

受外部周期信號(hào)激勵(lì)的震蕩,其頻率恰為激勵(lì)信號(hào)頻率的純分?jǐn)?shù),都叫做分頻。實(shí)現(xiàn)分頻的電路或裝置稱(chēng)為“分頻器”。(純分?jǐn)?shù):只有分?jǐn)?shù)部分,即小于1的分?jǐn)?shù),如3/4就是,而一又五分之四(1+4/5)就不是。)

2017-11-02 10:53:02 35807

35807 分頻器分為主動(dòng)式、被動(dòng)式、脈沖分頻器三種。主動(dòng)式電子分音器的原理就是要把適當(dāng)頻率訊號(hào)傳給適當(dāng)?shù)膯误w,被動(dòng)式分音器“功能、用途”是介于擴(kuò)大器與喇叭之間,由于單一喇叭無(wú)法達(dá)到“全頻段響應(yīng)”,脈沖分頻器利用漢穩(wěn)態(tài)電路的計(jì)數(shù)功能實(shí)現(xiàn)分頻的電路,又稱(chēng)為數(shù)字分頻器。

2018-01-10 15:36:20 10795

10795 DIP(DualIn-linePackage),即雙列直插式封裝,絕大多數(shù)中小規(guī)模集成電路均采用這種封裝形式,其引腳數(shù)一般不超過(guò)100個(gè)。DIP封裝的芯片有兩排引腳,分布于兩側(cè),且成直線平行布置

2018-06-14 14:40:00 2603

2603 液晶顯示器IC的封裝有多種形式,主要有DIP、SOP、SOJ、QFP(PQFP、TQFP)、PLCC和BGA封裝等

2018-06-17 09:25:00 3594

3594 設(shè)計(jì)背景: 分頻在 fpga的設(shè)計(jì)中一直都擔(dān)任著很重要的角色,而說(shuō)到分頻,我相信很多人都已經(jīng)想到了利用計(jì)算器來(lái)計(jì)算達(dá)到想要的時(shí)鐘頻率,但問(wèn)題是僅僅利用計(jì)數(shù)器來(lái)分頻,只可以實(shí)現(xiàn)偶數(shù)分頻,而如果我需要

2018-06-13 11:21:48 12390

12390

分頻器是FPGA設(shè)計(jì)中使用頻率非常高的基本單元之一。盡管目前在大部分設(shè)計(jì)中還廣泛使用集成鎖相環(huán)(如altera的PLL,Xilinx的DLL)來(lái)進(jìn)行時(shí)鐘的分頻、倍頻以及相移設(shè)計(jì),但是,對(duì)于時(shí)鐘要求

2019-08-07 08:00:00 9033

9033

VaaS形式化驗(yàn)證平臺(tái),采用了多種形式化驗(yàn)證方法,具有驗(yàn)證效率高、自動(dòng)化程度高、人工參與度低、易于使用、支持多個(gè)合約開(kāi)發(fā)語(yǔ)言、可支持大容量區(qū)塊鏈底層平臺(tái)的形式化驗(yàn)證等優(yōu)點(diǎn)。

2018-12-14 10:18:25 961

961 偶數(shù)倍分頻器的實(shí)現(xiàn)非常簡(jiǎn)單,只需要一個(gè)計(jì)數(shù)器進(jìn)行計(jì)數(shù)就能實(shí)現(xiàn)。如需要N分頻器(N為偶數(shù)),就可以由待分頻的時(shí)鐘觸發(fā)計(jì)數(shù)器進(jìn)行計(jì)數(shù),當(dāng)計(jì)數(shù)器從0計(jì)數(shù)到N/2-1時(shí),將輸出時(shí)鐘進(jìn)行翻轉(zhuǎn),并給計(jì)數(shù)器一個(gè)復(fù)位信號(hào),以使下一個(gè)時(shí)鐘開(kāi)始從零計(jì)數(shù)。

2019-02-01 01:49:00 1029

1029

論文分析了雙模前置小數(shù)分頻器的分頻原理和電路實(shí)現(xiàn)。結(jié)合脈沖刪除技術(shù),提出了一種適于硬件電路實(shí)現(xiàn)的任意小數(shù)分頻的設(shè)計(jì)方案 ,用 VerilogHDL語(yǔ) 言編程 ,在 QuartusII下對(duì) 此方案進(jìn) 行 了仿 真 ,并用 Cyclone 系 列 的 EP1C12Q240C8芯 片來(lái) 實(shí) 現(xiàn) 。

2019-08-02 08:00:00 5

5 基于提升框架的小波變換方法,利用FPGA 可編程特性可實(shí)現(xiàn)多種小波變換。提升框架(LS :Lifting Scheme) 是由Sweldens 等人在近幾年提出的一種小波變換方法,用它的框架結(jié)構(gòu)能有效地計(jì)算DWT。對(duì)于較長(zhǎng)的濾波器,LS 的操作次數(shù)比濾波器組的操作方式減少將近一半,更適合硬件實(shí)現(xiàn)。

2019-08-18 09:47:57 1918

1918

基于提升框架的小波變換方法,利用FPGA 可編程特性可實(shí)現(xiàn)多種小波變換。提升框架(LS :Lifting Scheme) 是由Sweldens 等人在近幾年提出的一種小波變換方法,用它的框架結(jié)構(gòu)能有

2019-08-25 11:01:31 5747

5747

從分頻方式看可以分為兩種,一種是主動(dòng)分頻(PassiveCrossover),或者叫電子分頻,也可以叫外置分頻、有源分頻;另一種是被動(dòng)分頻 (ActiveCrossover),或者叫功率分頻,也可以叫內(nèi)置分頻、無(wú)源分頻。

2019-10-08 10:37:42 11681

11681

在數(shù)字系統(tǒng)設(shè)計(jì)中,根據(jù)不同的設(shè)計(jì)需要,經(jīng)常會(huì)遇到偶數(shù)分頻、奇數(shù)分頻、半整數(shù)分頻等,有的還要求等占空比。在基于cpld(復(fù)雜可編程邏輯器件)的數(shù)字系統(tǒng)設(shè)計(jì)中,很容易實(shí)現(xiàn)由計(jì)數(shù)器或其級(jí)聯(lián)構(gòu)成各種形式的偶數(shù)分頻及非等占空比的奇數(shù)分頻,但對(duì)等占空比的奇數(shù)分頻及半整數(shù)分頻的實(shí)現(xiàn)較為困難。

2020-06-26 09:36:00 825

825

通常情況下,時(shí)鐘的分頻在FPGA設(shè)計(jì)中占有重要的地位,在此就簡(jiǎn)單列出分頻電路設(shè)計(jì)的思考思路。

2020-07-10 17:18:03 2192

2192 據(jù)介紹,北京京劇院除在園博園陽(yáng)光劇場(chǎng)上演《四郎探母》《龍鳳呈祥》外,將對(duì)北京園實(shí)施整體打造,采用沉浸式演出、戲劇體驗(yàn)活動(dòng)、展覽等多種形式向觀眾展示京劇藝術(shù)魅力。

2020-10-25 09:53:11 1449

1449 的設(shè)計(jì)來(lái)例系統(tǒng)地介紹了利用多種EDA工具進(jìn)行 FPGA協(xié)同設(shè)計(jì)的實(shí)現(xiàn)原理及方法近年來(lái),隨著微電子學(xué)的迅速發(fā)展以及SoC(System on Chip ,片上系統(tǒng)) 技術(shù)在設(shè)計(jì)領(lǐng)域引起的深刻變革,EDA(Electornic Design Automatic ,電子設(shè)計(jì)自動(dòng)化) 工具在系統(tǒng)設(shè)計(jì)中的地位愈發(fā)重要

2020-11-27 17:57:34 29

29 因?yàn)榕紨?shù)分頻器過(guò)于簡(jiǎn)單,所以我們從奇數(shù)分頻器開(kāi)始說(shuō)起8 01 奇數(shù)分頻器 ? ? 假設(shè)我們要實(shí)現(xiàn)一個(gè)2N+1分頻的分頻器,就需要高電平占N+0.5個(gè)周期,低電平占N+0.5個(gè)周期,這樣進(jìn)行處理的最小

2021-03-12 15:44:54 5614

5614

簡(jiǎn)要介紹了CPLD/FPGA器件的特點(diǎn)和應(yīng)用范圍,并以分頻比為2.5和1.5的分頻器的設(shè)計(jì)為例,介紹了在MaxPlusII開(kāi)發(fā)軟件下,利用VHDL硬件描述語(yǔ)言以及原理圖的輸入方式來(lái)設(shè)計(jì)數(shù)字邏輯電路的過(guò)程和方法。該設(shè)計(jì)具有結(jié)構(gòu)簡(jiǎn)單、實(shí)現(xiàn)方便、便于系統(tǒng)升級(jí)的特點(diǎn)。

2021-03-16 09:45:53 10

10 程序實(shí)現(xiàn)對(duì)輸入時(shí)鐘信號(hào)的7分頻介紹。

2021-03-17 14:59:23 11

11 簡(jiǎn)要介紹了 CPLD/FPGA器件的特點(diǎn)和應(yīng)用范圍,并以分頻比為2.5和15的分頻器的設(shè)計(jì)為例,介紹了在 Maxplusll開(kāi)發(fā)軟件下,利用ⅤHDL硬件描述語(yǔ)言以及原理圖的輸入方式來(lái)設(shè)計(jì)數(shù)字邏輯電路的過(guò)程和方法。該設(shè)計(jì)具有結(jié)構(gòu)簡(jiǎn)單、實(shí)現(xiàn)方便、便于系統(tǒng)升級(jí)的特點(diǎn)。

2021-03-22 16:52:15 5

5 一種基于FPGA的分頻器的實(shí)現(xiàn)說(shuō)明。

2021-05-25 16:57:08 16

16 基于CPLD/FPGA的半整數(shù)分頻器設(shè)計(jì)方案

2021-06-17 09:37:02 21

21 偶數(shù)倍分頻器的實(shí)現(xiàn)非常簡(jiǎn)單,只需要一個(gè)計(jì)數(shù)器進(jìn)行計(jì)數(shù)就能實(shí)現(xiàn)。如需要N分頻器(N為偶數(shù)),就可以由待分頻的時(shí)鐘觸發(fā)計(jì)數(shù)器進(jìn)行計(jì)數(shù),當(dāng)計(jì)數(shù)器從0計(jì)數(shù)到N/2-1時(shí),將輸出時(shí)鐘進(jìn)行翻轉(zhuǎn),并給計(jì)數(shù)器一個(gè)復(fù)位信號(hào),以使下一個(gè)時(shí)鐘開(kāi)始從零計(jì)數(shù)。

2022-11-21 09:41:24 751

751 FPGA分頻器是一種常用于數(shù)字信號(hào)處理、通信系統(tǒng)、雷達(dá)系統(tǒng)等領(lǐng)域的電路,其作用是將信號(hào)分成多個(gè)頻段。

2023-05-22 14:29:44 1032

1032

對(duì)于要求相位以及占空比嚴(yán)格的小數(shù)分頻,建議采用模擬電路實(shí)現(xiàn)。而使用數(shù)字電路實(shí)現(xiàn)只能保證盡量均勻,在長(zhǎng)時(shí)間內(nèi)進(jìn)行分頻。

2023-06-05 17:20:51 969

969

基于FPGA的高頻時(shí)鐘的分頻和分頻設(shè)計(jì)

2023-08-16 11:42:47 0

0 如何具體實(shí)現(xiàn)輸出信號(hào)的分頻和倍頻? 在現(xiàn)代電子系統(tǒng)中,信號(hào)分頻和倍頻是非常常見(jiàn)的技術(shù)。它們可以幫助電子設(shè)備在處理信號(hào)時(shí)具有更高的精度和準(zhǔn)確性。下面我將詳細(xì)介紹如何實(shí)現(xiàn)輸出信號(hào)的分頻和倍頻。 一、分頻

2023-10-31 10:33:21 1270

1270 分頻器設(shè)計(jì) 一:分頻器概念 板載時(shí)鐘往往 是 有限個(gè)( 50MHZ/100MHZ/24MHZ/60MHZ… ),如果在設(shè)計(jì)中需要其他時(shí)鐘時(shí),板載時(shí)鐘不滿(mǎn)足時(shí),需要對(duì)板載時(shí)鐘進(jìn)行分頻 / 倍頻,目的

2023-11-03 15:55:02 471

471

其實(shí)這個(gè)分頻時(shí)鐘切換很簡(jiǎn)單,根本不需要額外的切換電路。一個(gè)共用的計(jì)數(shù)器,加一點(diǎn)控制邏輯,就可以了,而且可以實(shí)現(xiàn)2到16任意整數(shù)分頻率之間的無(wú)縫切換。

2023-12-14 15:28:56 257

257

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論